# Formalizing the Concurrency Semantics of an LLVM Fragment

Soham Chakraborty, Viktor Vafeiadis

Max Planck Institute for Software Systems (MPI-SWS)

EuroLLVM 2017

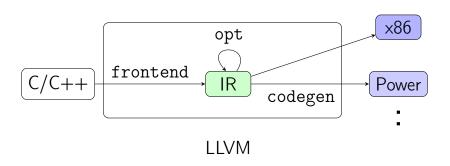

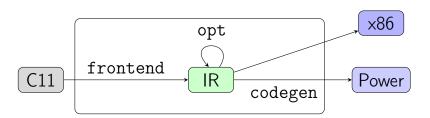

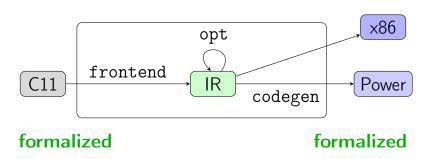

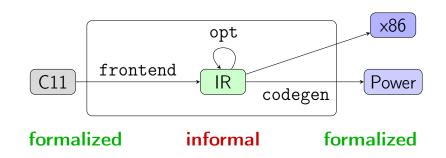

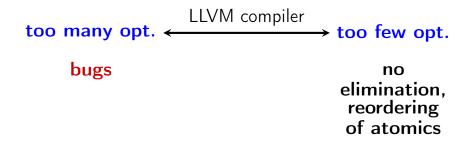

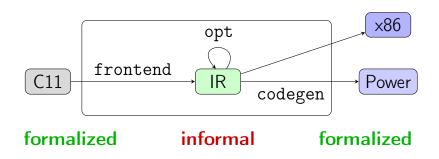

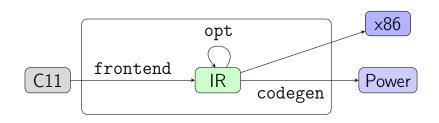

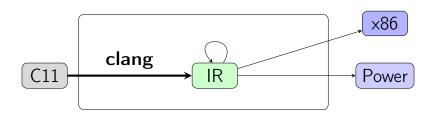

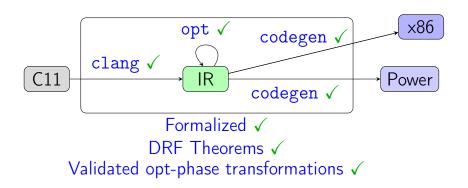

# LLVM Compilation

# LLVM Concurrency Compilation

# LLVM Concurrency Compilation

# LLVM Concurrency Compilation

Correctness of the transformations is unclear

# Limitation of LLVM Informal Concurrency

Valid opt is removed by over-restriction in bug fix

Formalized fragment of LLVM concurrency

Verified correctness of transformations

Validated LLVM opt-phase transformations

# Informal LLVM Concurrency

Informal text in Language Reference Manual

Frequent references to C11 concurrency

- "This model is inspired by the C++0x memory model."

- "These semantics are borrowed from Java and C++0x, but are somewhat more colloquial."

- This is intended to match shared variables in C/C++ ..."

- . . .

## Subtle differences

- A program has write-read race on non-atomics

- C11: the behavior of the program is undefined

- LLVM: defined behavior;racy read returns undef(u)

## Subtle differences

- A program has write-read race on non-atomics

- C11: the behavior of the program is *undefined*

- LLVM: defined behavior;racy read returns undef(u)

$$X = 1;$$

if  $(X)$

$t = 4;$  else

$t = 4;$

## Subtle differences

- A program has write-read race on non-atomics

- C11: the behavior of the program is *undefined*

- LLVM: defined behavior;racy read returns undef(u)

$$X = 1;$$

if  $(X)$

$t = 4;$  else

$t = 4;$

## Subtle differences

- A program has write-read race on non-atomics

- C11: the behavior of the program is *undefined*

- LLVM: defined behavior;racy read returns undef(u)

$$X=1; \ \left| egin{array}{l} {\sf if}(X) \ t=4; \ {\sf else} \ t=4; \end{array} \right|$$

$$t \neq 4$$

?

#### Subtle differences

- A program has write-read race on non-atomics

- C11: the behavior of the program is undefined

- LLVM: defined behavior;racy read returns undef(u)

$$X=1; \ \left\| egin{array}{l} \mathsf{if}(X) \ t=4; \ \mathsf{else} \ t=4; \end{array} \right\|$$

$$t \neq 4$$

? C11  $\checkmark$

## Subtle differences

- A program has write-read race on non-atomics

- C11: the behavior of the program is undefined

- LLVM: defined behavior;racy read returns undef(u)

$$X=1; \ \left| egin{array}{l} {\sf if}(X) \ t=4; \ {\sf else} \ t=4; \end{array} \right|$$

$$t \neq 4$$

? C11  $\checkmark$  LLVM  $x$

## Subtle differences

- A program has write-read race on non-atomics

- C11: the behavior of the program is undefined

- LLVM: defined behavior;racy read returns undef(u)

$$X=1; \ \left| egin{array}{l} {\sf if}(X) \ t=4; \ {\sf else} \ t=4; \end{array} \right|$$

$$t \neq 4$$

? C11  $\checkmark$  LLVM  $X$

- Set of allowed optimizations are different

#### C11 vs LLVM

```

Context: if (flag) { t = X; if (flag) { a = X; \Rightarrow } a = t; } \Rightarrow C11 X LLVM \checkmark

```

## C11 vs LLVM

```

t = X;

Context: if (flag) { x = 1; \parallel  }

Context:

if(flag){

a=t;

LLVM 🗸

C11 X

```

LLVM X

Context:

$t_1 = X$ ;  $egin{aligned} X = 4; \ Y_{\mathsf{rel}} = 1; \ \end{pmatrix} \quad & \begin{array}{c} \mathsf{if}(Y_{\mathsf{acq}}) \{ \ t_2 = X; \ \} \end{array}$   $t_1 = X$ ;  $if(Y_{acq})$  $t_2 = t_1$ ;

## Formalization

## Formalization of LLVM concurrency

Verified correctness of transformations

Validated LLVM opt-phase transformations

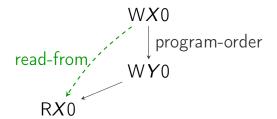

## Example

int

$$X = 0$$

,  $Y = 0$ ;

$a = X$ ;  $\begin{vmatrix} b = Y \\ Y = 1 \end{vmatrix}$ ;  $X = 1$ ;

Is  $a == b == 1$  possible?

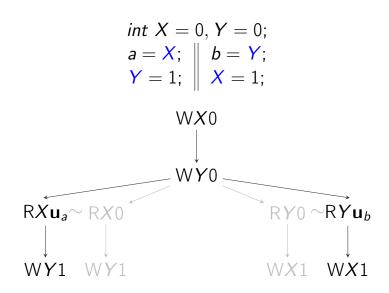

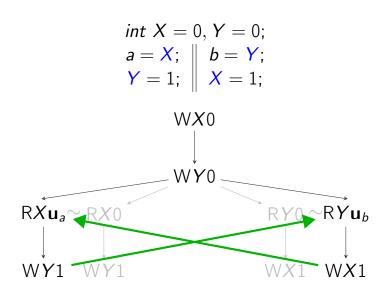

# Example

int

$$X = 0$$

,  $Y = 0$ ;

$a = X$ ;  $|| b = Y$ ;

$Y = 1$ ;  $|| X = 1$ ;

Is  $a == b == 1$  possible?  $\checkmark$

int

$$X = 0$$

,  $Y = 0$ ; int  $X = 0$ ,  $Y = 0$ ;  $A = X$ ;  $A$

int

$$X = 0, Y = 0$$

;

$a = X$ ;  $b = Y$ ;

$Y = 1$ ;  $X = 1$ ;

$X = 1$ ;

$X = 1$ ;

$X = 1$ ;

int

$$X = 0, Y = 0;$$

$a = X;$   $b = Y;$

$Y = 1;$   $X = 1;$

int

$$X = 0, Y = 0;$$

$a = X;$   $b = Y;$

$Y = 1;$   $X = 1;$

int

$$X = 0, Y = 0;$$

$a = X;$   $b = Y;$

$Y = 1;$   $X = 1;$

int

$$X = 0, Y = 0;$$

$a = X;$   $b = Y;$

$Y = 1;$   $X = 1;$

int

$$X = 0, Y = 0;$$

$a = X;$   $b = Y;$

$Y = 1;$   $X = 1;$

int

$$X = 0, Y = 0;$$

$a = X;$   $b = Y;$

$Y = 1;$   $X = 1;$

int

$$X = 0, Y = 0;$$

$a = X;$   $b = Y;$

$Y = 1;$   $X = 1;$

# Example

int

$$X = 0$$

,  $Y = 0$ ;

$a = X$ ;  $|| b = Y$ ;

$Y = 1$ ;  $|| X = 1$ ;

Is  $a == b == 1$  possible?  $\checkmark$

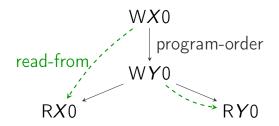

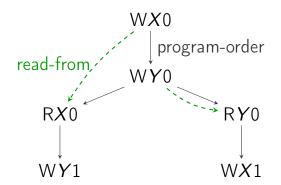

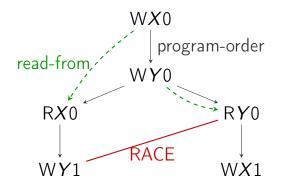

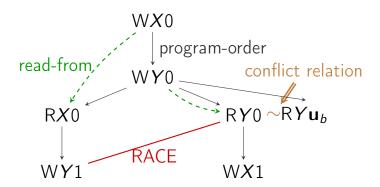

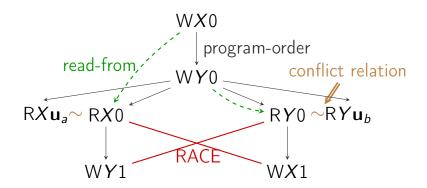

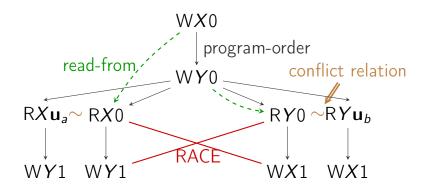

#### **Execution from Event Structure**

## Execution from Event Structure

$$int X = 0, Y = 0;$$

$$a = X; \quad | \quad b = Y;$$

$$Y = 1; \quad | \quad X = 1;$$

$$WX0$$

$$WY0$$

$$RXu_a = RX0$$

$$WY1$$

$$WY1$$

$$WY1$$

$$WY1$$

$$WX1$$

$$WX1$$

$$WX1$$

$$WX1$$

$$WX1$$

# Proposed Formalization Handles

- Memory operations:

- load

- store

- compare\_and\_swap (CAS)

- Memory orders:

- non-atomic (na)

- acquire (acq)

- release (rel)

- acquire\_release (acq\_rel)

- sequentially consistent (sc)

# Verifying Transformations

Formalized fragment of LLVM concurrency

## Verified correctness of transformations

- Elimination

- Reordering

- Mappings (C11 → LLVM → X86/Power)

Validated LLVM opt-phase transformations

## Transformation Correctness

Behavior $(P_{tgt}) \subseteq \text{Behavior}(P_{src})$ Behavior: final values observed in each location

#### Transformation Correctness

Behavior $(P_{tgt}) \subseteq \text{Behavior}(P_{src})$ Behavior: final values observed in each location

$\mathsf{Behavior}(G_{tgt}) \subseteq \mathsf{Behavior}(G_{src})$

#### Elimination Optimizations

Adjacent read after read/write elimination

•

$$a = X_o$$

;  $b = X_{na}$ ;  $\rightsquigarrow a = X_o$ ;  $b = a$ ;

•

$$X_o = v$$

;  $b = X_{na}$ ;  $\rightsquigarrow X_o = v$ ;  $b = v$ ;

Adjacent overwritten write elimination

•

$$X_{na} = v'; X_{na} = v; \rightsquigarrow X_{na} = v;$$

Non-adjacent overwritten write elimination

•

$$X_{na} = v'$$

; C;  $X_{na} = v$ ;  $\sim$  C;  $X_{na} = v$ ; where rel-acq-pair  $\notin$  C and  $access(X) \notin C$

#### LLVM performs these eliminations

#### Elimination Optimizations

Adjacent read after read/write elimination

•

$$a = X_o$$

;  $b = X_{na}$ ;  $\rightsquigarrow a = X_o$ ;  $b = a$ ;

•

$$X_o = v$$

;  $b = X_{na}$ ;  $\rightarrow X_o = v$ ;  $b = x_{na}$

Adjacent overwritten write

•

$$X_{na} = v'; X_{na} = v'$$

•

$$X_{\text{na}} = v; \rightarrow C; X_{\text{na}} = v;$$

$\text{acq-pair} \notin C \text{ and } access(X) \notin C$

LLVM performs these eliminations

#### Also Proved...

Adjacent read after read/write elimination

•

$$a = X_{acq}$$

;  $b = X_{acq}$ ;  $\rightarrow a = X_{acq}$ ;  $b = a$ ;

•

$$a = X_{sc}$$

;  $b = X_{(acq|sc)}$ ;  $\rightarrow a = X_{sc}$ ;  $b = a$ ;

•

$$X_{\text{rel}} = v$$

;  $b = X_{\text{acq}}$ ;  $\rightsquigarrow X_{\text{rel}} = v$ ;  $b = v$ ;

•

$$X_{sc} = v$$

;  $b = X_{(acq|sc)}$ ;  $\rightsquigarrow X_{sc} = v$ ;  $b = v$ ;

Adjacent overwritten write elimination

•

$$X_{\text{rel}} = v'$$

;  $X_{\text{rel}} = v$ ;  $\sim X_{\text{rel}} = v$ ;

•

$$X_{(\text{rel}|\text{sc})} = v'; X_{\text{sc}} = v; \rightsquigarrow X_{\text{sc}} = v;$$

#### LLVM does NOT perform these eliminations

#### Also Proved...

Adjacent read after read/write elimination

•

$$a = X_{\text{acq}}$$

;  $b = X_{\text{acq}}$ ;  $\rightarrow a = X_{\text{acq}}$ ;  $b = a$ ;

•

$$a = X_{sc}$$

;  $b = X_{(acq|sc)}$ ;  $\rightarrow a = X_{sc}$ ;  $b = a$ ;

•

$$X_{\text{rel}} = v$$

;  $b = X_{\text{acq}}$ ;  $\rightsquigarrow X_{\text{rel}} = v$ ;  $b = v$ ;

•

$$X_{sc} = v$$

;  $b = X_{(acq|sc)}$ ;  $\rightsquigarrow X_{sc} = v$ ;  $b = v$ ;

Adjacent overwritten write elimination

•

$$X_{\text{rel}} = v'; X_{\text{rel}} = v; \rightsquigarrow X_{\text{rel}} = v;$$

•

$$X_{(\text{rel}|\text{sc})} = v'; X_{\text{sc}} = v; \rightsquigarrow X_{\text{sc}} = v;$$

#### LLVM does NOT perform these eliminations

Non-adjacent read after write elimination

•

$$X_{na} = v$$

; C;  $a = X_{na}$ ;  $\rightsquigarrow X_{na} = v$ ; C;  $a = v$ ; where rel-acq-pair  $\notin$  C and  $access(X) \notin C$

#### Also Proved...

#### Adjacent read after read/write elimination

•

$$a = X_{\text{acq}}$$

;  $b = X_{\text{acq}}$ ;  $\rightarrow a = X_{\text{acq}}$ ;  $b = a$ ;

•

$$a = X_{sc}$$

;  $b = X_{(acq|sc)}$ ;  $\rightarrow a = X_{sc}$ ;  $b = a$ ;

•

$$X_{\text{rel}} = v$$

;  $b = X_{\text{acq}}$ ;  $\rightarrow X_{\text{rel}} = v$ ;  $b = v$

•

$$X_{sc} = v$$

;  $b = X_{(acq|sc)}$ ;  $\rightarrow X_{sc} = v$

## Adjacent overwritten write elim

•

$$X_{\text{rel}} = v'; X_{\text{rel}} = v; \sim$$

$$\bullet \ X_{(rel|sc)} = v'; X_{\bullet}$$

# LLVM dor Perform these eliminations

## Non read after write elimination

where rel-acq-pair  $\notin$  C and  $access(X) \notin$  C

#### Verifying Transformations

Formalized fragment of LLVM concurrency

#### Verified correctness of transformations

- Elimination

- Reordering  $(a; b \rightsquigarrow b; a)$

- Mappings (C11 → LLVM → X86/Power)

Validated LLVM opt-phase transformations

#### LLVM Reorderings

$a; b \rightsquigarrow b; a$

| $\downarrow a \setminus b \rightarrow$ | (St Ld) <sub>na</sub> | $St_{rel}$ | Ld <sub>acq</sub> | $Ld_{sc}$    | $U_{(acq\_rel sc)}$ |

|----------------------------------------|-----------------------|------------|-------------------|--------------|---------------------|

| (St Ld) <sub>na</sub>                  | $\checkmark$          | _          | $\checkmark$      | $\checkmark$ | _                   |

| St <sub>rel</sub>                      | $\checkmark$          | _          | _                 | _            | -                   |

| St <sub>sc</sub>                       | ✓                     | -          | -                 | -            | -                   |

| Ld <sub>acq</sub>                      | -                     | -          | -                 | -            | -                   |

| $U_{(acq\_rel sc)}$                    | -                     | -          | -                 | -            | -                   |

$$X_{\text{rel}} = v$$

;  $Y_{\text{na}} = v'$ ;  $V_{\text{na}} = v'$ ;  $V_{\text{rel}} = v$ ;  $V_{\text{rel}} = v'$

## LLVM performs(√) these reorderings

#### LLVM Reorderings

$a; b \rightsquigarrow b; a$

| $\downarrow a \setminus b \rightarrow$ | (St Ld) <sub>na</sub> | $St_{rel}$ | $Ld_{acq}$ | $Ld_{sc}$ | $U_{(acq_rel sc)}$ |

|----------------------------------------|-----------------------|------------|------------|-----------|--------------------|

| (St Ld) <sub>na</sub>                  | ✓                     | ×          | <b>√</b>   | <b>√</b>  | ×                  |

| St <sub>rel</sub>                      | ✓                     | ×          | -          | -         | ×                  |

| St <sub>sc</sub>                       | ✓                     | ×          | -          | ×         | ×                  |

| Ld <sub>acq</sub>                      | ×                     | ×          | ×          | ×         | ×                  |

| $U_{(acq\_rel sc)}$                    | ×                     | ×          | ×          | ×         | ×                  |

$$Y_{\mathsf{na}} = v'; X_{\mathsf{rel}} = v; \rightsquigarrow X_{\mathsf{rel}} = v; Y_{\mathsf{na}} = v'; \quad \times$$

## LLVM restricts(x) these reorderings

Also Analyzed...

$a; b \rightsquigarrow b; a$

| $\downarrow a \setminus b \rightarrow$ | (St Ld) <sub>na</sub> | $St_{rel}$ | Ld <sub>acq</sub> | Ld <sub>sc</sub> | $U_{(acq\_rel sc)}$ |

|----------------------------------------|-----------------------|------------|-------------------|------------------|---------------------|

| (St Ld) <sub>na</sub>                  | $\checkmark$          | ×          | $\checkmark$      | $\checkmark$     | ×                   |

| St <sub>rel</sub>                      | ✓                     | ×          | $\checkmark$      | $\checkmark$     | ×                   |

| St <sub>sc</sub>                       | ✓                     | ×          | ✓                 | ×                | ×                   |

| Ld <sub>acq</sub>                      | ×                     | ×          | ×                 | ×                | ×                   |

| $U_{(acq\_rel sc)}$                    | ×                     | ×          | ×                 | ×                | ×                   |

$$X_{\text{rel}} = v$$

;  $t = Y_{\text{acq}}$ ;  $\rightarrow t = Y_{\text{acq}}$ ;  $X_{\text{rel}} = v$ ;  $\checkmark$

#### LLVM does NOT perform these reorderings

#### Also Analyzed...

| $a; b \rightsquigarrow b; a$             |                       |            |       |           |

|------------------------------------------|-----------------------|------------|-------|-----------|

| $\downarrow$ $a \setminus b \rightarrow$ | (St Ld) <sub>na</sub> | $St_{rel}$ | Ldacq | y_rel sc) |

| (St Ld) <sub>na</sub>                    | ✓                     | ×          | 106   | ×         |

| $St_{rel}$                               | ✓                     | X          | 21    | ×         |

| $St_{sc}$                                | <b>✓</b> /            | ~ C        | X     | ×         |

$$t = Y_{\text{acq}}; \rightsquigarrow t = Y_{\text{acq}}; X_{\text{rel}} = v; \quad \checkmark$$

X

X

X

X

LLVM does NOT perform these reorderings

X

X

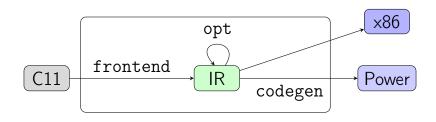

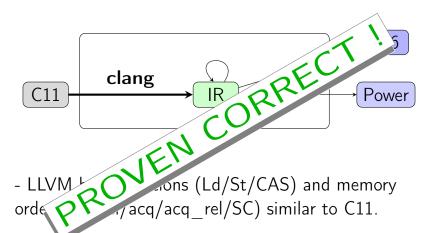

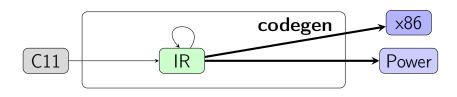

#### Verifying Transformations

Formalized fragment of LLVM concurrency

#### Verified correctness of transformations

- Elimination

- Reordering

- Mappings (C11 → LLVM → X86/Power)

Validated LLVM opt-phase transformations

#### C11 to LLVM Mapping Correctness

- LLVM has operations (Ld/St/CAS) and memory orders (na/rel/acq/acq\_rel/SC) similar to C11.

- LLVM model is stronger than C11.

#### C11 to LLVM Mapping Correctness

- LLVM model is stronger than C11.

#### LLVM to Architecture Mapping Correctness

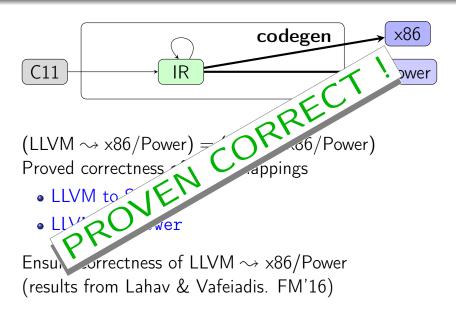

(LLVM  $\rightsquigarrow$  x86/Power) = (C11  $\rightsquigarrow$  x86/Power) Proved correctness of these mappings

- LLVM to SC

- LLVM to SPower

Ensure correctness of LLVM → x86/Power (results from Lahav & Vafeiadis. FM'16)

#### LLVM to Architecture Mapping Correctness

#### Validation

Formalized fragment of LLVM concurrency

Proved correctness of transformations

Validated LLVM opt-phase transformations

•  $P_{src} \xrightarrow{\text{LLVM}} P_{tgt}$  ? Correct : Potential Error

#### LLVM Validation

$$P_{src} \xrightarrow{\text{LLVM}} P_{tgt}$$

? Correct : Potential Error

$$\uparrow \qquad \qquad \qquad \uparrow \qquad \qquad P_{src} \xrightarrow{(R \cup E)^*} P_{tgt}$$

? Correct : Potential Error

- R: Safe reorderings

- E: Safe eliminations

$$s_1 = X ! A$$

$s_2 = X ! B$

$V = 1 ! C$

$s_4 = Z_{acq} ! D$

$Y = 1 ! E$

$Y = 2 ! F$

$$s_1 = X ! A$$

$$s_2 = X ! B$$

$$V = 1 ! C$$

$$s_4 = Z_{acq} ! D$$

$$Y = 1 ! E$$

$$Y = 2 ! F$$

✓

$$s_1 = X !A$$

✗  $s_2 = X !B$

$V = 1 !C$

$s_4 = Z_{acq} !D$

$Y = 1 !E$

$Y = 2 !F$

✓  $s_1 = X !A$ X  $s_2 = X !B$ V = 1 !C

✓  $s_4 = Z_{acq} !D$

$Y = 1 \, !E$

Y=2!F

- $\checkmark s_1 = X ! A$

- $x s_2 = X ! B$

- $V = 1 \ | C$

- $\checkmark s_4 = Z_{acq} !D$

- Y=1 !E

- ✓ Y = 2 !F

- $\checkmark s_1 = X ! A$

- $x s_2 = X !B$

- $V = 1 \ | C$

- $\checkmark s_4 = Z_{acq} !D$

- X Y = 1 ! E

- ✓ Y = 2 !F

- $\checkmark s_1 = X ! A$

- $x s_2 = X !B$

- ✓ V = 1 ! C

- $\checkmark s_4 = Z_{acq} !D$

- X Y = 1 ! E

- ✓ Y = 2 ! F

$$\checkmark s_1 = X ! A$$

$$x s_2 = X \mid B$$

✓

$$V = 1 ! C$$

$$\checkmark s_4 = Z_{acq} ! D$$

$$X Y = 1 ! E$$

✓

$$Y = 2 !F$$

$$t_1 = X ! A$$

$$t_2 = Z_{\text{acg}} ! D$$

$$Y = 2 \, !F$$

✓

$$s_1 = X !A$$

X  $s_2 = X !B$

✓  $V = 1 !C$

✓  $t_2 = Z_{acq} !D$

✓  $t_3 = Z_{acq} !D$

Y  $t_4 = Z_{acq} !D$

Y  $t_5 = 2 !F$

X  $t_7 = 1 !E$

✓  $t_7 = 2 !F$

✓

$$s_1 = X ! A$$

X  $s_2 = X ! B$

✓  $V = 1 ! C$

✓  $t_2 = Z_{acq} ! D$

✓  $t_3 = Z_{acq} ! D$

Y  $t_4 = Z_{acq} ! D$

Y  $t_5 = 2 ! F$

X  $t_7 = 1 ! E$

✓  $t_7 = 2 ! F$

- Check that unmatched accesses are deletable

- Check that reorderings are allowed

✓

$$s_1 = X ! A$$

X  $s_2 = X ! B$

✓  $V = 1 ! C$

✓  $t_2 = Z_{acq} ! D$

✓  $t_3 = Z_{acq} ! D$

Y  $t_4 = Z_{acq} ! D$

Y  $t_5 = 2 ! E$

✓  $t_7 = 2 ! E$

✓  $t_7 = 2 ! E$

✓  $t_7 = 2 ! E$

Correct

- Check that unmatched accesses are deletable

- Check that reorderings are allowed

Formalized fragment of LLVM concurrency

Proved correctness of transformations

## Validated LLVM opt-phase transformations

- Generate a test case  $(P_{src})$ .

- Apply LLVM transformations  $(P_{tgt})$ .

- $P_{src} \xrightarrow{\text{LLVM}} P_{tgt}$  ? Correct : Potential Error

#### More Details

## LLVM Formalization [CGO'17]

- Event structure construction rules

- Consistency constraints

- Data race freedom (DRF) theorems

- Proofs: http://plv.mpi-sws.org/llvmcs/

## Translation validation [CGO'16]

- Programs with control flow

- Experimental evaluations

- Artifact: http://plv.mpi-sws.org/validc/

#### Summary

#### **Future Directions**

#### Extend the LLVM concurrency model

- With relaxed accesses and fences

- Verify more optimizations

- Mechanize the formalization

- Improve the validator

- Integrate with sequential transformations

- Handle loops, pointer etc

#### Thank You!