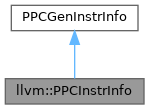

#include "Target/PowerPC/PPCInstrInfo.h"

Static Public Member Functions | |

| static bool | isSameClassPhysRegCopy (unsigned Opcode) |

| static bool | hasPCRelFlag (unsigned TF) |

| static bool | hasGOTFlag (unsigned TF) |

| static bool | hasTLSFlag (unsigned TF) |

| static int | getRecordFormOpcode (unsigned Opcode) |

Protected Member Functions | |

| MachineInstr * | commuteInstructionImpl (MachineInstr &MI, bool NewMI, unsigned OpIdx1, unsigned OpIdx2) const override |

| Commutes the operands in the given instruction. | |

Detailed Description

Definition at line 174 of file PPCInstrInfo.h.

Constructor & Destructor Documentation

◆ PPCInstrInfo()

|

explicit |

Definition at line 92 of file PPCInstrInfo.cpp.

Member Function Documentation

◆ analyzeBranch()

|

override |

Definition at line 1260 of file PPCInstrInfo.cpp.

References llvm::MachineBasicBlock::begin(), Cond, llvm::MachineOperand::CreateImm(), llvm::MachineOperand::CreateReg(), DisableCTRLoopAnal, llvm::MachineBasicBlock::end(), llvm::MachineBasicBlock::getLastNonDebugInstr(), llvm::MachineOperand::getMBB(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), I, llvm::MachineBasicBlock::isLayoutSuccessor(), llvm::MachineOperand::isMBB(), llvm::PPCSubtarget::isPPC64(), MBB, llvm::PPC::PRED_BIT_SET, llvm::PPC::PRED_BIT_UNSET, and TBB.

◆ analyzeCompare()

|

override |

◆ analyzeLoopForPipelining()

|

override |

Analyze loop L, which must be a single-basic-block loop, and if the conditions can be understood enough produce a PipelinerLoopInfo object.

Definition at line 5484 of file PPCInstrInfo.cpp.

References llvm::MachineBasicBlock::end(), findLoopInstr(), llvm::MachineBasicBlock::getFirstTerminator(), llvm::MachineBasicBlock::getParent(), llvm::MachineFunction::getRegInfo(), I, isBDNZ(), MRI, and llvm::MachineBasicBlock::pred_begin().

◆ areMemAccessesTriviallyDisjoint()

|

override |

Return true if two MIs access different memory addresses and false otherwise.

Definition at line 5542 of file PPCInstrInfo.cpp.

References assert(), getMemOperandWithOffsetWidth(), getRegisterInfo(), llvm::LocationSize::getValue(), llvm::MachineInstr::hasOrderedMemoryRef(), llvm::MachineInstr::hasUnmodeledSideEffects(), llvm::LocationSize::hasValue(), llvm::MachineOperand::isIdenticalTo(), llvm::MachineInstr::mayLoadOrStore(), and TRI.

◆ canInsertSelect()

|

override |

Definition at line 1520 of file PPCInstrInfo.cpp.

References Cond, llvm::MachineBasicBlock::getParent(), getReg(), llvm::MachineFunction::getRegInfo(), MBB, and MRI.

◆ ClobbersPredicate()

|

override |

Definition at line 2311 of file PPCInstrInfo.cpp.

References llvm::TargetRegisterClass::contains(), and MI.

◆ combineRLWINM()

| bool PPCInstrInfo::combineRLWINM | ( | MachineInstr & | MI, |

| MachineInstr ** | ToErase = nullptr |

||

| ) | const |

Definition at line 3795 of file PPCInstrInfo.cpp.

References assert(), llvm::dbgs(), llvm::MachineInstr::dump(), llvm::Pass::dump(), llvm::get(), llvm::APInt::getBitsSetWithWrap(), llvm::MachineOperand::getImm(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::APInt::getZExtValue(), llvm::MachineInstr::hasImplicitDef(), llvm::MachineOperand::isImm(), llvm::MachineOperand::isKill(), llvm::isRunOfOnes(), llvm::Register::isVirtual(), llvm::APInt::isZero(), LLVM_DEBUG, MI, MRI, llvm::APInt::rotl(), and llvm::MachineOperand::setIsKill().

◆ commuteInstructionImpl()

|

overrideprotected |

Commutes the operands in the given instruction.

The commutable operands are specified by their indices OpIdx1 and OpIdx2.

Do not call this method for a non-commutable instruction or for non-commutable pair of operand indices OpIdx1 and OpIdx2. Even though the instruction is commutable, the method may still fail to commute the operands, null pointer is returned in such cases.

For example, we can commute rlwimi instructions, but only if the rotate amt is zero. We also have to munge the immediates a bit.

Definition at line 1131 of file PPCInstrInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), assert(), llvm::BuildMI(), llvm::TargetInstrInfo::commuteInstructionImpl(), llvm::RegState::Define, llvm::getDeadRegState(), llvm::getKillRegState(), MI, and llvm::MCOI::TIED_TO.

◆ convertToImmediateForm()

| bool PPCInstrInfo::convertToImmediateForm | ( | MachineInstr & | MI, |

| SmallSet< Register, 4 > & | RegsToUpdate, | ||

| MachineInstr ** | KilledDef = nullptr |

||

| ) | const |

Definition at line 3733 of file PPCInstrInfo.cpp.

References assert(), DefMI, llvm::PPCRegisterInfo::getMappedIdxOpcForImmOpc(), llvm::MachineOperand::getReg(), llvm::MachineFunction::getRegInfo(), llvm::SmallSet< T, N, C >::insert(), instrHasImmForm(), llvm::MachineOperand::isDef(), llvm::MachineOperand::isReg(), llvm::PPC::isVFRegister(), MI, MRI, and llvm::MachineInstr::operands().

◆ copyPhysReg()

|

override |

Definition at line 1678 of file PPCInstrInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), assert(), llvm::BuildMI(), contains(), DL, llvm::PPCRegisterInfo::emitAccCopyInfo(), llvm::get(), getCRBitValue(), llvm::getCRFromCRBit(), llvm::getKillRegState(), llvm::MCInstrDesc::getNumOperands(), getRegisterInfo(), I, Idx, llvm::RegState::Kill, llvm_unreachable, MBB, TRI, and VSXSelfCopyCrash.

◆ CreateTargetHazardRecognizer()

|

override |

CreateTargetHazardRecognizer - Return the hazard recognizer to use for this target when scheduling the DAG.

Definition at line 101 of file PPCInstrInfo.cpp.

References llvm::TargetInstrInfo::CreateTargetHazardRecognizer(), llvm::PPC::DIR_440, llvm::PPC::DIR_A2, llvm::PPC::DIR_E500mc, and llvm::PPC::DIR_E5500.

◆ CreateTargetPostRAHazardRecognizer()

|

override |

CreateTargetPostRAHazardRecognizer - Return the postRA hazard recognizer to use for this target when scheduling the DAG.

Definition at line 118 of file PPCInstrInfo.cpp.

References assert(), llvm::PPC::DIR_440, llvm::PPC::DIR_A2, llvm::PPC::DIR_E500mc, llvm::PPC::DIR_E5500, llvm::PPC::DIR_PWR7, llvm::PPC::DIR_PWR8, llvm::MachineFunction::getSubtarget(), llvm::ScheduleDAG::MF, and llvm::ScheduleDAG::TII.

◆ decomposeMachineOperandsTargetFlags()

|

override |

Definition at line 2966 of file PPCInstrInfo.cpp.

◆ expandPostRAPseudo()

|

override |

Definition at line 3077 of file PPCInstrInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), assert(), llvm::BuildMI(), contains(), DL, expandPostRAPseudo(), expandVSXMemPseudo(), llvm::get(), llvm::PPCSubtarget::getTargetMachine(), llvm::PPCSubtarget::getTargetTriple(), isAnImmediateOperand(), llvm::PPCSubtarget::isLittleEndian(), llvm::Triple::isOSGlibc(), llvm::PPCSubtarget::isPPC64(), llvm::PPCSubtarget::isTargetLinux(), MBB, MI, llvm::Offset, llvm::PPC::PRED_NE_MINUS, and llvm::PPCTargetMachine::setGlibcHWCAPAccess().

Referenced by expandPostRAPseudo().

◆ expandVSXMemPseudo()

| bool PPCInstrInfo::expandVSXMemPseudo | ( | MachineInstr & | MI | ) | const |

Definition at line 3011 of file PPCInstrInfo.cpp.

References llvm::get(), llvm_unreachable, and MI.

Referenced by expandPostRAPseudo().

◆ finalizeInsInstrs()

|

override |

Fixup the placeholders we put in genAlternativeCodeSequence() for MachineCombiner.

Definition at line 526 of file PPCInstrInfo.cpp.

References assert(), llvm::CallingConv::C, llvm::APFloat::changeSign(), llvm::SmallVectorBase< Size_T >::empty(), FMAOpIdxInfo, getConstantFromConstantPool(), llvm::MachineFunction::getConstantPool(), llvm::MachineConstantPool::getConstantPoolIndex(), llvm::MachineFunction::getDataLayout(), llvm::MachineInstr::getMF(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::DataLayout::getPrefTypeAlign(), llvm::MachineOperand::getReg(), llvm::MachineFunction::getRegInfo(), getRegisterInfo(), Idx, InfoArrayIdxMULOpIdx, MRI, llvm::REASSOC_XY_BAC, llvm::REASSOC_XY_BCA, and TRI.

◆ findCommutedOpIndices()

|

override |

Definition at line 1215 of file PPCInstrInfo.cpp.

References llvm::TargetInstrInfo::findCommutedOpIndices(), llvm::PPC::getAltVSXFMAOpcode(), and MI.

◆ findLoopInstr()

| MachineInstr * PPCInstrInfo::findLoopInstr | ( | MachineBasicBlock & | PreHeader, |

| SmallPtrSet< MachineBasicBlock *, 8 > & | Visited | ||

| ) | const |

Find the hardware loop instruction used to set-up the specified loop.

On PPC, we have two instructions used to set-up the hardware loop (MTCTRloop, MTCTR8loop) with corresponding endloop (BDNZ, BDNZ8) instructions to indicate the end of a loop.

Definition at line 5504 of file PPCInstrInfo.cpp.

References I, llvm::MachineBasicBlock::instrs(), and llvm::PPCSubtarget::isPPC64().

Referenced by analyzeLoopForPipelining().

◆ foldFrameOffset()

| bool PPCInstrInfo::foldFrameOffset | ( | MachineInstr & | MI | ) | const |

Definition at line 3524 of file PPCInstrInfo.cpp.

References assert(), llvm::dbgs(), llvm::MachineInstr::dump(), llvm::Pass::dump(), End, llvm::MachineInstr::eraseFromParent(), llvm::get(), getDefMIPostRA(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineFunction::getRegInfo(), getRegisterInfo(), llvm::ImmInstrInfo::ImmOpNo, isADDInstrEligibleForFolding(), isImmInstrEligibleForFolding(), llvm::MachineOperand::isKill(), isValidToBeChangedReg(), LLVM_DEBUG, MI, MRI, llvm::ImmInstrInfo::OpNoForForwarding, llvm::MachineOperand::setImm(), and llvm::ImmInstrInfo::ZeroIsSpecialOrig.

◆ foldImmediate()

|

override |

Definition at line 2118 of file PPCInstrInfo.cpp.

References DefMI, MRI, onlyFoldImmediate(), and UseMI.

◆ genAlternativeCodeSequence()

|

override |

When getMachineCombinerPatterns() finds patterns, this function generates the instructions that could replace the original code sequence.

Definition at line 768 of file PPCInstrInfo.cpp.

References llvm::TargetInstrInfo::genAlternativeCodeSequence(), llvm::REASSOC_XMM_AMM_BMM, llvm::REASSOC_XY_AMM_BMM, llvm::REASSOC_XY_BAC, and llvm::REASSOC_XY_BCA.

◆ getCombinerObjective()

|

override |

Definition at line 740 of file PPCInstrInfo.cpp.

References llvm::TargetInstrInfo::getCombinerObjective(), llvm::MustReduceDepth, llvm::MustReduceRegisterPressure, llvm::REASSOC_XMM_AMM_BMM, llvm::REASSOC_XY_AMM_BMM, llvm::REASSOC_XY_BAC, and llvm::REASSOC_XY_BCA.

◆ getConstantFromConstantPool()

| const Constant * PPCInstrInfo::getConstantFromConstantPool | ( | MachineInstr * | I | ) | const |

Definition at line 720 of file PPCInstrInfo.cpp.

References assert(), DefMI, llvm::MachineFunction::getConstantPool(), llvm::MachineConstantPool::getConstants(), llvm::MachineFunction::getRegInfo(), I, MRI, and llvm::MachineInstr::uses().

Referenced by finalizeInsInstrs().

◆ getDefMIPostRA()

| MachineInstr * PPCInstrInfo::getDefMIPostRA | ( | unsigned | Reg, |

| MachineInstr & | MI, | ||

| bool & | SeenIntermediateUse | ||

| ) | const |

Definition at line 3336 of file PPCInstrInfo.cpp.

References assert(), getRegisterInfo(), MI, and TRI.

Referenced by foldFrameOffset(), isValidToBeChangedReg(), and optimizeCmpPostRA().

◆ getExtendResourceLenLimit()

|

inlineoverride |

On PowerPC, we try to reassociate FMA chain which will increase instruction size.

Set extension resource length limit to 1 for edge case. Resource Length is calculated by scaled resource usage in getCycles(). Because of the division in getCycles(), it returns different cycles due to legacy scaled resource usage. So new resource length may be same with legacy or 1 bigger than legacy. We need to execlude the 1 bigger case even the resource length is not perserved for more FMA chain reassociations on PowerPC.

Definition at line 411 of file PPCInstrInfo.h.

◆ getFMAPatterns()

| bool PPCInstrInfo::getFMAPatterns | ( | MachineInstr & | Root, |

| SmallVectorImpl< unsigned > & | Patterns, | ||

| bool | DoRegPressureReduce | ||

| ) | const |

Return true when there is potentially a faster code sequence for a fma chain ending in Root.

All potential patterns are output in the P array.

Definition at line 351 of file PPCInstrInfo.cpp.

References assert(), llvm::dbgs(), FMAOpIdxInfo, llvm::MachineInstr::FmNsz, llvm::MachineInstr::FmReassoc, llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineBasicBlock::getParent(), llvm::MachineInstr::getParent(), llvm::MachineOperand::getReg(), llvm::MachineFunction::getRegInfo(), getRegisterInfo(), Idx, InfoArrayIdxAddOpIdx, InfoArrayIdxFAddInst, InfoArrayIdxFSubInst, InfoArrayIdxMULOpIdx, isLoadFromConstantPool(), llvm::Register::isVirtual(), LLVM_DEBUG, MBB, MRI, llvm::SmallVectorTemplateBase< T, bool >::push_back(), llvm::REASSOC_XMM_AMM_BMM, llvm::REASSOC_XY_AMM_BMM, llvm::REASSOC_XY_BAC, llvm::REASSOC_XY_BCA, TRI, and true.

Referenced by getMachineCombinerPatterns().

◆ getInstrLatency()

|

override |

Definition at line 138 of file PPCInstrInfo.cpp.

References llvm::InstrItineraryData::getOperandCycle(), llvm::MachineOperand::isDef(), llvm::MachineOperand::isImplicit(), llvm::MachineOperand::isReg(), llvm::Latency, MI, and UseOldLatencyCalc.

Referenced by getOperandLatency().

◆ getInstSizeInBytes()

|

override |

GetInstSize - Return the number of bytes of code the specified instruction may be.

This returns the maximum number of bytes.

Definition at line 2947 of file PPCInstrInfo.cpp.

References llvm::get(), llvm::TargetMachine::getMCAsmInfo(), llvm::StackMapOpers::getNumPatchBytes(), llvm::PatchPointOpers::getNumPatchBytes(), llvm::MachineFunction::getTarget(), and MI.

◆ getLoadOpcodeForSpill()

| unsigned PPCInstrInfo::getLoadOpcodeForSpill | ( | const TargetRegisterClass * | RC | ) | const |

Definition at line 1921 of file PPCInstrInfo.cpp.

◆ getMachineCombinerPatterns()

|

override |

Return true when there is potentially a faster code sequence for an instruction chain ending in <Root>.

All potential patterns are output in the <Pattern> array.

Definition at line 753 of file PPCInstrInfo.cpp.

References llvm::Aggressive, getFMAPatterns(), llvm::TargetInstrInfo::getMachineCombinerPatterns(), llvm::TargetMachine::getOptLevel(), and llvm::PPCSubtarget::getTargetMachine().

◆ getMemOperandsWithOffsetWidth()

|

override |

Get the base operand and byte offset of an instruction that reads/writes memory.

Definition at line 2836 of file PPCInstrInfo.cpp.

References getMemOperandWithOffsetWidth(), llvm::Offset, llvm::SmallVectorTemplateBase< T, bool >::push_back(), and TRI.

◆ getMemOperandWithOffsetWidth()

| bool PPCInstrInfo::getMemOperandWithOffsetWidth | ( | const MachineInstr & | LdSt, |

| const MachineOperand *& | BaseOp, | ||

| int64_t & | Offset, | ||

| LocationSize & | Width, | ||

| const TargetRegisterInfo * | TRI | ||

| ) | const |

Return true if get the base operand, byte offset of an instruction and the memory width.

Width is the size of memory that is being loaded/stored (e.g. 1, 2, 4, 8).

Definition at line 5519 of file PPCInstrInfo.cpp.

References llvm::MachineOperand::getImm(), llvm::MachineInstr::getNumExplicitOperands(), llvm::MachineInstr::getOperand(), getSize(), llvm::MachineInstr::hasOneMemOperand(), llvm::MachineOperand::isFI(), llvm::MachineOperand::isImm(), llvm::MachineOperand::isReg(), llvm::MachineInstr::mayLoadOrStore(), llvm::MachineInstr::memoperands_begin(), and llvm::Offset.

Referenced by areMemAccessesTriviallyDisjoint(), getMemOperandsWithOffsetWidth(), and shouldClusterMemOps().

◆ getNop()

|

override |

Return the noop instruction to use for a noop.

Definition at line 1251 of file PPCInstrInfo.cpp.

References llvm::MCInst::setOpcode().

◆ getOperandLatency() [1/2]

|

override |

Definition at line 168 of file PPCInstrInfo.cpp.

References DefMI, llvm::PPC::DIR_7400, llvm::PPC::DIR_750, llvm::PPC::DIR_970, llvm::PPC::DIR_E5500, llvm::PPC::DIR_PWR4, llvm::PPC::DIR_PWR5, llvm::PPC::DIR_PWR5X, llvm::PPC::DIR_PWR6, llvm::PPC::DIR_PWR6X, llvm::PPC::DIR_PWR7, llvm::PPC::DIR_PWR8, llvm::PPCSubtarget::getCPUDirective(), getInstrLatency(), llvm::MachineInstr::getParent(), llvm::MachineOperand::getReg(), llvm::Latency, MRI, and UseMI.

◆ getOperandLatency() [2/2]

|

inlineoverride |

Definition at line 342 of file PPCInstrInfo.h.

◆ getRecordFormOpcode()

|

static |

Definition at line 5107 of file PPCInstrInfo.cpp.

◆ getRegisterInfo()

|

inline |

getRegisterInfo - TargetInstrInfo is a superset of MRegister info.

As such, whenever a client has an instance of instruction info, it should always be able to get register info as well (through this method).

Definition at line 274 of file PPCInstrInfo.h.

Referenced by areMemAccessesTriviallyDisjoint(), copyPhysReg(), finalizeInsInstrs(), foldFrameOffset(), getDefMIPostRA(), getFMAPatterns(), llvm::PPCSubtarget::getRegisterInfo(), optimizeCompareInstr(), replaceInstrOperandWithImm(), shouldClusterMemOps(), and shouldReduceRegisterPressure().

◆ getSerializableDirectMachineOperandTargetFlags()

|

override |

Definition at line 2972 of file PPCInstrInfo.cpp.

◆ getStoreOpcodeForSpill()

| unsigned PPCInstrInfo::getStoreOpcodeForSpill | ( | const TargetRegisterClass * | RC | ) | const |

Definition at line 1915 of file PPCInstrInfo.cpp.

◆ hasGOTFlag()

Definition at line 308 of file PPCInstrInfo.h.

References llvm::PPCII::MO_GOT_FLAG, llvm::PPCII::MO_GOT_PCREL_FLAG, llvm::PPCII::MO_GOT_TLSGD_PCREL_FLAG, llvm::PPCII::MO_GOT_TLSLD_PCREL_FLAG, and llvm::PPCII::MO_GOT_TPREL_PCREL_FLAG.

◆ hasLowDefLatency()

|

inlineoverride |

Definition at line 350 of file PPCInstrInfo.h.

◆ hasPCRelFlag()

Definition at line 300 of file PPCInstrInfo.h.

References llvm::PPCII::MO_GOT_PCREL_FLAG, llvm::PPCII::MO_GOT_TLSGD_PCREL_FLAG, llvm::PPCII::MO_GOT_TLSLD_PCREL_FLAG, llvm::PPCII::MO_GOT_TPREL_PCREL_FLAG, llvm::PPCII::MO_PCREL_FLAG, llvm::PPCII::MO_TLS_PCREL_FLAG, and llvm::PPCII::MO_TPREL_PCREL_FLAG.

Referenced by isValidPCRelNode().

◆ hasTLSFlag()

Definition at line 315 of file PPCInstrInfo.h.

References llvm::PPCII::MO_DTPREL_LO, llvm::PPCII::MO_GOT_TLSGD_PCREL_FLAG, llvm::PPCII::MO_GOT_TLSLD_PCREL_FLAG, llvm::PPCII::MO_GOT_TPREL_PCREL_FLAG, llvm::PPCII::MO_TLS, llvm::PPCII::MO_TLS_PCREL_FLAG, llvm::PPCII::MO_TLSGD_FLAG, llvm::PPCII::MO_TLSGDM_FLAG, llvm::PPCII::MO_TLSLD_FLAG, llvm::PPCII::MO_TLSLD_LO, llvm::PPCII::MO_TPREL_FLAG, llvm::PPCII::MO_TPREL_HA, llvm::PPCII::MO_TPREL_LO, and llvm::PPCII::MO_TPREL_PCREL_FLAG.

Referenced by getTOCEntryTypeForMO().

◆ insertBranch()

|

override |

Definition at line 1467 of file PPCInstrInfo.cpp.

References llvm::MachineInstrBuilder::add(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addMBB(), assert(), llvm::BuildMI(), Cond, DL, llvm::get(), getReg(), llvm::PPCSubtarget::isPPC64(), MBB, llvm::PPC::PRED_BIT_SET, llvm::PPC::PRED_BIT_UNSET, and TBB.

◆ insertNoop()

|

override |

Definition at line 1231 of file PPCInstrInfo.cpp.

References llvm::BuildMI(), llvm::PPC::DIR_PWR6, llvm::PPC::DIR_PWR7, llvm::PPC::DIR_PWR8, llvm::PPC::DIR_PWR9, DL, llvm::get(), llvm::PPCSubtarget::getCPUDirective(), MBB, and MI.

◆ insertSelect()

|

override |

Definition at line 1566 of file PPCInstrInfo.cpp.

References llvm::MachineInstrBuilder::addReg(), assert(), llvm::BuildMI(), Cond, llvm::get(), llvm::MachineBasicBlock::getParent(), getReg(), llvm::MachineFunction::getRegInfo(), MBB, MI, MRI, llvm::PPC::PRED_BIT_SET, llvm::PPC::PRED_BIT_UNSET, llvm::PPC::PRED_EQ, llvm::PPC::PRED_EQ_MINUS, llvm::PPC::PRED_EQ_PLUS, llvm::PPC::PRED_GE, llvm::PPC::PRED_GE_MINUS, llvm::PPC::PRED_GE_PLUS, llvm::PPC::PRED_GT, llvm::PPC::PRED_GT_MINUS, llvm::PPC::PRED_GT_PLUS, llvm::PPC::PRED_LE, llvm::PPC::PRED_LE_MINUS, llvm::PPC::PRED_LE_PLUS, llvm::PPC::PRED_LT, llvm::PPC::PRED_LT_MINUS, llvm::PPC::PRED_LT_PLUS, llvm::PPC::PRED_NE, llvm::PPC::PRED_NE_MINUS, llvm::PPC::PRED_NE_PLUS, llvm::PPC::PRED_NU, llvm::PPC::PRED_NU_MINUS, llvm::PPC::PRED_NU_PLUS, llvm::PPC::PRED_UN, llvm::PPC::PRED_UN_MINUS, and llvm::PPC::PRED_UN_PLUS.

◆ instrHasImmForm()

| bool PPCInstrInfo::instrHasImmForm | ( | unsigned | Opc, |

| bool | IsVFReg, | ||

| ImmInstrInfo & | III, | ||

| bool | PostRA | ||

| ) | const |

Definition at line 3932 of file PPCInstrInfo.cpp.

References llvm::ImmInstrInfo::ImmMustBeMultipleOf, llvm::ImmInstrInfo::ImmOpcode, llvm::ImmInstrInfo::ImmOpNo, llvm::ImmInstrInfo::ImmWidth, llvm::ImmInstrInfo::IsCommutative, llvm::ImmInstrInfo::IsSummingOperands, llvm_unreachable, llvm::ImmInstrInfo::OpNoForForwarding, llvm::ImmInstrInfo::SignedImm, llvm::ImmInstrInfo::TruncateImmTo, llvm::ImmInstrInfo::ZeroIsSpecialNew, and llvm::ImmInstrInfo::ZeroIsSpecialOrig.

Referenced by convertToImmediateForm(), and isImmInstrEligibleForFolding().

◆ isADDIInstrEligibleForFolding()

| bool PPCInstrInfo::isADDIInstrEligibleForFolding | ( | MachineInstr & | ADDIMI, |

| int64_t & | Imm | ||

| ) | const |

Definition at line 3621 of file PPCInstrInfo.cpp.

References llvm::MachineOperand::getImm(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), and llvm::MachineOperand::isImm().

Referenced by isValidToBeChangedReg().

◆ isADDInstrEligibleForFolding()

| bool PPCInstrInfo::isADDInstrEligibleForFolding | ( | MachineInstr & | ADDMI | ) | const |

Definition at line 3638 of file PPCInstrInfo.cpp.

References llvm::MachineInstr::getOpcode().

Referenced by foldFrameOffset().

◆ isAssociativeAndCommutative()

|

override |

Definition at line 233 of file PPCInstrInfo.cpp.

References llvm::MachineInstr::FmNsz, llvm::MachineInstr::FmReassoc, llvm::MachineInstr::getFlag(), and llvm::MachineInstr::getOpcode().

◆ isBDNZ()

Check Opcode is BDNZ (Decrement CTR and branch if it is still nonzero).

Definition at line 5410 of file PPCInstrInfo.cpp.

References llvm::PPCSubtarget::isPPC64().

Referenced by analyzeLoopForPipelining().

◆ isCoalescableExtInstr()

|

override |

Definition at line 1048 of file PPCInstrInfo.cpp.

References MI.

◆ isImmInstrEligibleForFolding()

| bool PPCInstrInfo::isImmInstrEligibleForFolding | ( | MachineInstr & | MI, |

| unsigned & | BaseReg, | ||

| unsigned & | XFormOpcode, | ||

| int64_t & | OffsetOfImmInstr, | ||

| ImmInstrInfo & | III | ||

| ) | const |

Definition at line 3645 of file PPCInstrInfo.cpp.

References assert(), llvm::MachineOperand::getImm(), llvm::PPCRegisterInfo::getMappedIdxOpcForImmOpc(), llvm::MachineOperand::getReg(), llvm::ImmInstrInfo::ImmOpNo, instrHasImmForm(), llvm::MachineOperand::isImm(), llvm::MachineOperand::isKill(), llvm::MachineOperand::isReg(), llvm::ImmInstrInfo::IsSummingOperands, llvm::PPC::isVFRegister(), MI, and llvm::ImmInstrInfo::OpNoForForwarding.

Referenced by foldFrameOffset().

◆ isLoadFromConstantPool()

| bool PPCInstrInfo::isLoadFromConstantPool | ( | MachineInstr * | I | ) | const |

Definition at line 656 of file PPCInstrInfo.cpp.

References llvm::PseudoSourceValue::ConstantPool, and I.

Referenced by getFMAPatterns().

◆ isLoadFromStackSlot()

|

override |

Definition at line 1063 of file PPCInstrInfo.cpp.

References llvm::is_contained(), and MI.

◆ isPredicated()

|

override |

Definition at line 2148 of file PPCInstrInfo.cpp.

◆ isPrefixed()

Definition at line 279 of file PPCInstrInfo.h.

References llvm::get(), and llvm::PPCII::Prefixed.

◆ isProfitableToDupForIfCvt()

|

inlineoverride |

Definition at line 518 of file PPCInstrInfo.h.

◆ isProfitableToIfCvt() [1/2]

|

inlineoverride |

Definition at line 506 of file PPCInstrInfo.h.

◆ isProfitableToIfCvt() [2/2]

|

override |

Definition at line 2139 of file PPCInstrInfo.cpp.

References MBBDefinesCTR().

◆ isProfitableToUnpredicate()

|

inlineoverride |

Definition at line 523 of file PPCInstrInfo.h.

◆ isReallyTriviallyReMaterializable()

|

override |

Definition at line 1079 of file PPCInstrInfo.cpp.

References llvm::TargetInstrInfo::isReallyTriviallyReMaterializable(), and MI.

◆ isSameClassPhysRegCopy()

Definition at line 289 of file PPCInstrInfo.h.

◆ isSchedulingBoundary()

|

override |

Definition at line 2159 of file PPCInstrInfo.cpp.

References llvm::TargetInstrInfo::isSchedulingBoundary(), MBB, and MI.

◆ isSExt32To64()

Definition at line 282 of file PPCInstrInfo.h.

References llvm::get(), and llvm::PPCII::SExt32To64.

◆ isSignExtended()

|

inline |

Definition at line 617 of file PPCInstrInfo.h.

References isSignOrZeroExtended(), MRI, and Reg.

Referenced by optimizeCompareInstr().

◆ isSignOrZeroExtended()

| std::pair< bool, bool > PPCInstrInfo::isSignOrZeroExtended | ( | const unsigned | Reg, |

| const unsigned | BinOpDepth, | ||

| const MachineRegisterInfo * | MRI | ||

| ) | const |

Definition at line 5242 of file PPCInstrInfo.cpp.

References definedBySignExtendingOp(), definedByZeroExtendingOp(), llvm::Function::getAttributes(), llvm::IntegerType::getBitWidth(), llvm::Function::getEntryBlock(), llvm::MachineFunction::getFunction(), llvm::MachineOperand::getGlobal(), llvm::MachineFunction::getInfo(), llvm::MachineInstr::getOperand(), llvm::MachineFunction::getRegInfo(), llvm::AttributeList::getRetAttrs(), llvm::Function::getReturnType(), llvm::MachineFunction::getSubtarget(), I, llvm::MachineBasicBlock::instr_begin(), llvm::MachineInstr::isCall(), llvm::MachineOperand::isGlobal(), llvm::MachineRegisterInfo::isLiveIn(), llvm::PPCFunctionInfo::isLiveInSExt(), llvm::PPCFunctionInfo::isLiveInZExt(), isSignOrZeroExtended(), llvm::PPCSubtarget::isSVR4ABI(), llvm::Register::isVirtualRegister(), MAX_BINOP_DEPTH, MBB, MI, and MRI.

Referenced by isSignExtended(), isSignOrZeroExtended(), and isZeroExtended().

◆ isStoreToStackSlot()

|

override |

Definition at line 1119 of file PPCInstrInfo.cpp.

References llvm::is_contained(), and MI.

◆ isTOCSaveMI()

| bool PPCInstrInfo::isTOCSaveMI | ( | const MachineInstr & | MI | ) | const |

Definition at line 5220 of file PPCInstrInfo.cpp.

References llvm::PPCSubtarget::getFrameLowering(), llvm::PPCFrameLowering::getTOCSaveOffset(), llvm::PPCSubtarget::isPPC64(), and MI.

◆ isValidToBeChangedReg()

| bool PPCInstrInfo::isValidToBeChangedReg | ( | MachineInstr * | ADDMI, |

| unsigned | Index, | ||

| MachineInstr *& | ADDIMI, | ||

| int64_t & | OffsetAddi, | ||

| int64_t | OffsetImm | ||

| ) | const |

Definition at line 3688 of file PPCInstrInfo.cpp.

References assert(), getDefMIPostRA(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), isADDIInstrEligibleForFolding(), and llvm::MachineOperand::isKill().

Referenced by foldFrameOffset().

◆ isXFormMemOp()

Definition at line 276 of file PPCInstrInfo.h.

References llvm::get(), and llvm::PPCII::XFormMemOp.

◆ isZeroExtended()

|

inline |

Definition at line 623 of file PPCInstrInfo.h.

References isSignOrZeroExtended(), MRI, and Reg.

Referenced by optimizeCompareInstr().

◆ isZExt32To64()

Definition at line 285 of file PPCInstrInfo.h.

References llvm::get(), and llvm::PPCII::ZExt32To64.

◆ loadRegFromStackSlot()

|

override |

Definition at line 2015 of file PPCInstrInfo.cpp.

References loadRegFromStackSlotNoUpd(), MBB, MI, TRI, and updatedRC().

◆ loadRegFromStackSlotNoUpd()

| void PPCInstrInfo::loadRegFromStackSlotNoUpd | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock::iterator | MBBI, | ||

| unsigned | DestReg, | ||

| int | FrameIndex, | ||

| const TargetRegisterClass * | RC, | ||

| const TargetRegisterInfo * | TRI | ||

| ) | const |

Definition at line 1993 of file PPCInstrInfo.cpp.

References llvm::SmallVectorTemplateCommon< T, typename >::back(), DL, llvm::MachineBasicBlock::end(), llvm::MachinePointerInfo::getFixedStack(), llvm::MachineFunction::getFrameInfo(), llvm::MachineFunction::getMachineMemOperand(), llvm::MachineFrameInfo::getObjectAlign(), llvm::MachineFrameInfo::getObjectSize(), llvm::MachineBasicBlock::getParent(), llvm::MachineBasicBlock::insert(), MBB, MI, llvm::MachineMemOperand::MOLoad, and llvm::SmallVectorBase< Size_T >::size().

Referenced by loadRegFromStackSlot().

◆ materializeImmPostRA()

| void PPCInstrInfo::materializeImmPostRA | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock::iterator | MBBI, | ||

| const DebugLoc & | DL, | ||

| Register | Reg, | ||

| int64_t | Imm | ||

| ) | const |

Definition at line 3353 of file PPCInstrInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), assert(), llvm::BuildMI(), DL, llvm::get(), llvm::MachineBasicBlock::getParent(), llvm::MachineFunction::getRegInfo(), llvm::PPCSubtarget::isPPC64(), llvm::MachineRegisterInfo::isSSA(), llvm::RegState::Kill, MBB, and MBBI.

◆ onlyFoldImmediate()

| bool PPCInstrInfo::onlyFoldImmediate | ( | MachineInstr & | UseMI, |

| MachineInstr & | DefMI, | ||

| Register | Reg | ||

| ) | const |

Definition at line 2047 of file PPCInstrInfo.cpp.

References assert(), llvm::MCOperandInfo::Constraints, llvm::dbgs(), DefMI, llvm::MCInstrDesc::getNumOperands(), llvm::MachineInstrBuilder::getReg(), llvm::MCOperandInfo::isLookupPtrRegClass(), llvm::PPCSubtarget::isPPC64(), llvm::MCInstrDesc::isPseudo(), LLVM_DEBUG, llvm::MCInstrDesc::operands(), llvm::MCOperandInfo::RegClass, and UseMI.

Referenced by foldImmediate().

◆ optimizeCmpPostRA()

| bool PPCInstrInfo::optimizeCmpPostRA | ( | MachineInstr & | MI | ) | const |

Definition at line 2761 of file PPCInstrInfo.cpp.

References llvm::MachineInstrBuilder::addReg(), analyzeCompare(), assert(), llvm::MachineInstr::clearRegisterDeads(), llvm::dbgs(), llvm::MachineInstr::definesRegister(), llvm::MachineInstr::dump(), llvm::get(), getDefMIPostRA(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineBasicBlock::getParent(), llvm::MachineInstr::getParent(), llvm::MachineOperand::getReg(), llvm::MachineFunction::getRegInfo(), llvm::MachineInstr::hasImplicitDef(), llvm::RegState::ImplicitDefine, llvm::PPCSubtarget::isPPC64(), LLVM_DEBUG, MRI, and llvm::MachineInstr::setDesc().

◆ optimizeCompareInstr()

|

override |

Definition at line 2376 of file PPCInstrInfo.cpp.

References llvm::MachineInstrBuilder::addReg(), assert(), B, llvm::MachineBasicBlock::begin(), llvm::BuildMI(), llvm::MachineOperand::CreateReg(), DisableCmpOpt, llvm::MachineBasicBlock::end(), llvm::MachineInstr::eraseFromParent(), llvm::get(), llvm::MachineInstr::getFlag(), llvm::MachineOperand::getImm(), llvm::PPC::getNonRecordFormOpcode(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::PPC::getPredicate(), llvm::PPC::getPredicateCondition(), llvm::PPC::getPredicateHint(), llvm::MachineOperand::getReg(), getRegisterInfo(), llvm::MachineOperand::getSubReg(), llvm::PPC::getSwappedPredicate(), I, llvm::MCInstrDesc::implicit_defs(), llvm::MCInstrDesc::implicit_uses(), llvm::PPCSubtarget::isPPC64(), isSignExtended(), llvm::Register::isVirtual(), isZeroExtended(), llvm::RegState::Kill, MI, MRI, llvm::MachineInstr::NoSWrap, llvm::PPC::PRED_EQ, llvm::PPC::PRED_GE, llvm::PPC::PRED_GT, llvm::PPC::PRED_LE, llvm::PPC::PRED_LT, llvm::PPC::PRED_NE, llvm::SmallVectorTemplateBase< T, bool >::push_back(), llvm::MachineOperand::setImm(), llvm::SmallVectorBase< Size_T >::size(), TRI, and UseMI.

◆ PredicateInstruction()

|

override |

Definition at line 2176 of file PPCInstrInfo.cpp.

References llvm::MachineInstrBuilder::add(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addMBB(), llvm::MachineInstrBuilder::addReg(), llvm::get(), getReg(), llvm::RegState::Implicit, llvm::RegState::ImplicitDefine, llvm::PPCSubtarget::isPPC64(), llvm_unreachable, MBB, MI, llvm::PPC::PRED_BIT_SET, and llvm::PPC::PRED_BIT_UNSET.

◆ removeBranch()

|

override |

Definition at line 1435 of file PPCInstrInfo.cpp.

References assert(), llvm::MachineBasicBlock::begin(), llvm::MachineBasicBlock::end(), llvm::MachineBasicBlock::getLastNonDebugInstr(), I, and MBB.

◆ replaceInstrOperandWithImm()

| void PPCInstrInfo::replaceInstrOperandWithImm | ( | MachineInstr & | MI, |

| unsigned | OpNo, | ||

| int64_t | Imm | ||

| ) | const |

Definition at line 3282 of file PPCInstrInfo.cpp.

References assert(), getRegisterInfo(), llvm::MachineOperand::isImplicit(), MI, and TRI.

◆ replaceInstrWithLI()

| void PPCInstrInfo::replaceInstrWithLI | ( | MachineInstr & | MI, |

| const LoadImmediateInfo & | LII | ||

| ) | const |

Definition at line 3313 of file PPCInstrInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), llvm::get(), llvm::LoadImmediateInfo::Imm, llvm::RegState::ImplicitDefine, llvm::LoadImmediateInfo::Is64Bit, MI, and llvm::LoadImmediateInfo::SetCR.

◆ reverseBranchCondition()

|

override |

Definition at line 2033 of file PPCInstrInfo.cpp.

References assert(), Cond, getReg(), and llvm::PPC::InvertPredicate().

◆ setSpecialOperandAttr() [1/2]

| void PPCInstrInfo::setSpecialOperandAttr | ( | MachineInstr & | MI, |

| uint32_t | Flags | ||

| ) | const |

Definition at line 220 of file PPCInstrInfo.cpp.

References llvm::MachineInstr::IsExact, MI, llvm::MachineInstr::NoSWrap, and llvm::MachineInstr::NoUWrap.

◆ setSpecialOperandAttr() [2/2]

|

inline |

This is an architecture-specific helper function of reassociateOps.

Set special operand attributes for new instructions after reassociation.

Definition at line 1294 of file TargetInstrInfo.h.

◆ shouldClusterMemOps()

|

override |

Returns true if the two given memory operations should be scheduled adjacent.

Definition at line 2887 of file PPCInstrInfo.cpp.

References assert(), llvm::ArrayRef< T >::front(), llvm::MachineOperand::getIndex(), getMemOperandWithOffsetWidth(), llvm::MachineInstr::getOpcode(), llvm::MachineOperand::getParent(), llvm::MachineOperand::getReg(), getRegisterInfo(), llvm::LocationSize::getValue(), isClusterableLdStOpcPair(), llvm::MachineOperand::isFI(), isLdStSafeToCluster(), llvm::MachineOperand::isReg(), llvm::ArrayRef< T >::size(), and TRI.

◆ shouldReduceRegisterPressure()

|

override |

On PowerPC, we leverage machine combiner pass to reduce register pressure when the register pressure is high for one BB.

Return true if register pressure for MBB is high and ABI is supported to reduce register pressure. Otherwise return false.

Definition at line 596 of file PPCInstrInfo.cpp.

References assert(), llvm::RegPressureTracker::closeRegion(), llvm::RegisterOperands::collect(), EnableFMARegPressureReduction, llvm::MachineBasicBlock::end(), FMARPFactor, llvm::TargetMachine::getCodeModel(), llvm::MachineBasicBlock::getParent(), llvm::RegPressureTracker::getPos(), llvm::RegPressureTracker::getPressure(), llvm::MachineFunction::getRegInfo(), getRegisterInfo(), llvm::PPCSubtarget::getTargetMachine(), llvm::RegPressureTracker::init(), llvm::PPCSubtarget::isPPC64(), llvm::RegisterPressure::MaxSetPressure, MBB, llvm::CodeModel::Medium, MI, MRI, llvm::RegPressureTracker::recede(), llvm::RegPressureTracker::recedeSkipDebugValues(), llvm::reverse(), and TRI.

◆ storeRegToStackSlot()

|

override |

Definition at line 1968 of file PPCInstrInfo.cpp.

References MBB, MI, storeRegToStackSlotNoUpd(), TRI, and updatedRC().

◆ storeRegToStackSlotNoUpd()

| void PPCInstrInfo::storeRegToStackSlotNoUpd | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock::iterator | MBBI, | ||

| unsigned | SrcReg, | ||

| bool | isKill, | ||

| int | FrameIndex, | ||

| const TargetRegisterClass * | RC, | ||

| const TargetRegisterInfo * | TRI | ||

| ) | const |

Definition at line 1948 of file PPCInstrInfo.cpp.

References llvm::SmallVectorTemplateCommon< T, typename >::back(), llvm::MachinePointerInfo::getFixedStack(), llvm::MachineFunction::getFrameInfo(), llvm::MachineFunction::getMachineMemOperand(), llvm::MachineFrameInfo::getObjectAlign(), llvm::MachineFrameInfo::getObjectSize(), llvm::MachineBasicBlock::getParent(), llvm::MachineBasicBlock::insert(), MBB, MI, llvm::MachineMemOperand::MOStore, and llvm::SmallVectorBase< Size_T >::size().

Referenced by storeRegToStackSlot().

◆ SubsumesPredicate()

|

override |

Definition at line 2280 of file PPCInstrInfo.cpp.

References assert(), getReg(), llvm::PPC::PRED_EQ, llvm::PPC::PRED_GE, llvm::PPC::PRED_GT, llvm::PPC::PRED_LE, llvm::PPC::PRED_LT, and llvm::ArrayRef< T >::size().

◆ updatedRC()

| const TargetRegisterClass * PPCInstrInfo::updatedRC | ( | const TargetRegisterClass * | RC | ) | const |

Definition at line 5101 of file PPCInstrInfo.cpp.

Referenced by loadRegFromStackSlot(), and storeRegToStackSlot().

◆ useMachineCombiner()

|

inlineoverride |

Definition at line 359 of file PPCInstrInfo.h.

The documentation for this class was generated from the following files:

- lib/Target/PowerPC/PPCInstrInfo.h

- lib/Target/PowerPC/PPCInstrInfo.cpp