#include "Target/AMDGPU/SIInstrInfo.h"

Public Types | |

| enum | TargetOperandFlags { MO_MASK = 0xf , MO_NONE = 0 , MO_GOTPCREL = 1 , MO_GOTPCREL32 = 2 , MO_GOTPCREL32_LO = 2 , MO_GOTPCREL32_HI = 3 , MO_REL32 = 4 , MO_REL32_LO = 4 , MO_REL32_HI = 5 , MO_FAR_BRANCH_OFFSET = 6 , MO_ABS32_LO = 8 , MO_ABS32_HI = 9 } |

Protected Member Functions | |

| std::optional< DestSourcePair > | isCopyInstrImpl (const MachineInstr &MI) const override |

| If the specific machine instruction is a instruction that moves/copies value from one register to another register return destination and source registers as machine operands. | |

| bool | swapSourceModifiers (MachineInstr &MI, MachineOperand &Src0, unsigned Src0OpName, MachineOperand &Src1, unsigned Src1OpName) const |

| MachineInstr * | commuteInstructionImpl (MachineInstr &MI, bool NewMI, unsigned OpIdx0, unsigned OpIdx1) const override |

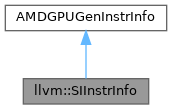

Detailed Description

Definition at line 83 of file SIInstrInfo.h.

Member Enumeration Documentation

◆ TargetOperandFlags

| Enumerator | |

|---|---|

| MO_MASK | |

| MO_NONE | |

| MO_GOTPCREL | |

| MO_GOTPCREL32 | |

| MO_GOTPCREL32_LO | |

| MO_GOTPCREL32_HI | |

| MO_REL32 | |

| MO_REL32_LO | |

| MO_REL32_HI | |

| MO_FAR_BRANCH_OFFSET | |

| MO_ABS32_LO | |

| MO_ABS32_HI | |

Definition at line 197 of file SIInstrInfo.h.

Constructor & Destructor Documentation

◆ SIInstrInfo()

|

explicit |

Definition at line 66 of file SIInstrInfo.cpp.

References llvm::TargetSchedModel::init().

Member Function Documentation

◆ allowNegativeFlatOffset()

Returns true if negative offsets are allowed for the given FlatVariant.

Definition at line 9124 of file SIInstrInfo.cpp.

References llvm::SIInstrFlags::FLAT, llvm::SIInstrFlags::FlatScratch, llvm::GCNSubtarget::hasNegativeScratchOffsetBug(), and llvm::AMDGPU::isGFX12Plus().

Referenced by isLegalFLATOffset(), and splitFlatOffset().

◆ analyzeBranch()

|

override |

Definition at line 3026 of file SIInstrInfo.cpp.

References analyzeBranchImpl(), Cond, llvm::MachineBasicBlock::end(), llvm::MachineBasicBlock::getFirstTerminator(), I, llvm_unreachable, MBB, and TBB.

◆ analyzeBranchImpl()

| bool SIInstrInfo::analyzeBranchImpl | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock::iterator | I, | ||

| MachineBasicBlock *& | TBB, | ||

| MachineBasicBlock *& | FBB, | ||

| SmallVectorImpl< MachineOperand > & | Cond, | ||

| bool | AllowModify | ||

| ) | const |

Definition at line 2983 of file SIInstrInfo.cpp.

References Cond, llvm::MachineOperand::CreateImm(), llvm::MachineBasicBlock::end(), I, MBB, and TBB.

Referenced by analyzeBranch().

◆ analyzeCompare()

|

override |

Definition at line 9652 of file SIInstrInfo.cpp.

References MI.

◆ areLoadsFromSameBasePtr()

|

override |

Definition at line 235 of file SIInstrInfo.cpp.

References assert(), llvm::get(), llvm::SDNode::getAsZExtVal(), llvm::SDNode::getConstantOperandVal(), llvm::SDNode::getMachineOpcode(), llvm::AMDGPU::getNamedOperandIdx(), getNumOperandsNoGlue(), llvm::SDNode::getOperand(), llvm::ConstantSDNode::getZExtValue(), llvm::AMDGPU::hasNamedOperand(), isDS(), llvm::SDNode::isMachineOpcode(), isMTBUF(), isMUBUF(), isSMRD(), and nodesHaveSameOperandValue().

◆ areMemAccessesTriviallyDisjoint()

|

override |

Definition at line 3671 of file SIInstrInfo.cpp.

References assert(), llvm::MachineInstr::hasOrderedMemoryRef(), llvm::MachineInstr::hasUnmodeledSideEffects(), isDS(), isFLAT(), isFLATGlobal(), isFLATScratch(), isLDSDMA(), isMTBUF(), isMUBUF(), isSegmentSpecificFLAT(), isSMRD(), and llvm::MachineInstr::mayLoadOrStore().

◆ buildExtractSubReg()

| unsigned SIInstrInfo::buildExtractSubReg | ( | MachineBasicBlock::iterator | MI, |

| MachineRegisterInfo & | MRI, | ||

| const MachineOperand & | SuperReg, | ||

| const TargetRegisterClass * | SuperRC, | ||

| unsigned | SubIdx, | ||

| const TargetRegisterClass * | SubRC | ||

| ) | const |

Definition at line 5593 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), DL, llvm::get(), llvm::MachineOperand::getReg(), llvm::MachineOperand::getSubReg(), MBB, MI, MRI, and SubReg.

Referenced by buildExtractSubRegOrImm().

◆ buildExtractSubRegOrImm()

| MachineOperand SIInstrInfo::buildExtractSubRegOrImm | ( | MachineBasicBlock::iterator | MI, |

| MachineRegisterInfo & | MRI, | ||

| const MachineOperand & | SuperReg, | ||

| const TargetRegisterClass * | SuperRC, | ||

| unsigned | SubIdx, | ||

| const TargetRegisterClass * | SubRC | ||

| ) | const |

Definition at line 5622 of file SIInstrInfo.cpp.

References buildExtractSubReg(), llvm::MachineOperand::CreateImm(), llvm::MachineOperand::CreateReg(), llvm_unreachable, MRI, and SubReg.

◆ buildShrunkInst()

| MachineInstr * SIInstrInfo::buildShrunkInst | ( | MachineInstr & | MI, |

| unsigned | NewOpcode | ||

| ) | const |

Definition at line 4427 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::add(), assert(), llvm::BuildMI(), copyFlagsToImplicitVCC(), fixImplicitOperands(), llvm::get(), getNamedOperand(), llvm::AMDGPU::getNamedOperandIdx(), llvm::AMDGPU::hasNamedOperand(), MBB, MI, and llvm::MachineInstrBuilder::setMIFlags().

◆ canInsertSelect()

|

override |

Definition at line 3170 of file SIInstrInfo.cpp.

References Cond, llvm::MachineBasicBlock::getParent(), llvm::AMDGPU::getRegBitWidth(), llvm::MachineFunction::getRegInfo(), llvm::SIRegisterInfo::hasVGPRs(), llvm::SIRegisterInfo::isSGPRClass(), MBB, and MRI.

◆ canShrink()

| bool SIInstrInfo::canShrink | ( | const MachineInstr & | MI, |

| const MachineRegisterInfo & | MRI | ||

| ) | const |

Definition at line 4357 of file SIInstrInfo.cpp.

References getNamedOperand(), llvm::MachineOperand::getReg(), hasModifiersSet(), hasVALU32BitEncoding(), llvm::MachineOperand::isReg(), llvm::SIRegisterInfo::isVGPR(), MI, and MRI.

◆ commuteInstructionImpl()

|

overrideprotected |

Definition at line 2717 of file SIInstrInfo.cpp.

References assert(), llvm::TargetInstrInfo::commuteInstructionImpl(), commuteOpcode(), llvm::get(), llvm::AMDGPU::getNamedOperandIdx(), isOperandLegal(), llvm::MachineOperand::isReg(), MI, llvm::MachineInstr::setDesc(), std::swap(), swapRegAndNonRegOperand(), and swapSourceModifiers().

◆ commuteOpcode() [1/2]

|

inline |

Definition at line 318 of file SIInstrInfo.h.

References commuteOpcode(), and MI.

◆ commuteOpcode() [2/2]

| int SIInstrInfo::commuteOpcode | ( | unsigned | Opc | ) | const |

Definition at line 1148 of file SIInstrInfo.cpp.

References llvm::AMDGPU::getCommuteOrig(), llvm::AMDGPU::getCommuteRev(), and pseudoToMCOpcode().

Referenced by commuteInstructionImpl(), commuteOpcode(), and legalizeOperandsVOP2().

◆ convertNonUniformIfRegion()

| void SIInstrInfo::convertNonUniformIfRegion | ( | MachineBasicBlock * | IfEntry, |

| MachineBasicBlock * | IfEnd | ||

| ) | const |

Definition at line 8717 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::add(), llvm::MachineInstrBuilder::addReg(), assert(), llvm::BuildMI(), llvm::MachineBasicBlock::end(), llvm::MachineBasicBlock::erase(), llvm::get(), llvm::SIRegisterInfo::getBoolRC(), llvm::MachineBasicBlock::getFirstNonPHI(), llvm::MachineBasicBlock::getFirstTerminator(), llvm::MachineBasicBlock::getParent(), llvm::MachineFunction::getRegInfo(), llvm::MachineBasicBlock::insert(), and MRI.

◆ convertNonUniformLoopRegion()

| void SIInstrInfo::convertNonUniformLoopRegion | ( | MachineBasicBlock * | LoopEntry, |

| MachineBasicBlock * | LoopEnd | ||

| ) | const |

Definition at line 8742 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::add(), llvm::MachineInstrBuilder::addMBB(), llvm::MachineInstrBuilder::addReg(), assert(), llvm::MachineBasicBlock::begin(), llvm::BuildMI(), llvm::MachineBasicBlock::end(), llvm::MachineBasicBlock::erase(), llvm::get(), llvm::SIRegisterInfo::getBoolRC(), llvm::MachineBasicBlock::getFirstTerminator(), llvm::MachineBasicBlock::getParent(), llvm::MachineFunction::getRegInfo(), llvm::MachineBasicBlock::insert(), materializeImmediate(), MRI, and llvm::MachineBasicBlock::predecessors().

◆ convertToThreeAddress()

|

override |

Definition at line 3770 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::add(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstr::addOperand(), llvm::LiveVariables::VarInfo::AliveBlocks, assert(), llvm::BuildMI(), llvm::SparseBitVector< ElementSize >::clear(), DefMI, llvm::LiveRange::find(), llvm::get(), llvm::GCNSubtarget::getConstantBusLimit(), getFoldableImm(), llvm::MachineOperand::getImm(), llvm::LiveIntervals::getInstructionIndex(), llvm::LiveIntervals::getInterval(), llvm::AMDGPU::getMFMAEarlyClobberOp(), getNamedOperand(), llvm::AMDGPU::getNamedOperandIdx(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOperand(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), llvm::MachineFunction::getRegInfo(), llvm::SlotIndex::getRegSlot(), llvm::LiveVariables::getVarInfo(), llvm::LiveIntervals::hasInterval(), llvm::AMDGPU::hasNamedOperand(), llvm::AMDGPUSubtarget::hasTrue16BitInsts(), llvm::GCNSubtarget::hasVOP3Literal(), I, llvm::MachineOperand::isImm(), isInlineConstant(), isOperandLegal(), llvm::MachineOperand::isReg(), llvm::SIRegisterInfo::isSGPRReg(), isWMMA(), llvm::AMDGPU::mapWMMA2AddrTo3AddrOpcode(), MBB, MI, MRI, pseudoToMCOpcode(), llvm::MachineInstr::removeOperand(), llvm::LiveIntervals::ReplaceMachineInstrInMaps(), llvm::MachineInstr::setDesc(), llvm::MachineInstrBuilder::setMIFlags(), and updateLiveVariables().

◆ copyPhysReg()

|

override |

Definition at line 795 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), assert(), llvm::BuildMI(), contains(), copyPhysReg(), llvm::RegState::Define, DL, expandSGPRCopy(), Fix16BitCopies, llvm::get(), llvm::SIRegisterInfo::get32BitRegister(), llvm::SIRegisterInfo::getHWRegIndex(), llvm::getKillRegState(), llvm::SIRegisterInfo::getRegSplitParts(), llvm::SIRegisterInfo::getVGPR64Class(), llvm::GCNSubtarget::hasGFX90AInsts(), llvm::GCNSubtarget::hasMovB64(), llvm::GCNSubtarget::hasPkMovB32(), llvm::GCNSubtarget::hasScalarCompareEq64(), llvm::GCNSubtarget::hasSDWAScalar(), llvm::AMDGPUSubtarget::hasTrue16BitInsts(), llvm::SIRegisterInfo::hasVGPRs(), Idx, llvm::RegState::Implicit, indirectCopyToAGPR(), llvm::SIRegisterInfo::isAGPRClass(), llvm::AMDGPU::isHi(), llvm::SIRegisterInfo::isProperlyAlignedRC(), llvm::SIRegisterInfo::isSGPRClass(), MBB, MI, llvm::SISrcMods::OP_SEL_0, llvm::SISrcMods::OP_SEL_1, reportIllegalCopy(), llvm::ArrayRef< T >::size(), Size, SubReg, llvm::MachineInstr::tieOperands(), llvm::RegState::Undef, llvm::AMDGPU::SDWA::UNUSED_PRESERVE, llvm::AMDGPU::SDWA::WORD_0, and llvm::AMDGPU::SDWA::WORD_1.

Referenced by copyPhysReg().

◆ createPHIDestinationCopy()

|

override |

Definition at line 9405 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addReg(), llvm::MachineBasicBlock::begin(), llvm::BuildMI(), llvm::TargetInstrInfo::createPHIDestinationCopy(), DL, llvm::MachineBasicBlock::end(), llvm::get(), and MBB.

◆ createPHISourceCopy()

|

override |

Definition at line 9420 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), llvm::TargetInstrInfo::createPHISourceCopy(), DL, llvm::MachineBasicBlock::end(), llvm::get(), llvm::RegState::Implicit, llvm::GCNSubtarget::isWave32(), and MBB.

◆ CreateTargetMIHazardRecognizer()

|

override |

Definition at line 8815 of file SIInstrInfo.cpp.

References llvm::TargetInstrInfo::CreateTargetMIHazardRecognizer(), llvm::ScheduleDAGMI::hasVRegLiveness(), and llvm::ScheduleDAG::MF.

◆ CreateTargetPostRAHazardRecognizer() [1/2]

|

override |

This is used by the post-RA scheduler (SchedulePostRAList.cpp).

The post-RA version of misched uses CreateTargetMIHazardRecognizer.

Definition at line 8800 of file SIInstrInfo.cpp.

References llvm::ScheduleDAG::MF.

◆ CreateTargetPostRAHazardRecognizer() [2/2]

|

override |

This is the hazard recognizer used at -O0 by the PostRAHazardRecognizer pass.

Definition at line 8808 of file SIInstrInfo.cpp.

◆ decomposeMachineOperandsTargetFlags()

|

override |

Definition at line 8827 of file SIInstrInfo.cpp.

References MO_MASK.

◆ doesNotReadTiedSource() [1/2]

|

inlinestatic |

Definition at line 928 of file SIInstrInfo.h.

References MI, and llvm::SIInstrFlags::TiedSourceNotRead.

◆ doesNotReadTiedSource() [2/2]

Definition at line 932 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::TiedSourceNotRead.

◆ enforceOperandRCAlignment()

| void SIInstrInfo::enforceOperandRCAlignment | ( | MachineInstr & | MI, |

| unsigned | OpName | ||

| ) | const |

Definition at line 9858 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), llvm::MachineOperand::CreateReg(), DL, llvm::get(), llvm::AMDGPU::getNamedOperandIdx(), getOpSize(), llvm::MachineBasicBlock::getParent(), llvm::MachineFunction::getRegInfo(), llvm::SIRegisterInfo::isAGPR(), MI, MRI, and llvm::GCNSubtarget::needsAlignedVGPRs().

◆ expandMovDPP64()

| std::pair< MachineInstr *, MachineInstr * > SIInstrInfo::expandMovDPP64 | ( | MachineInstr & | MI | ) | const |

Definition at line 2596 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), assert(), llvm::BuildMI(), DL, llvm::drop_begin(), llvm::MachineBasicBlock::findDebugLoc(), llvm::get(), llvm::SrcOp::getImm(), getNamedOperand(), llvm::MachineBasicBlock::getParent(), llvm::SrcOp::getReg(), getReg(), llvm::MachineFunction::getRegInfo(), llvm::GCNSubtarget::hasMovB64(), I, llvm::AMDGPU::isLegalDPALU_DPPControl(), MBB, MI, MRI, and llvm::RegState::Undef.

Referenced by expandPostRAPseudo().

◆ expandPostRAPseudo()

|

override |

Definition at line 2043 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::add(), llvm::MachineInstrBuilder::addDef(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), llvm::MachineInstr::addRegisterDead(), llvm::MIBundleBuilder::append(), assert(), llvm::MIBundleBuilder::begin(), llvm::BuildMI(), llvm::MachineInstrBuilder::copyImplicitOps(), llvm::RegState::Define, DL, llvm::AMDGPU::VGPRIndexMode::DST_ENABLE, expandMovDPP64(), llvm::TargetInstrInfo::expandPostRAPseudo(), expandPostRAPseudo(), llvm::finalizeBundle(), llvm::MachineBasicBlock::findDebugLoc(), llvm::get(), llvm::SrcOp::getImm(), llvm::ilist_node_impl< OptionsT >::getIterator(), llvm::MCInstrDesc::getNumOperands(), llvm::MachineOperand::getOffset(), llvm::MachineInstr::getOperand(), getOpRegClass(), llvm::MachineBasicBlock::getParent(), llvm::SrcOp::getReg(), llvm::MachineFunction::getRegInfo(), llvm::GCNSubtarget::getRegisterInfo(), llvm::MachineFunction::getSubtarget(), llvm::GCNSubtarget::hasGetPCZeroExtension(), llvm::GCNSubtarget::hasMovB64(), llvm::GCNSubtarget::hasPkMovB32(), llvm::SIRegisterInfo::hasVGPRs(), llvm::Hi, Idx, llvm::RegState::Implicit, llvm::MCInstrDesc::implicit_uses(), llvm::RegState::ImplicitDefine, llvm::SIRegisterInfo::isAGPR(), llvm::MachineOperand::isGlobal(), isInlineConstant(), llvm::GCNSubtarget::isWave32(), llvm::Lo, MBB, MI, llvm::SISrcMods::OP_SEL_0, llvm::SISrcMods::OP_SEL_1, llvm::MachineOperand::setIsUndef(), llvm::MachineOperand::setOffset(), llvm::AMDGPU::VGPRIndexMode::SRC0_ENABLE, SubReg, llvm::MachineInstr::tieOperands(), TRI, llvm::RegState::Undef, and llvm::GCNSubtarget::useVGPRIndexMode().

Referenced by expandPostRAPseudo().

◆ findCommutedOpIndices() [1/2]

|

override |

Definition at line 2772 of file SIInstrInfo.cpp.

References findCommutedOpIndices(), and MI.

Referenced by findCommutedOpIndices().

◆ findCommutedOpIndices() [2/2]

| bool SIInstrInfo::findCommutedOpIndices | ( | const MCInstrDesc & | Desc, |

| unsigned & | SrcOpIdx0, | ||

| unsigned & | SrcOpIdx1 | ||

| ) | const |

Definition at line 2778 of file SIInstrInfo.cpp.

References llvm::AMDGPU::getNamedOperandIdx().

◆ fixImplicitOperands()

| void SIInstrInfo::fixImplicitOperands | ( | MachineInstr & | MI | ) | const |

Definition at line 8960 of file SIInstrInfo.cpp.

References llvm::GCNSubtarget::isWave32(), and MI.

Referenced by buildShrunkInst(), insertBranch(), insertSelect(), legalizeOperandsVOP2(), llvm::GCNSubtarget::mirFileLoaded(), and moveToVALUImpl().

◆ foldImmediate()

|

final |

Definition at line 3354 of file SIInstrInfo.cpp.

References llvm::APInt::ashr(), assert(), llvm::MachineOperand::ChangeToImmediate(), llvm::TargetRegisterClass::contains(), DefMI, llvm::get(), llvm::SIRegisterInfo::get32BitRegister(), llvm::GCNSubtarget::getConstantBusLimit(), llvm::MachineOperand::getImm(), getNamedOperand(), llvm::AMDGPU::getNamedOperandIdx(), getOpSize(), llvm::MachineInstr::getParent(), llvm::MachineOperand::getReg(), llvm::MachineInstrBuilder::getReg(), llvm::SIRegisterInfo::getRegClass(), llvm::APInt::getSExtValue(), llvm::MachineOperand::getSubReg(), hasAnyModifiersSet(), llvm::AMDGPUSubtarget::hasTrue16BitInsts(), llvm::Hi_32(), llvm::SIRegisterInfo::isAGPR(), llvm::MachineOperand::isImm(), isInlineConstant(), llvm::MachineOperand::isKill(), llvm::Register::isPhysical(), llvm::MachineOperand::isReg(), llvm::SIRegisterInfo::isSGPRClass(), llvm::SIRegisterInfo::isSGPRReg(), llvm::SIRegisterInfo::isVGPR(), isVGPRCopy(), llvm::Register::isVirtual(), legalizeOperands(), llvm::Lo_32(), MRI, llvm::MCInstrDesc::operands(), pseudoToMCOpcode(), removeModOperands(), llvm::MachineOperand::setIsKill(), llvm::MachineOperand::setReg(), llvm::MachineOperand::setSubReg(), and UseMI.

Referenced by legalizeGenericOperand().

◆ foldMemoryOperandImpl()

|

override |

Definition at line 9442 of file SIInstrInfo.cpp.

References llvm::MachineFunction::getRegInfo(), llvm::TargetRegisterClass::hasSuperClassEq(), llvm::Register::isVirtual(), MI, and MRI.

◆ getAddNoCarry() [1/2]

| MachineInstrBuilder SIInstrInfo::getAddNoCarry | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock::iterator | I, | ||

| const DebugLoc & | DL, | ||

| Register | DestReg | ||

| ) | const |

Return a partially built integer add instruction without carry.

Caller must add source operands. For pre-GFX9 it will generate unused carry destination operand. TODO: After GFX9 it should return a no-carry operation.

Definition at line 8890 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), llvm::RegState::Dead, llvm::RegState::Define, DL, llvm::get(), llvm::SIRegisterInfo::getBoolRC(), llvm::MachineBasicBlock::getParent(), llvm::MachineFunction::getRegInfo(), llvm::SIRegisterInfo::getVCC(), llvm::GCNSubtarget::hasAddNoCarry(), I, MBB, and MRI.

◆ getAddNoCarry() [2/2]

| MachineInstrBuilder SIInstrInfo::getAddNoCarry | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock::iterator | I, | ||

| const DebugLoc & | DL, | ||

| Register | DestReg, | ||

| RegScavenger & | RS | ||

| ) | const |

Definition at line 8905 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), llvm::RegState::Dead, llvm::RegState::Define, DL, llvm::get(), llvm::SIRegisterInfo::getBoolRC(), llvm::SIRegisterInfo::getVCC(), llvm::GCNSubtarget::hasAddNoCarry(), I, llvm::RegScavenger::isRegUsed(), llvm::Register::isValid(), MBB, and llvm::RegScavenger::scavengeRegisterBackwards().

◆ getBranchDestBlock()

|

override |

Definition at line 2813 of file SIInstrInfo.cpp.

References MI.

◆ getClampMask()

|

inline |

Definition at line 900 of file SIInstrInfo.h.

References llvm::SIInstrFlags::ClampHi, llvm::SIInstrFlags::ClampLo, llvm::SIInstrFlags::FPClamp, llvm::SIInstrFlags::IntClamp, and MI.

◆ getDefaultRsrcDataFormat()

| uint64_t SIInstrInfo::getDefaultRsrcDataFormat | ( | ) | const |

Definition at line 8517 of file SIInstrInfo.cpp.

References llvm::Format, llvm::GCNSubtarget::getGeneration(), llvm::AMDGPUSubtarget::GFX10, llvm::AMDGPUSubtarget::GFX11, llvm::AMDGPUSubtarget::isAmdHsaOS(), llvm::AMDGPU::RSRC_DATA_FORMAT, llvm::AMDGPU::UfmtGFX10::UFMT_32_FLOAT, llvm::AMDGPU::UfmtGFX11::UFMT_32_FLOAT, and llvm::AMDGPUSubtarget::VOLCANIC_ISLANDS.

Referenced by getScratchRsrcWords23().

◆ getDSShaderTypeValue()

|

static |

Definition at line 9630 of file SIInstrInfo.cpp.

References llvm::CallingConv::AMDGPU_CS, llvm::CallingConv::AMDGPU_ES, llvm::CallingConv::AMDGPU_GS, llvm::CallingConv::AMDGPU_HS, llvm::CallingConv::AMDGPU_KERNEL, llvm::CallingConv::AMDGPU_LS, llvm::CallingConv::AMDGPU_PS, llvm::CallingConv::AMDGPU_VS, llvm::CallingConv::C, llvm::CallingConv::Fast, llvm::Function::getCallingConv(), llvm::MachineFunction::getFunction(), and llvm::report_fatal_error().

◆ getGenericInstructionUniformity()

| InstructionUniformity SIInstrInfo::getGenericInstructionUniformity | ( | const MachineInstr & | MI | ) | const |

Definition at line 9497 of file SIInstrInfo.cpp.

References llvm::AlwaysUniform, llvm::any_of(), llvm::Default, llvm::AMDGPU::isGenericAtomic(), llvm::AMDGPU::isIntrinsicAlwaysUniform(), llvm::AMDGPU::isIntrinsicSourceOfDivergence(), MI, and llvm::NeverUniform.

Referenced by getInstructionUniformity().

◆ getIndirectGPRIDXPseudo()

| const MCInstrDesc & SIInstrInfo::getIndirectGPRIDXPseudo | ( | unsigned | VecSize, |

| bool | IsIndirectSrc | ||

| ) | const |

Definition at line 1398 of file SIInstrInfo.cpp.

References llvm::get(), and llvm_unreachable.

◆ getIndirectRegWriteMovRelPseudo()

| const MCInstrDesc & SIInstrInfo::getIndirectRegWriteMovRelPseudo | ( | unsigned | VecSize, |

| unsigned | EltSize, | ||

| bool | IsSGPR | ||

| ) | const |

Definition at line 1531 of file SIInstrInfo.cpp.

References assert(), llvm::get(), getIndirectSGPRWriteMovRelPseudo32(), getIndirectSGPRWriteMovRelPseudo64(), getIndirectVGPRWriteMovRelPseudoOpc(), and llvm_unreachable.

◆ getInstBundleSize()

| unsigned SIInstrInfo::getInstBundleSize | ( | const MachineInstr & | MI | ) | const |

Definition at line 8626 of file SIInstrInfo.cpp.

References assert(), getInstSizeInBytes(), I, MI, and Size.

Referenced by getInstSizeInBytes().

◆ getInstrLatency()

|

override |

Definition at line 9479 of file SIInstrInfo.cpp.

Referenced by llvm::GCNSubtarget::adjustSchedDependency().

◆ getInstructionUniformity()

|

finaloverride |

Definition at line 9546 of file SIInstrInfo.cpp.

References llvm::AlwaysUniform, llvm::any_of(), llvm::Default, getGenericInstructionUniformity(), llvm::RegisterBank::getID(), llvm::SrcOp::getReg(), llvm::MachineOperand::getReg(), llvm::RegisterBankInfo::getRegBank(), llvm::GCNSubtarget::getRegBankInfo(), I, isAtomic(), isFLAT(), isNeverUniform(), llvm::Register::isPhysical(), llvm::MachineOperand::isReg(), llvm::SIRegisterInfo::isSGPRClass(), MI, MRI, and llvm::NeverUniform.

◆ getInstSizeInBytes()

|

override |

Definition at line 8638 of file SIInstrInfo.cpp.

References getInstBundleSize(), llvm::TargetMachine::getMCAsmInfo(), getMCOpcodeFromPseudo(), llvm::AMDGPU::getNamedOperandIdx(), llvm::MachineFunction::getTarget(), llvm::GCNSubtarget::hasOffset3fBug(), I, isDPP(), isFixedSize(), isInlineConstant(), isMIMG(), isSALU(), isVALU(), MI, and Size.

Referenced by llvm::AMDGPUAsmPrinter::emitInstruction(), getInstBundleSize(), and removeBranch().

◆ getKillTerminatorFromPseudo()

| const MCInstrDesc & SIInstrInfo::getKillTerminatorFromPseudo | ( | unsigned | Opcode | ) | const |

Definition at line 8938 of file SIInstrInfo.cpp.

References llvm::get(), and llvm_unreachable.

◆ getLiveRangeSplitOpcode()

|

override |

Definition at line 8857 of file SIInstrInfo.cpp.

References assert(), llvm::SIMachineFunctionInfo::checkFlag(), llvm::MachineFunction::getInfo(), llvm::Register::isVirtual(), and llvm::AMDGPU::VirtRegFlag::WWM_REG.

◆ getMachineCSELookAheadLimit()

|

inlineoverride |

Definition at line 399 of file SIInstrInfo.h.

◆ getMaxMUBUFImmOffset()

|

static |

Definition at line 8953 of file SIInstrInfo.cpp.

References llvm::AMDGPUSubtarget::GFX12.

Referenced by isLegalMUBUFImmOffset(), llvm::AMDGPURegisterBankInfo::splitBufferOffsets(), llvm::AMDGPULegalizerInfo::splitBufferOffsets(), and splitMUBUFOffset().

◆ getMCOpcodeFromPseudo()

|

inline |

Return the descriptor of the target-specific machine instruction that corresponds to the specified pseudo or native opcode.

Definition at line 1226 of file SIInstrInfo.h.

References llvm::get(), and pseudoToMCOpcode().

Referenced by getInstSizeInBytes().

◆ getMemOperandsWithOffsetWidth()

|

final |

Definition at line 361 of file SIInstrInfo.cpp.

References assert(), llvm::MachineOperand::getImm(), getNamedOperand(), llvm::AMDGPU::getNamedOperandIdx(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), getOpRegClass(), getOpSize(), llvm::LocationSize::getValue(), I, isDS(), llvm::MachineOperand::isFI(), isFLAT(), isMIMG(), isMTBUF(), isMUBUF(), llvm::MachineOperand::isReg(), isSMRD(), isStride64(), llvm::MachineInstr::mayLoad(), llvm::MachineInstr::mayLoadOrStore(), llvm::MachineInstr::mayStore(), llvm::Offset, llvm::SmallVectorTemplateBase< T, bool >::push_back(), and TRI.

◆ getMIRFormatter()

|

inlineoverride |

Definition at line 1366 of file SIInstrInfo.h.

◆ getMovOpcode()

| unsigned SIInstrInfo::getMovOpcode | ( | const TargetRegisterClass * | DstRC | ) | const |

Definition at line 1379 of file SIInstrInfo.cpp.

References llvm::SIRegisterInfo::isAGPRClass(), and llvm::SIRegisterInfo::isSGPRClass().

◆ getNamedImmOperand()

|

inline |

Get required immediate operand.

Definition at line 1213 of file SIInstrInfo.h.

References llvm::AMDGPU::getNamedOperandIdx(), Idx, and MI.

Referenced by legalizeOperands().

◆ getNamedOperand() [1/2]

|

inline |

Definition at line 1207 of file SIInstrInfo.h.

References getNamedOperand(), and MI.

◆ getNamedOperand() [2/2]

| MachineOperand * SIInstrInfo::getNamedOperand | ( | MachineInstr & | MI, |

| unsigned | OperandName | ||

| ) | const |

Returns the operand named Op.

If MI does not have an operand named Op, this function returns nullptr.

Definition at line 8508 of file SIInstrInfo.cpp.

References llvm::AMDGPU::getNamedOperandIdx(), Idx, and MI.

Referenced by buildShrunkInst(), canShrink(), convertToThreeAddress(), expandMovDPP64(), foldImmediate(), getMemOperandsWithOffsetWidth(), getNamedOperand(), hasModifiersSet(), isSGPRStackAccess(), isStackAccess(), legalizeOperands(), legalizeOperandsFLAT(), legalizeOperandsSMRD(), reMaterialize(), swapSourceModifiers(), and verifyInstruction().

◆ getNonSoftWaitcntOpcode()

Definition at line 936 of file SIInstrInfo.h.

Referenced by isWaitInstr(), and pseudoToMCOpcode().

◆ getNumWaitStates()

|

static |

Return the number of wait states that result from executing this instruction.

Definition at line 2029 of file SIInstrInfo.cpp.

References MI.

Referenced by llvm::GCNHazardRecognizer::AdvanceCycle().

◆ getOpRegClass()

| const TargetRegisterClass * SIInstrInfo::getOpRegClass | ( | const MachineInstr & | MI, |

| unsigned | OpNo | ||

| ) | const |

Return the correct register class for OpNo.

For target-specific instructions, this will return the register class that has been defined in tablegen. For generic instructions, like REG_SEQUENCE it will return the register class of its machine operand. to infer the correct register class base on the other operands.

Definition at line 5555 of file SIInstrInfo.cpp.

References adjustAllocatableRegClass(), llvm::get(), MI, and MRI.

Referenced by expandPostRAPseudo(), getMemOperandsWithOffsetWidth(), getOpSize(), legalizeOperands(), and verifyInstruction().

◆ getOpSize() [1/2]

|

inline |

This form should usually be preferred since it handles operands with unknown register classes.

Definition at line 1108 of file SIInstrInfo.h.

References getOpRegClass(), llvm::MachineOperand::getSubReg(), llvm::MachineOperand::isReg(), MI, and SubReg.

◆ getOpSize() [2/2]

Return the size in bytes of the operand OpNo on the given.

Definition at line 1094 of file SIInstrInfo.h.

References assert(), llvm::get(), llvm::SIRegisterInfo::getRegClass(), llvm::MCOI::OPERAND_IMMEDIATE, llvm::MCOperandInfo::OperandType, and llvm::MCOperandInfo::RegClass.

Referenced by enforceOperandRCAlignment(), foldImmediate(), getMemOperandsWithOffsetWidth(), isInlineConstant(), and verifyInstruction().

◆ getPreferredSelectRegClass()

| const TargetRegisterClass * SIInstrInfo::getPreferredSelectRegClass | ( | unsigned | Size | ) | const |

Definition at line 1223 of file SIInstrInfo.cpp.

◆ getRegClass()

|

override |

Definition at line 5525 of file SIInstrInfo.cpp.

References adjustAllocatableRegClass(), llvm::SIInstrFlags::DS, llvm::SIInstrFlags::FLAT, llvm::AMDGPU::getNamedOperandIdx(), llvm::MCInstrDesc::getNumOperands(), llvm::MachineFunction::getRegInfo(), llvm::AMDGPU::hasNamedOperand(), llvm::MCInstrDesc::Opcode, llvm::MCInstrDesc::operands(), and llvm::MCInstrDesc::TSFlags.

Referenced by reMaterialize().

◆ getRegisterInfo()

|

inline |

Definition at line 222 of file SIInstrInfo.h.

Referenced by llvm::GCNSubtarget::getRegisterInfo(), and llvm::PhiLoweringHelper::isLaneMaskReg().

◆ getSchedModel()

|

inline |

Definition at line 1374 of file SIInstrInfo.h.

Referenced by llvm::GCNSubtarget::adjustSchedDependency(), and llvm::GCNSchedStage::getScheduleMetrics().

◆ getScratchRsrcWords23()

| uint64_t SIInstrInfo::getScratchRsrcWords23 | ( | ) | const |

Definition at line 8542 of file SIInstrInfo.cpp.

References getDefaultRsrcDataFormat(), llvm::GCNSubtarget::getGeneration(), llvm::GCNSubtarget::getMaxPrivateElementSize(), llvm::AMDGPUSubtarget::getWavefrontSize(), llvm::AMDGPUSubtarget::GFX9, llvm::Log2_32(), llvm::AMDGPU::RSRC_ELEMENT_SIZE_SHIFT, llvm::AMDGPU::RSRC_INDEX_STRIDE_SHIFT, llvm::AMDGPU::RSRC_TID_ENABLE, and llvm::AMDGPUSubtarget::VOLCANIC_ISLANDS.

◆ getSerializableDirectMachineOperandTargetFlags()

|

override |

Definition at line 8832 of file SIInstrInfo.cpp.

References MO_ABS32_HI, MO_ABS32_LO, MO_GOTPCREL, MO_GOTPCREL32_HI, MO_GOTPCREL32_LO, MO_REL32_HI, and MO_REL32_LO.

◆ getSerializableMachineMemOperandTargetFlags()

|

override |

Definition at line 8847 of file SIInstrInfo.cpp.

References llvm::MOLastUse, and llvm::MONoClobber.

◆ getSerializableTargetIndices()

|

override |

Definition at line 8787 of file SIInstrInfo.cpp.

References llvm::AMDGPU::TI_CONSTDATA_START, llvm::AMDGPU::TI_SCRATCH_RSRC_DWORD0, llvm::AMDGPU::TI_SCRATCH_RSRC_DWORD1, llvm::AMDGPU::TI_SCRATCH_RSRC_DWORD2, and llvm::AMDGPU::TI_SCRATCH_RSRC_DWORD3.

◆ getSubtarget()

|

inline |

Definition at line 226 of file SIInstrInfo.h.

◆ getVALUOp()

| unsigned SIInstrInfo::getVALUOp | ( | const MachineInstr & | MI | ) | const |

Definition at line 5283 of file SIInstrInfo.cpp.

References llvm::GCNSubtarget::hasAddNoCarry(), llvm::GCNSubtarget::hasDLInsts(), llvm::SIRegisterInfo::isAGPR(), llvm_unreachable, MI, MRI, and llvm::AMDGPUSubtarget::useRealTrue16Insts().

Referenced by moveToVALUImpl().

◆ hasAnyModifiersSet()

| bool SIInstrInfo::hasAnyModifiersSet | ( | const MachineInstr & | MI | ) | const |

Definition at line 4352 of file SIInstrInfo.cpp.

References llvm::any_of(), hasModifiersSet(), MI, ModifierOpNames, and Name.

Referenced by foldImmediate().

◆ hasDivergentBranch()

| bool SIInstrInfo::hasDivergentBranch | ( | const MachineBasicBlock * | MBB | ) | const |

Return whether the block terminate with divergent branch.

Note this only work before lowering the pseudo control flow instructions.

Definition at line 2817 of file SIInstrInfo.cpp.

References MBB, MI, and llvm::MachineBasicBlock::terminators().

Referenced by isSafeToSink().

◆ hasFPClamp() [1/2]

|

inlinestatic |

Definition at line 888 of file SIInstrInfo.h.

References llvm::SIInstrFlags::FPClamp, and MI.

◆ hasFPClamp() [2/2]

Definition at line 892 of file SIInstrInfo.h.

References llvm::SIInstrFlags::FPClamp, and llvm::get().

◆ hasIntClamp()

|

inlinestatic |

Definition at line 896 of file SIInstrInfo.h.

References llvm::SIInstrFlags::IntClamp, and MI.

◆ hasModifiers()

Return true if this instruction has any modifiers.

e.g. src[012]_mod, omod, clamp.

Definition at line 4339 of file SIInstrInfo.cpp.

References llvm::AMDGPU::hasNamedOperand().

◆ hasModifiersSet()

| bool SIInstrInfo::hasModifiersSet | ( | const MachineInstr & | MI, |

| unsigned | OpName | ||

| ) | const |

Definition at line 4346 of file SIInstrInfo.cpp.

References llvm::MachineOperand::getImm(), getNamedOperand(), and MI.

Referenced by canShrink(), and hasAnyModifiersSet().

◆ hasUnwantedEffectsWhenEXECEmpty()

| bool SIInstrInfo::hasUnwantedEffectsWhenEXECEmpty | ( | const MachineInstr & | MI | ) | const |

Whether we must prevent this instruction from executing with EXEC = 0.

Definition at line 4064 of file SIInstrInfo.cpp.

References isEXP(), isSMRD(), MI, and modifiesModeRegister().

◆ hasVALU32BitEncoding()

Return true if this 64-bit VALU instruction has a 32-bit encoding.

This function will return false if you pass it a 32-bit instruction.

Definition at line 4327 of file SIInstrInfo.cpp.

References llvm::AMDGPU::getVOPe32(), llvm::GCNSubtarget::hasGFX90AInsts(), and pseudoToMCOpcode().

Referenced by canShrink().

◆ hasVGPRUses()

|

inline |

Definition at line 967 of file SIInstrInfo.h.

References llvm::any_of(), llvm::MachineFunction::getRegInfo(), MI, and MRI.

◆ insertBranch()

|

override |

Definition at line 3097 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::add(), llvm::MachineInstrBuilder::addMBB(), assert(), llvm::BuildMI(), Cond, DL, fixImplicitOperands(), llvm::get(), llvm::MachineInstr::getOperand(), llvm::GCNSubtarget::hasOffset3fBug(), isImm(), isUndef(), MBB, preserveCondRegFlags(), llvm::MachineOperand::setIsKill(), llvm::MachineOperand::setIsUndef(), and TBB.

◆ insertEQ()

| Register SIInstrInfo::insertEQ | ( | MachineBasicBlock * | MBB, |

| MachineBasicBlock::iterator | I, | ||

| const DebugLoc & | DL, | ||

| Register | SrcReg, | ||

| int | Value | ||

| ) | const |

Definition at line 1353 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), DL, llvm::get(), llvm::SIRegisterInfo::getBoolRC(), llvm::MachineBasicBlock::getParent(), llvm::MachineFunction::getRegInfo(), I, MBB, and MRI.

◆ insertIndirectBranch()

|

override |

Definition at line 2827 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addReg(), llvm::MachineInstrBuilder::addSym(), assert(), llvm::BuildMI(), llvm::MCSymbolRefExpr::create(), llvm::MCConstantExpr::create(), llvm::MCBinaryExpr::createAnd(), llvm::MCBinaryExpr::createAShr(), llvm::MCBinaryExpr::createSub(), llvm::RegState::Define, DL, llvm::MachineBasicBlock::empty(), llvm::MachineBasicBlock::end(), llvm::RegScavenger::enterBasicBlock(), llvm::RegScavenger::enterBasicBlockEnd(), llvm::get(), llvm::MachineFunction::getContext(), llvm::MachineFunction::getInfo(), llvm::SIMachineFunctionInfo::getLongBranchReservedReg(), llvm::MachineBasicBlock::getParent(), llvm::MachineFunction::getRegInfo(), llvm::MachineFunction::getSubtarget(), llvm::MachineBasicBlock::getSymbol(), I, MBB, MO_FAR_BRANCH_OFFSET, MRI, llvm::Offset, llvm::MachineBasicBlock::pred_size(), llvm::RegScavenger::scavengeRegisterBackwards(), llvm::MachineInstr::setPostInstrSymbol(), llvm::RegScavenger::setRegUsed(), llvm::MCSymbol::setVariableValue(), and TRI.

◆ insertNE()

| Register SIInstrInfo::insertNE | ( | MachineBasicBlock * | MBB, |

| MachineBasicBlock::iterator | I, | ||

| const DebugLoc & | DL, | ||

| Register | SrcReg, | ||

| int | Value | ||

| ) | const |

Definition at line 1366 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), DL, llvm::get(), llvm::SIRegisterInfo::getBoolRC(), llvm::MachineBasicBlock::getParent(), llvm::MachineFunction::getRegInfo(), I, MBB, and MRI.

◆ insertNoop()

|

override |

Definition at line 1995 of file SIInstrInfo.cpp.

References insertNoops(), MBB, and MI.

◆ insertNoops()

|

override |

Definition at line 2000 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::BuildMI(), DL, llvm::MachineBasicBlock::findDebugLoc(), llvm::get(), MBB, and MI.

Referenced by insertNoop().

◆ insertReturn()

| void SIInstrInfo::insertReturn | ( | MachineBasicBlock & | MBB | ) | const |

Definition at line 2011 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), assert(), llvm::BuildMI(), llvm::MachineBasicBlock::end(), llvm::get(), llvm::MachineBasicBlock::getFirstTerminator(), llvm::MachineBasicBlock::getParent(), Info, MBB, and llvm::MachineBasicBlock::succ_empty().

◆ insertScratchExecCopy()

| void SIInstrInfo::insertScratchExecCopy | ( | MachineFunction & | MF, |

| MachineBasicBlock & | MBB, | ||

| MachineBasicBlock::iterator | MBBI, | ||

| const DebugLoc & | DL, | ||

| Register | Reg, | ||

| bool | IsSCCLive, | ||

| SlotIndexes * | Indexes = nullptr |

||

| ) | const |

Definition at line 5444 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), DL, llvm::MachineInstr::getOperand(), llvm::MachineFunction::getSubtarget(), llvm::SlotIndexes::insertMachineInstrInMaps(), llvm::RegState::Kill, MBB, MBBI, llvm::MachineOperand::setIsDead(), and TII.

◆ insertSelect()

|

override |

Definition at line 3212 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), Cond, DL, fixImplicitOperands(), llvm::get(), llvm::ilist_node_impl< OptionsT >::getIterator(), llvm::MachineBasicBlock::getParent(), llvm::MachineFunction::getRegInfo(), I, Idx, MBB, MRI, preserveCondRegFlags(), llvm::SmallVectorTemplateBase< T, bool >::push_back(), Select, and std::swap().

◆ insertVectorSelect()

| void SIInstrInfo::insertVectorSelect | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock::iterator | I, | ||

| const DebugLoc & | DL, | ||

| Register | DstReg, | ||

| ArrayRef< MachineOperand > | Cond, | ||

| Register | TrueReg, | ||

| Register | FalseReg | ||

| ) | const |

Definition at line 1227 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::add(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), assert(), llvm::BuildMI(), Cond, DL, llvm::get(), llvm::SIRegisterInfo::getBoolRC(), llvm::MachineBasicBlock::getParent(), llvm::SIRegisterInfo::getRegClass(), llvm::MachineFunction::getRegInfo(), I, isImm(), llvm::GCNSubtarget::isWave32(), llvm_unreachable, MBB, MRI, and llvm::MachineOperand::setImplicit().

◆ isAlwaysGDS()

Definition at line 4053 of file SIInstrInfo.cpp.

References isGWS().

◆ isAsmOnlyOpcode()

| bool SIInstrInfo::isAsmOnlyOpcode | ( | int | MCOp | ) | const |

Check if this instruction should only be used by assembler.

Return true if this opcode should not be used by codegen.

Definition at line 9152 of file SIInstrInfo.cpp.

Referenced by pseudoToMCOpcode().

◆ isAtomic() [1/2]

|

inlinestatic |

Definition at line 681 of file SIInstrInfo.h.

References llvm::SIInstrFlags::IsAtomicNoRet, llvm::SIInstrFlags::IsAtomicRet, and MI.

Referenced by getInstructionUniformity(), and isValidClauseInst().

◆ isAtomic() [2/2]

Definition at line 686 of file SIInstrInfo.h.

References llvm::get(), llvm::SIInstrFlags::IsAtomicNoRet, and llvm::SIInstrFlags::IsAtomicRet.

◆ isAtomicNoRet() [1/2]

|

inlinestatic |

Definition at line 665 of file SIInstrInfo.h.

References llvm::SIInstrFlags::IsAtomicNoRet, and MI.

◆ isAtomicNoRet() [2/2]

Definition at line 669 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::IsAtomicNoRet.

◆ isAtomicRet() [1/2]

|

inlinestatic |

Definition at line 673 of file SIInstrInfo.h.

References llvm::SIInstrFlags::IsAtomicRet, and MI.

◆ isAtomicRet() [2/2]

Definition at line 677 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::IsAtomicRet.

◆ isBasicBlockPrologue()

|

override |

Definition at line 8867 of file SIInstrInfo.cpp.

References llvm::SIRegisterInfo::getRegClassForReg(), llvm::SIRegisterInfo::isSGPRClass(), isSpill(), MI, and MRI.

◆ isBranchOffsetInRange()

Definition at line 2796 of file SIInstrInfo.cpp.

References assert(), BranchOffsetBits, and llvm::isIntN().

◆ isBufferSMRD()

| bool SIInstrInfo::isBufferSMRD | ( | const MachineInstr & | MI | ) | const |

Definition at line 8973 of file SIInstrInfo.cpp.

References llvm::AMDGPU::getNamedOperandIdx(), llvm::SIRegisterInfo::getRegClass(), llvm::TargetRegisterClass::hasSubClassEq(), Idx, isSMRD(), and MI.

◆ isChainCallOpcode()

Definition at line 755 of file SIInstrInfo.h.

◆ isCopyInstrImpl()

|

overrideprotected |

If the specific machine instruction is a instruction that moves/copies value from one register to another register return destination and source registers as machine operands.

Definition at line 2660 of file SIInstrInfo.cpp.

References MI.

◆ isDisableWQM() [1/2]

|

inlinestatic |

Definition at line 703 of file SIInstrInfo.h.

References llvm::SIInstrFlags::DisableWQM, and MI.

◆ isDisableWQM() [2/2]

Definition at line 707 of file SIInstrInfo.h.

References llvm::SIInstrFlags::DisableWQM, and llvm::get().

◆ isDOT() [1/2]

|

inlinestatic |

Definition at line 805 of file SIInstrInfo.h.

References llvm::SIInstrFlags::IsDOT, and MI.

◆ isDOT() [2/2]

Definition at line 829 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::IsDOT.

◆ isDPP() [1/2]

|

inlinestatic |

Definition at line 760 of file SIInstrInfo.h.

References llvm::SIInstrFlags::DPP, and MI.

Referenced by llvm::GCNHazardRecognizer::getHazardType(), getInstSizeInBytes(), and llvm::GCNHazardRecognizer::PreEmitNoopsCommon().

◆ isDPP() [2/2]

Definition at line 764 of file SIInstrInfo.h.

References llvm::SIInstrFlags::DPP, and llvm::get().

◆ isDS() [1/2]

|

inlinestatic |

Definition at line 554 of file SIInstrInfo.h.

References llvm::SIInstrFlags::DS, and MI.

Referenced by areLoadsFromSameBasePtr(), areMemAccessesTriviallyDisjoint(), llvm::GCNHazardRecognizer::getHazardType(), getMemOperandsWithOffsetWidth(), isOperandLegal(), llvm::GCNHazardRecognizer::PreEmitNoopsCommon(), shouldRunLdsBranchVmemWARHazardFixup(), and verifyInstruction().

◆ isDS() [2/2]

Definition at line 558 of file SIInstrInfo.h.

References llvm::SIInstrFlags::DS, and llvm::get().

◆ isDualSourceBlendEXP()

|

inlinestatic |

Definition at line 653 of file SIInstrInfo.h.

References llvm::AMDGPU::Exp::ET_DUAL_SRC_BLEND0, llvm::AMDGPU::Exp::ET_DUAL_SRC_BLEND1, isEXP(), and MI.

◆ isEXP() [1/2]

|

inlinestatic |

Definition at line 649 of file SIInstrInfo.h.

References llvm::SIInstrFlags::EXP, and MI.

Referenced by llvm::GCNHazardRecognizer::getHazardType(), hasUnwantedEffectsWhenEXECEmpty(), isDualSourceBlendEXP(), and llvm::GCNHazardRecognizer::PreEmitNoopsCommon().

◆ isEXP() [2/2]

Definition at line 661 of file SIInstrInfo.h.

References llvm::SIInstrFlags::EXP, and llvm::get().

◆ isFixedSize() [1/2]

|

inlinestatic |

Definition at line 880 of file SIInstrInfo.h.

References llvm::SIInstrFlags::FIXED_SIZE, and MI.

Referenced by getInstSizeInBytes().

◆ isFixedSize() [2/2]

Definition at line 884 of file SIInstrInfo.h.

References llvm::SIInstrFlags::FIXED_SIZE, and llvm::get().

◆ isFLAT() [1/2]

|

inlinestatic |

Definition at line 612 of file SIInstrInfo.h.

References llvm::SIInstrFlags::FLAT, and MI.

Referenced by areMemAccessesTriviallyDisjoint(), breaksVMEMSoftClause(), llvm::GCNHazardRecognizer::getHazardType(), getInstructionUniformity(), getMemOperandsWithOffsetWidth(), isHighLatencyDef(), isLdsDma(), isLDSDMA(), isVMEMClauseInst(), legalizeOperands(), mayAccessFlatAddressSpace(), llvm::GCNHazardRecognizer::PreEmitNoopsCommon(), and verifyInstruction().

◆ isFLAT() [2/2]

Definition at line 645 of file SIInstrInfo.h.

References llvm::SIInstrFlags::FLAT, and llvm::get().

◆ isFLATGlobal() [1/2]

|

inlinestatic |

Definition at line 628 of file SIInstrInfo.h.

References llvm::SIInstrFlags::FlatGlobal, and MI.

Referenced by areMemAccessesTriviallyDisjoint().

◆ isFLATGlobal() [2/2]

Definition at line 632 of file SIInstrInfo.h.

References llvm::SIInstrFlags::FlatGlobal, and llvm::get().

◆ isFLATScratch() [1/2]

|

inlinestatic |

Definition at line 636 of file SIInstrInfo.h.

References llvm::SIInstrFlags::FlatScratch, and MI.

Referenced by areMemAccessesTriviallyDisjoint(), llvm::SIRegisterInfo::getFrameIndexInstrOffset(), llvm::SIRegisterInfo::getScratchInstrOffset(), llvm::SIRegisterInfo::isFrameOffsetLegal(), and llvm::SIRegisterInfo::needsFrameBaseReg().

◆ isFLATScratch() [2/2]

Definition at line 640 of file SIInstrInfo.h.

References llvm::SIInstrFlags::FlatScratch, and llvm::get().

◆ isFoldableCopy()

|

static |

◆ isFPAtomic() [1/2]

|

inlinestatic |

Definition at line 916 of file SIInstrInfo.h.

References llvm::SIInstrFlags::FPAtomic, and MI.

◆ isFPAtomic() [2/2]

Definition at line 920 of file SIInstrInfo.h.

References llvm::SIInstrFlags::FPAtomic, and llvm::get().

◆ isGather4() [1/2]

|

inlinestatic |

Definition at line 604 of file SIInstrInfo.h.

References llvm::SIInstrFlags::Gather4, and MI.

Referenced by verifyInstruction().

◆ isGather4() [2/2]

Definition at line 608 of file SIInstrInfo.h.

References llvm::SIInstrFlags::Gather4, and llvm::get().

◆ isGWS() [1/2]

|

inlinestatic |

Definition at line 570 of file SIInstrInfo.h.

References llvm::SIInstrFlags::GWS, and MI.

Referenced by isAlwaysGDS().

◆ isGWS() [2/2]

Definition at line 574 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::GWS.

◆ isHighLatencyDef()

|

override |

Definition at line 8572 of file SIInstrInfo.cpp.

References llvm::get(), isFLAT(), isMIMG(), isMTBUF(), and isMUBUF().

Referenced by llvm::SIScheduleDAGMI::schedule().

◆ isIgnorableUse()

|

override |

Definition at line 187 of file SIInstrInfo.cpp.

References llvm::MachineOperand::getParent(), llvm::MachineOperand::getReg(), llvm::MachineOperand::isImplicit(), isVALU(), and resultDependsOnExec().

◆ isImage() [1/2]

|

inlinestatic |

Definition at line 424 of file SIInstrInfo.h.

References isMIMG(), isVIMAGE(), isVSAMPLE(), and MI.

Referenced by isVMEM(), legalizeOperands(), and verifyInstruction().

◆ isImage() [2/2]

Definition at line 428 of file SIInstrInfo.h.

References isMIMG(), isVIMAGE(), and isVSAMPLE().

◆ isImmOperandLegal()

| bool SIInstrInfo::isImmOperandLegal | ( | const MachineInstr & | MI, |

| unsigned | OpNo, | ||

| const MachineOperand & | MO | ||

| ) | const |

Definition at line 4297 of file SIInstrInfo.cpp.

References assert(), llvm::AMDGPU::getNamedOperandIdx(), llvm::GCNSubtarget::hasMFMAInlineLiteralBug(), llvm::GCNSubtarget::hasVOP3Literal(), llvm::MachineOperand::isFI(), llvm::MachineOperand::isGlobal(), llvm::MachineOperand::isImm(), isInlineConstant(), isMAI(), llvm::AMDGPU::isSISrcOperand(), llvm::MachineOperand::isTargetIndex(), isVOP3(), MI, llvm::SIRegisterInfo::opCanUseInlineConstant(), llvm::SIRegisterInfo::opCanUseLiteralConstant(), llvm::MCOI::OPERAND_IMMEDIATE, llvm::MCInstrDesc::operands(), llvm::MCOperandInfo::OperandType, and llvm::MCOperandInfo::RegClass.

Referenced by isOperandLegal().

◆ isInlineConstant() [1/8]

Definition at line 4152 of file SIInstrInfo.cpp.

References llvm::APInt::getSExtValue(), llvm::AMDGPUSubtarget::has16BitInsts(), llvm::AMDGPUSubtarget::hasInv2PiInlineImm(), llvm::AMDGPU::isInlinableLiteralBF16(), llvm::AMDGPU::isInlinableLiteralFP16(), isInlineConstant(), llvm_unreachable, llvm::APFloatBase::S_BFloat, llvm::APFloatBase::S_IEEEdouble, llvm::APFloatBase::S_IEEEhalf, llvm::APFloatBase::S_IEEEsingle, and llvm::APFloatBase::SemanticsToEnum().

◆ isInlineConstant() [2/8]

Definition at line 4132 of file SIInstrInfo.cpp.

References llvm::AMDGPUSubtarget::has16BitInsts(), llvm::AMDGPUSubtarget::hasInv2PiInlineImm(), llvm::AMDGPU::isInlinableLiteral32(), llvm::AMDGPU::isInlinableLiteral64(), llvm::AMDGPU::isInlinableLiteralI16(), and llvm_unreachable.

Referenced by convertToThreeAddress(), expandPostRAPseudo(), foldImmediate(), getInstSizeInBytes(), isImmOperandLegal(), isInlineConstant(), isOperandLegal(), legalizeOperandsVOP3(), usesConstantBus(), and verifyInstruction().

◆ isInlineConstant() [3/8]

|

inline |

returns true if UseMO is substituted with DefMO in MI it would be an inline immediate.

Definition at line 1005 of file SIInstrInfo.h.

References assert(), llvm::MachineOperand::getOperandNo(), llvm::MachineOperand::getParent(), isInlineConstant(), and MI.

◆ isInlineConstant() [4/8]

|

inline |

returns true if the operand OpIdx in MI is a valid inline immediate.

Definition at line 1018 of file SIInstrInfo.h.

References isInlineConstant(), and MI.

◆ isInlineConstant() [5/8]

|

inline |

Definition at line 1023 of file SIInstrInfo.h.

References assert(), getOpSize(), isInlineConstant(), MI, llvm::AMDGPU::OPERAND_REG_IMM_INT32, llvm::AMDGPU::OPERAND_REG_IMM_INT64, and Size.

◆ isInlineConstant() [6/8]

|

inline |

Definition at line 1040 of file SIInstrInfo.h.

References llvm::MachineOperand::getOperandNo(), llvm::MachineOperand::getParent(), and isInlineConstant().

◆ isInlineConstant() [7/8]

|

inline |

Definition at line 998 of file SIInstrInfo.h.

References isInlineConstant(), and llvm::MCOperandInfo::OperandType.

◆ isInlineConstant() [8/8]

| bool SIInstrInfo::isInlineConstant | ( | const MachineOperand & | MO, |

| uint8_t | OperandType | ||

| ) | const |

Definition at line 4171 of file SIInstrInfo.cpp.

References assert(), llvm::MachineOperand::getImm(), llvm::AMDGPUSubtarget::has16BitInsts(), llvm::AMDGPUSubtarget::hasInv2PiInlineImm(), llvm::MachineOperand::isImm(), llvm::AMDGPU::isInlinableIntLiteral(), llvm::AMDGPU::isInlinableLiteral32(), llvm::AMDGPU::isInlinableLiteral64(), llvm::AMDGPU::isInlinableLiteralBF16(), llvm::AMDGPU::isInlinableLiteralFP16(), llvm::AMDGPU::isInlinableLiteralV2BF16(), llvm::AMDGPU::isInlinableLiteralV2F16(), llvm::AMDGPU::isInlinableLiteralV2I16(), llvm::MachineOperand::isReg(), llvm_unreachable, llvm::MCOI::OPERAND_GENERIC_0, llvm::MCOI::OPERAND_GENERIC_1, llvm::MCOI::OPERAND_GENERIC_2, llvm::MCOI::OPERAND_GENERIC_3, llvm::MCOI::OPERAND_GENERIC_4, llvm::MCOI::OPERAND_GENERIC_5, llvm::MCOI::OPERAND_IMMEDIATE, llvm::AMDGPU::OPERAND_INLINE_SPLIT_BARRIER_INT32, llvm::AMDGPU::OPERAND_INPUT_MODS, llvm::AMDGPU::OPERAND_KIMM16, llvm::AMDGPU::OPERAND_KIMM32, llvm::MCOI::OPERAND_PCREL, llvm::AMDGPU::OPERAND_REG_IMM_BF16, llvm::AMDGPU::OPERAND_REG_IMM_BF16_DEFERRED, llvm::AMDGPU::OPERAND_REG_IMM_FP16, llvm::AMDGPU::OPERAND_REG_IMM_FP16_DEFERRED, llvm::AMDGPU::OPERAND_REG_IMM_FP32, llvm::AMDGPU::OPERAND_REG_IMM_FP32_DEFERRED, llvm::AMDGPU::OPERAND_REG_IMM_FP64, llvm::AMDGPU::OPERAND_REG_IMM_INT16, llvm::AMDGPU::OPERAND_REG_IMM_INT32, llvm::AMDGPU::OPERAND_REG_IMM_INT64, llvm::AMDGPU::OPERAND_REG_IMM_V2BF16, llvm::AMDGPU::OPERAND_REG_IMM_V2FP16, llvm::AMDGPU::OPERAND_REG_IMM_V2FP32, llvm::AMDGPU::OPERAND_REG_IMM_V2INT16, llvm::AMDGPU::OPERAND_REG_IMM_V2INT32, llvm::AMDGPU::OPERAND_REG_INLINE_AC_BF16, llvm::AMDGPU::OPERAND_REG_INLINE_AC_FP16, llvm::AMDGPU::OPERAND_REG_INLINE_AC_FP32, llvm::AMDGPU::OPERAND_REG_INLINE_AC_FP64, llvm::AMDGPU::OPERAND_REG_INLINE_AC_INT16, llvm::AMDGPU::OPERAND_REG_INLINE_AC_INT32, llvm::AMDGPU::OPERAND_REG_INLINE_AC_V2BF16, llvm::AMDGPU::OPERAND_REG_INLINE_AC_V2FP16, llvm::AMDGPU::OPERAND_REG_INLINE_AC_V2INT16, llvm::AMDGPU::OPERAND_REG_INLINE_C_BF16, llvm::AMDGPU::OPERAND_REG_INLINE_C_FP16, llvm::AMDGPU::OPERAND_REG_INLINE_C_FP32, llvm::AMDGPU::OPERAND_REG_INLINE_C_FP64, llvm::AMDGPU::OPERAND_REG_INLINE_C_INT16, llvm::AMDGPU::OPERAND_REG_INLINE_C_INT32, llvm::AMDGPU::OPERAND_REG_INLINE_C_INT64, llvm::AMDGPU::OPERAND_REG_INLINE_C_V2BF16, llvm::AMDGPU::OPERAND_REG_INLINE_C_V2FP16, llvm::AMDGPU::OPERAND_REG_INLINE_C_V2FP32, llvm::AMDGPU::OPERAND_REG_INLINE_C_V2INT16, llvm::AMDGPU::OPERAND_REG_INLINE_C_V2INT32, llvm::MCOI::OPERAND_REGISTER, and llvm::MCOI::OPERAND_UNKNOWN.

◆ isKillTerminator()

Definition at line 8928 of file SIInstrInfo.cpp.

◆ isLDSDIR() [1/2]

|

inlinestatic |

Definition at line 833 of file SIInstrInfo.h.

References llvm::SIInstrFlags::LDSDIR, and MI.

◆ isLDSDIR() [2/2]

Definition at line 837 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::LDSDIR.

◆ isLDSDMA() [1/2]

|

inlinestatic |

Definition at line 562 of file SIInstrInfo.h.

References isFLAT(), isMUBUF(), isVALU(), and MI.

Referenced by areMemAccessesTriviallyDisjoint(), and mayWriteLDSThroughDMA().

◆ isLDSDMA() [2/2]

Definition at line 566 of file SIInstrInfo.h.

◆ isLegalFLATOffset()

| bool SIInstrInfo::isLegalFLATOffset | ( | int64_t | Offset, |

| unsigned | AddrSpace, | ||

| uint64_t | FlatVariant | ||

| ) | const |

Returns if Offset is legal for the subtarget as the offset to a FLAT encoded instruction.

If Signed, this is for an instruction that interprets the offset as signed.

Definition at line 9069 of file SIInstrInfo.cpp.

References allowNegativeFlatOffset(), llvm::SIInstrFlags::FLAT, llvm::AMDGPUAS::FLAT_ADDRESS, llvm::SIInstrFlags::FlatScratch, llvm::AMDGPU::getNumFlatOffsetBits(), llvm::AMDGPUAS::GLOBAL_ADDRESS, llvm::GCNSubtarget::hasFlatInstOffsets(), llvm::GCNSubtarget::hasFlatSegmentOffsetBug(), llvm::GCNSubtarget::hasNegativeUnalignedScratchOffsetBug(), llvm::isIntN(), N, and llvm::Offset.

Referenced by splitFlatOffset().

◆ isLegalMUBUFImmOffset()

Definition at line 8949 of file SIInstrInfo.cpp.

References getMaxMUBUFImmOffset().

◆ isLegalRegOperand()

| bool SIInstrInfo::isLegalRegOperand | ( | const MachineRegisterInfo & | MRI, |

| const MCOperandInfo & | OpInfo, | ||

| const MachineOperand & | MO | ||

| ) | const |

Check if MO (a register operand) is a legal register for the given operand description.

Definition at line 5648 of file SIInstrInfo.cpp.

References llvm::TargetRegisterClass::contains(), llvm::SIRegisterInfo::getLargestLegalSuperClass(), llvm::MachineOperand::getParent(), llvm::MachineBasicBlock::getParent(), llvm::MachineInstr::getParent(), llvm::MachineOperand::getReg(), llvm::SIRegisterInfo::getRegClass(), llvm::MachineOperand::getSubReg(), llvm::TargetRegisterClass::hasSuperClassEq(), llvm::MachineOperand::isReg(), MRI, and llvm::MCOperandInfo::RegClass.

Referenced by isLegalVSrcOperand(), isOperandLegal(), and legalizeOperandsVOP2().

◆ isLegalVSrcOperand()

| bool SIInstrInfo::isLegalVSrcOperand | ( | const MachineRegisterInfo & | MRI, |

| const MCOperandInfo & | OpInfo, | ||

| const MachineOperand & | MO | ||

| ) | const |

Check if MO would be a valid operand for the given operand definition OpInfo.

Note this does not attempt to validate constant bus restrictions (e.g. literal constant usage).

Definition at line 5675 of file SIInstrInfo.cpp.

References assert(), llvm::MachineOperand::isFI(), llvm::MachineOperand::isGlobal(), llvm::MachineOperand::isImm(), isLegalRegOperand(), llvm::MachineOperand::isReg(), llvm::MachineOperand::isTargetIndex(), and MRI.

◆ isLoadFromStackSlot()

|

override |

Definition at line 8598 of file SIInstrInfo.cpp.

References isMUBUF(), isSGPRSpill(), isSGPRStackAccess(), isStackAccess(), isVGPRSpill(), and MI.

◆ isLowLatencyInstruction()

| bool SIInstrInfo::isLowLatencyInstruction | ( | const MachineInstr & | MI | ) | const |

Definition at line 8566 of file SIInstrInfo.cpp.

Referenced by llvm::SIScheduleDAGMI::schedule().

◆ isMAI() [1/2]

|

inlinestatic |

Definition at line 792 of file SIInstrInfo.h.

References llvm::SIInstrFlags::IsMAI, and MI.

Referenced by llvm::GCNHazardRecognizer::getHazardType(), isImmOperandLegal(), isMFMA(), isXDL(), llvm::GCNHazardRecognizer::PreEmitNoopsCommon(), and pseudoToMCOpcode().

◆ isMAI() [2/2]

Definition at line 796 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::IsMAI.

◆ isMFMA()

|

inlinestatic |

Definition at line 800 of file SIInstrInfo.h.

Referenced by isMFMAorWMMA(), and llvm::GCNHazardRecognizer::ShouldPreferAnother().

◆ isMFMAorWMMA()

|

inlinestatic |

Definition at line 817 of file SIInstrInfo.h.

References isMFMA(), isSWMMAC(), isWMMA(), and MI.

◆ isMIMG() [1/2]

|

inlinestatic |

Definition at line 580 of file SIInstrInfo.h.

References MI, and llvm::SIInstrFlags::MIMG.

Referenced by getInstSizeInBytes(), getMemOperandsWithOffsetWidth(), isHighLatencyDef(), isImage(), isOperandLegal(), legalizeOperands(), and verifyInstruction().

◆ isMIMG() [2/2]

Definition at line 584 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::MIMG.

◆ isMTBUF() [1/2]

|

inlinestatic |

Definition at line 536 of file SIInstrInfo.h.

References MI, and llvm::SIInstrFlags::MTBUF.

Referenced by areLoadsFromSameBasePtr(), areMemAccessesTriviallyDisjoint(), getMemOperandsWithOffsetWidth(), isHighLatencyDef(), isVMEM(), and legalizeOperands().

◆ isMTBUF() [2/2]

Definition at line 540 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::MTBUF.

◆ isMUBUF() [1/2]

|

inlinestatic |

Definition at line 528 of file SIInstrInfo.h.

References MI, and llvm::SIInstrFlags::MUBUF.

Referenced by areLoadsFromSameBasePtr(), areMemAccessesTriviallyDisjoint(), llvm::SIRegisterInfo::getFrameIndexInstrOffset(), getMemOperandsWithOffsetWidth(), llvm::SIRegisterInfo::getScratchInstrOffset(), llvm::SIRegisterInfo::isFrameOffsetLegal(), isHighLatencyDef(), isLdsDma(), isLDSDMA(), isLoadFromStackSlot(), isStoreToStackSlot(), isVMEM(), legalizeOperands(), and llvm::SIRegisterInfo::needsFrameBaseReg().

◆ isMUBUF() [2/2]

Definition at line 532 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::MUBUF.

◆ isNeverUniform()

|

inlinestatic |

Definition at line 924 of file SIInstrInfo.h.

References llvm::SIInstrFlags::IsNeverUniform, and MI.

Referenced by getInstructionUniformity().

◆ isNonUniformBranchInstr()

| bool SIInstrInfo::isNonUniformBranchInstr | ( | MachineInstr & | Instr | ) | const |

Definition at line 8713 of file SIInstrInfo.cpp.

◆ isOperandLegal()

| bool SIInstrInfo::isOperandLegal | ( | const MachineInstr & | MI, |

| unsigned | OpIdx, | ||

| const MachineOperand * | MO = nullptr |

||

| ) | const |

Check if MO is a legal operand if it was the OpIdx Operand for MI.

Definition at line 5686 of file SIInstrInfo.cpp.

References assert(), llvm::detail::DenseSetImpl< ValueT, MapTy, ValueInfoT >::count(), llvm::GCNSubtarget::getConstantBusLimit(), llvm::MachineOperand::getImm(), llvm::AMDGPU::getNamedOperandIdx(), llvm::MachineOperand::getReg(), llvm::SIRegisterInfo::getRegClass(), llvm::MachineFunction::getRegInfo(), llvm::MachineOperand::getSubReg(), llvm::GCNSubtarget::hasGFX90AInsts(), llvm::AMDGPUSubtarget::hasInv2PiInlineImm(), llvm::GCNSubtarget::hasMAIInsts(), llvm::GCNSubtarget::hasVOP3Literal(), llvm::detail::DenseSetImpl< ValueT, MapTy, ValueInfoT >::insert(), llvm::SIRegisterInfo::isAGPR(), isDS(), llvm::MachineOperand::isFI(), llvm::MachineOperand::isGlobal(), llvm::MachineOperand::isImm(), isImmOperandLegal(), llvm::AMDGPU::isInlinableLiteral64(), isInlineConstant(), isLegalRegOperand(), isMIMG(), llvm::MachineOperand::isReg(), llvm::SIRegisterInfo::isSGPRReg(), llvm::AMDGPU::isSISrcOperand(), llvm::MachineOperand::isTargetIndex(), llvm::AMDGPU::isValid32BitLiteral(), isVALU(), isVOP3(), MI, MRI, llvm::AMDGPU::OPERAND_REG_IMM_FP64, llvm::AMDGPU::OPERAND_REG_IMM_INT64, llvm::AMDGPU::OPERAND_REG_IMM_V2FP32, llvm::AMDGPU::OPERAND_REG_IMM_V2INT32, llvm::MCOI::OPERAND_UNKNOWN, llvm::MCInstrDesc::operands(), llvm::MCOperandInfo::OperandType, llvm::MCOperandInfo::RegClass, and usesConstantBus().

Referenced by commuteInstructionImpl(), convertToThreeAddress(), and legalizeOperandsVOP3().

◆ isPacked() [1/2]

|

inlinestatic |

Definition at line 480 of file SIInstrInfo.h.

References llvm::SIInstrFlags::IsPacked, and MI.

◆ isPacked() [2/2]

Definition at line 484 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::IsPacked.

◆ isReallyTriviallyReMaterializable()

|

override |

Definition at line 127 of file SIInstrInfo.cpp.

References canRemat(), llvm::TargetInstrInfo::isReallyTriviallyReMaterializable(), and MI.

◆ isSafeToSink()

|

override |

Definition at line 193 of file SIInstrInfo.cpp.

References assert(), llvm::GenericCycle< ContextT >::contains(), llvm::GenericCycleInfo< ContextT >::getCycle(), llvm::GenericCycle< ContextT >::getExitBlocks(), llvm::MachineInstr::getParent(), llvm::GenericCycle< ContextT >::getParentCycle(), hasDivergentBranch(), llvm::SIRegisterInfo::isSGPRClass(), MI, MRI, and llvm::SmallVectorBase< Size_T >::size().

◆ isSALU() [1/2]

|

inlinestatic |

Definition at line 408 of file SIInstrInfo.h.

References MI, and llvm::SIInstrFlags::SALU.

Referenced by canRemat(), getInstSizeInBytes(), isSGPRSpill(), mayReadEXEC(), and shouldReadExec().

◆ isSALU() [2/2]

Definition at line 412 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::SALU.

◆ isScalarStore() [1/2]

|

inlinestatic |

- Returns

- true if this is an s_store_dword* instruction. This is more specific than isSMEM && mayStore.

Definition at line 872 of file SIInstrInfo.h.

References MI, and llvm::SIInstrFlags::SCALAR_STORE.

◆ isScalarStore() [2/2]

Definition at line 876 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::SCALAR_STORE.

◆ isScalarUnit()

|

inlinestatic |

Definition at line 849 of file SIInstrInfo.h.

References MI, llvm::SIInstrFlags::SALU, and llvm::SIInstrFlags::SMRD.

◆ isSchedulingBoundary()

|

override |

Definition at line 4022 of file SIInstrInfo.cpp.

References changesVGPRIndexingMode(), and MI.

◆ isSDWA() [1/2]

|

inlinestatic |

Definition at line 512 of file SIInstrInfo.h.

References MI, and llvm::SIInstrFlags::SDWA.

Referenced by canRemat(), and verifyInstruction().

◆ isSDWA() [2/2]

Definition at line 516 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::SDWA.

◆ isSegmentSpecificFLAT() [1/2]

|

inlinestatic |

Definition at line 618 of file SIInstrInfo.h.

References llvm::SIInstrFlags::FlatGlobal, llvm::SIInstrFlags::FlatScratch, and MI.

Referenced by areMemAccessesTriviallyDisjoint(), legalizeOperandsFLAT(), moveFlatAddrToVGPR(), and shouldRunLdsBranchVmemWARHazardFixup().

◆ isSegmentSpecificFLAT() [2/2]

Definition at line 623 of file SIInstrInfo.h.

References llvm::SIInstrFlags::FlatGlobal, llvm::SIInstrFlags::FlatScratch, and llvm::get().

◆ isSGPRSpill() [1/2]

|

inlinestatic |

Definition at line 728 of file SIInstrInfo.h.

References isSALU(), isSpill(), and MI.

Referenced by isLoadFromStackSlot(), and isStoreToStackSlot().

◆ isSGPRSpill() [2/2]

Definition at line 734 of file SIInstrInfo.h.

◆ isSGPRStackAccess()

| unsigned SIInstrInfo::isSGPRStackAccess | ( | const MachineInstr & | MI, |

| int & | FrameIndex | ||

| ) | const |

Definition at line 8590 of file SIInstrInfo.cpp.

References Addr, assert(), getNamedOperand(), llvm::MachineOperand::getReg(), and MI.

Referenced by isLoadFromStackSlot(), and isStoreToStackSlot().

◆ isSMRD() [1/2]

|

inlinestatic |

Definition at line 544 of file SIInstrInfo.h.

References MI, and llvm::SIInstrFlags::SMRD.

Referenced by areLoadsFromSameBasePtr(), areMemAccessesTriviallyDisjoint(), breaksSMEMSoftClause(), canRemat(), llvm::GCNHazardRecognizer::getHazardType(), getMemOperandsWithOffsetWidth(), hasUnwantedEffectsWhenEXECEmpty(), isBufferSMRD(), isLowLatencyInstruction(), isSMEMClauseInst(), legalizeOperands(), llvm::GCNHazardRecognizer::PreEmitNoopsCommon(), shouldReadExec(), and verifyInstruction().

◆ isSMRD() [2/2]

Definition at line 548 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::SMRD.

◆ isSOP1() [1/2]

|

inlinestatic |

Definition at line 440 of file SIInstrInfo.h.

References MI, and llvm::SIInstrFlags::SOP1.

◆ isSOP1() [2/2]

Definition at line 444 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::SOP1.

◆ isSOP2() [1/2]

|

inlinestatic |

Definition at line 448 of file SIInstrInfo.h.

References MI, and llvm::SIInstrFlags::SOP2.

Referenced by verifyInstruction().

◆ isSOP2() [2/2]

Definition at line 452 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::SOP2.

◆ isSOPC() [1/2]

|

inlinestatic |

Definition at line 456 of file SIInstrInfo.h.

References MI, and llvm::SIInstrFlags::SOPC.

Referenced by verifyInstruction().

◆ isSOPC() [2/2]

Definition at line 460 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::SOPC.

◆ isSOPK() [1/2]

|

inlinestatic |

Definition at line 464 of file SIInstrInfo.h.

References MI, and llvm::SIInstrFlags::SOPK.

Referenced by verifyInstruction().

◆ isSOPK() [2/2]

Definition at line 468 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::SOPK.

◆ isSOPP() [1/2]

|

inlinestatic |

Definition at line 472 of file SIInstrInfo.h.

References MI, and llvm::SIInstrFlags::SOPP.

◆ isSOPP() [2/2]

Definition at line 476 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::SOPP.

◆ isSpill() [1/2]

|

inlinestatic |

Definition at line 744 of file SIInstrInfo.h.

References MI, and llvm::SIInstrFlags::Spill.

◆ isSpill() [2/2]

Definition at line 740 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::Spill.

Referenced by isBasicBlockPrologue(), isSGPRSpill(), and isVGPRSpill().

◆ isStackAccess()

| unsigned SIInstrInfo::isStackAccess | ( | const MachineInstr & | MI, |

| int & | FrameIndex | ||

| ) | const |

Definition at line 8577 of file SIInstrInfo.cpp.

References Addr, assert(), getNamedOperand(), llvm::MachineOperand::getReg(), MI, and llvm::AMDGPUAS::PRIVATE_ADDRESS.

Referenced by isLoadFromStackSlot(), and isStoreToStackSlot().

◆ isStoreToStackSlot()

|

override |

Definition at line 8612 of file SIInstrInfo.cpp.

References isMUBUF(), isSGPRSpill(), isSGPRStackAccess(), isStackAccess(), isVGPRSpill(), and MI.

◆ isSWMMAC() [1/2]

|

inlinestatic |

Definition at line 821 of file SIInstrInfo.h.

References llvm::SIInstrFlags::IsSWMMAC, and MI.

Referenced by isMFMAorWMMA().

◆ isSWMMAC() [2/2]

Definition at line 825 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::IsSWMMAC.

◆ isTRANS() [1/2]

|

inlinestatic |

Definition at line 768 of file SIInstrInfo.h.

References MI, and llvm::SIInstrFlags::TRANS.

◆ isTRANS() [2/2]

Definition at line 772 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::TRANS.

◆ isVALU() [1/2]

|

inlinestatic |

Definition at line 416 of file SIInstrInfo.h.

References MI, and llvm::SIInstrFlags::VALU.

Referenced by llvm::GCNHazardRecognizer::getHazardType(), getInstSizeInBytes(), isIgnorableUse(), isLdsDma(), isLDSDMA(), isOperandLegal(), isVGPRSpill(), llvm::GCNHazardRecognizer::PreEmitNoopsCommon(), shouldReadExec(), and verifyInstruction().

◆ isVALU() [2/2]

Definition at line 420 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::VALU.

◆ isVGPRCopy()

|

inline |

Definition at line 959 of file SIInstrInfo.h.

References assert(), llvm::MachineFunction::getRegInfo(), llvm::SIRegisterInfo::isSGPRReg(), MI, and MRI.

Referenced by foldImmediate().

◆ isVGPRSpill() [1/2]

|

inlinestatic |

Definition at line 716 of file SIInstrInfo.h.

References isSpill(), isVALU(), and MI.

Referenced by isLoadFromStackSlot(), isStoreToStackSlot(), and verifyInstruction().

◆ isVGPRSpill() [2/2]

Definition at line 722 of file SIInstrInfo.h.

◆ isVIMAGE() [1/2]

|

inlinestatic |

Definition at line 588 of file SIInstrInfo.h.

References MI, and llvm::SIInstrFlags::VIMAGE.

Referenced by isImage(), and legalizeOperands().

◆ isVIMAGE() [2/2]

Definition at line 592 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::VIMAGE.

◆ isVINTERP() [1/2]

|

inlinestatic |

Definition at line 841 of file SIInstrInfo.h.

References MI, and llvm::SIInstrFlags::VINTERP.

◆ isVINTERP() [2/2]

Definition at line 845 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::VINTERP.

◆ isVINTRP() [1/2]

|

inlinestatic |

Definition at line 784 of file SIInstrInfo.h.

References MI, and llvm::SIInstrFlags::VINTRP.

Referenced by llvm::GCNHazardRecognizer::getHazardType(), and llvm::GCNHazardRecognizer::PreEmitNoopsCommon().

◆ isVINTRP() [2/2]

Definition at line 788 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::VINTRP.

◆ isVMEM() [1/2]

|

inlinestatic |

Definition at line 432 of file SIInstrInfo.h.

References isImage(), isMTBUF(), isMUBUF(), and MI.

Referenced by breaksVMEMSoftClause(), llvm::GCNHazardRecognizer::getHazardType(), isVMEMClauseInst(), isVMEMLoad(), llvm::GCNHazardRecognizer::PreEmitNoopsCommon(), and shouldRunLdsBranchVmemWARHazardFixup().

◆ isVMEM() [2/2]

Definition at line 436 of file SIInstrInfo.h.

◆ isVOP1() [1/2]

|

inlinestatic |

Definition at line 488 of file SIInstrInfo.h.

References MI, and llvm::SIInstrFlags::VOP1.

Referenced by canRemat().

◆ isVOP1() [2/2]

Definition at line 492 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::VOP1.

◆ isVOP2() [1/2]

|

inlinestatic |

Definition at line 496 of file SIInstrInfo.h.

References MI, and llvm::SIInstrFlags::VOP2.

Referenced by canRemat(), legalizeOperands(), and verifyInstruction().

◆ isVOP2() [2/2]

Definition at line 500 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::VOP2.

◆ isVOP3() [1/2]

|

inlinestatic |

Definition at line 504 of file SIInstrInfo.h.

References MI, and llvm::SIInstrFlags::VOP3.

Referenced by canRemat(), isImmOperandLegal(), isOperandLegal(), legalizeOperands(), moveToVALUImpl(), and verifyInstruction().

◆ isVOP3() [2/2]

Definition at line 508 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::VOP3.

◆ isVOP3P() [1/2]

|

inlinestatic |

Definition at line 776 of file SIInstrInfo.h.

References MI, and llvm::SIInstrFlags::VOP3P.

◆ isVOP3P() [2/2]

Definition at line 780 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::VOP3P.

◆ isVOPC() [1/2]

|

inlinestatic |

Definition at line 520 of file SIInstrInfo.h.

References MI, and llvm::SIInstrFlags::VOPC.

Referenced by legalizeOperands(), and verifyInstruction().

◆ isVOPC() [2/2]

Definition at line 524 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::VOPC.

◆ isVSAMPLE() [1/2]

|

inlinestatic |

Definition at line 596 of file SIInstrInfo.h.

References MI, and llvm::SIInstrFlags::VSAMPLE.

Referenced by isImage(), legalizeOperands(), and verifyInstruction().

◆ isVSAMPLE() [2/2]

Definition at line 600 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::VSAMPLE.

◆ isWave32()

| bool llvm::SIInstrInfo::isWave32 | ( | ) | const |

Definition at line 9440 of file SIInstrInfo.cpp.

References llvm::GCNSubtarget::isWave32().

Referenced by restoreExec().

◆ isWMMA() [1/2]

|

inlinestatic |

Definition at line 809 of file SIInstrInfo.h.

References llvm::SIInstrFlags::IsWMMA, and MI.

Referenced by convertToThreeAddress(), and isMFMAorWMMA().

◆ isWMMA() [2/2]

Definition at line 813 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::IsWMMA.

◆ isWQM() [1/2]

|

inlinestatic |

Definition at line 695 of file SIInstrInfo.h.

References MI, and llvm::SIInstrFlags::WQM.

◆ isWQM() [2/2]

Definition at line 699 of file SIInstrInfo.h.

References llvm::get(), and llvm::SIInstrFlags::WQM.

◆ isWWMRegSpillOpcode()

Definition at line 748 of file SIInstrInfo.h.

◆ legalizeGenericOperand()

| void SIInstrInfo::legalizeGenericOperand | ( | MachineBasicBlock & | InsertMBB, |

| MachineBasicBlock::iterator | I, | ||

| const TargetRegisterClass * | DstRC, | ||

| MachineOperand & | Op, | ||

| MachineRegisterInfo & | MRI, | ||

| const DebugLoc & | DL | ||

| ) | const |

Definition at line 6170 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::add(), llvm::BuildMI(), DL, foldImmediate(), llvm::get(), llvm::SIRegisterInfo::getRegClassForReg(), I, llvm::RegState::Implicit, llvm::SIRegisterInfo::isSGPRClass(), and MRI.

Referenced by legalizeOperands().

◆ legalizeOperands()

| MachineBasicBlock * SIInstrInfo::legalizeOperands | ( | MachineInstr & | MI, |

| MachineDominatorTree * | MDT = nullptr |

||

| ) | const |

Legalize all operands in this instruction.

This function may create new instructions and control-flow around MI. If present, MDT is updated.

- Returns

- A new basic block that contains

MIif new blocks were created.

Definition at line 6502 of file SIInstrInfo.cpp.