#### MLIR Graph Compiler for In-Memory Inference Computing

Satyam Srivastava, Kshitij Jain, Vinay M, Prashantha NR, Sudeep Bhoja [d-Matrix Corporation]

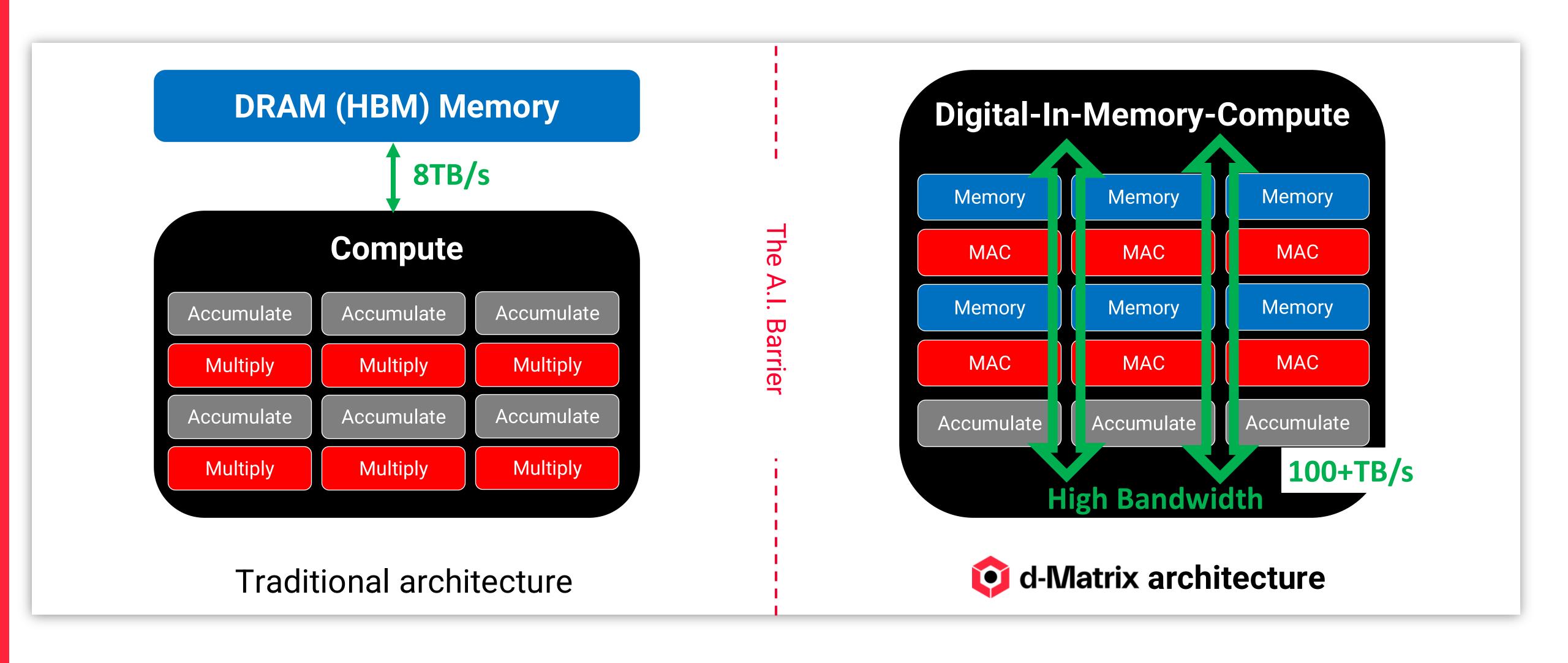

# A New Computing Paradigm for GenAl Inference

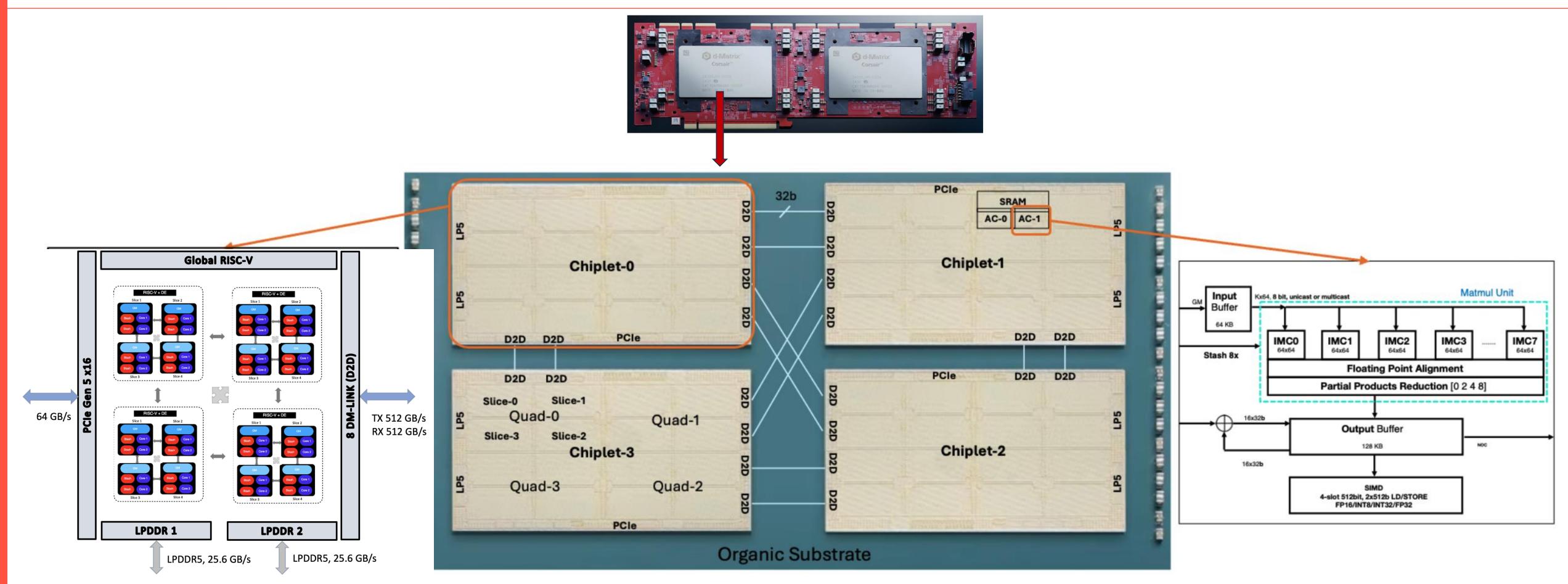

## Corsair Accelerator Architecture Purpose Built for Al

Chiplet-based modular design: connectivity, scaling, cost

In-memory compute with block floating point: efficiency, throughput, accuracy

Large, on-chip performance memory: high bandwidth for params and caches

Independent, collaborative Quads: asynchronous, self-contained graph execution

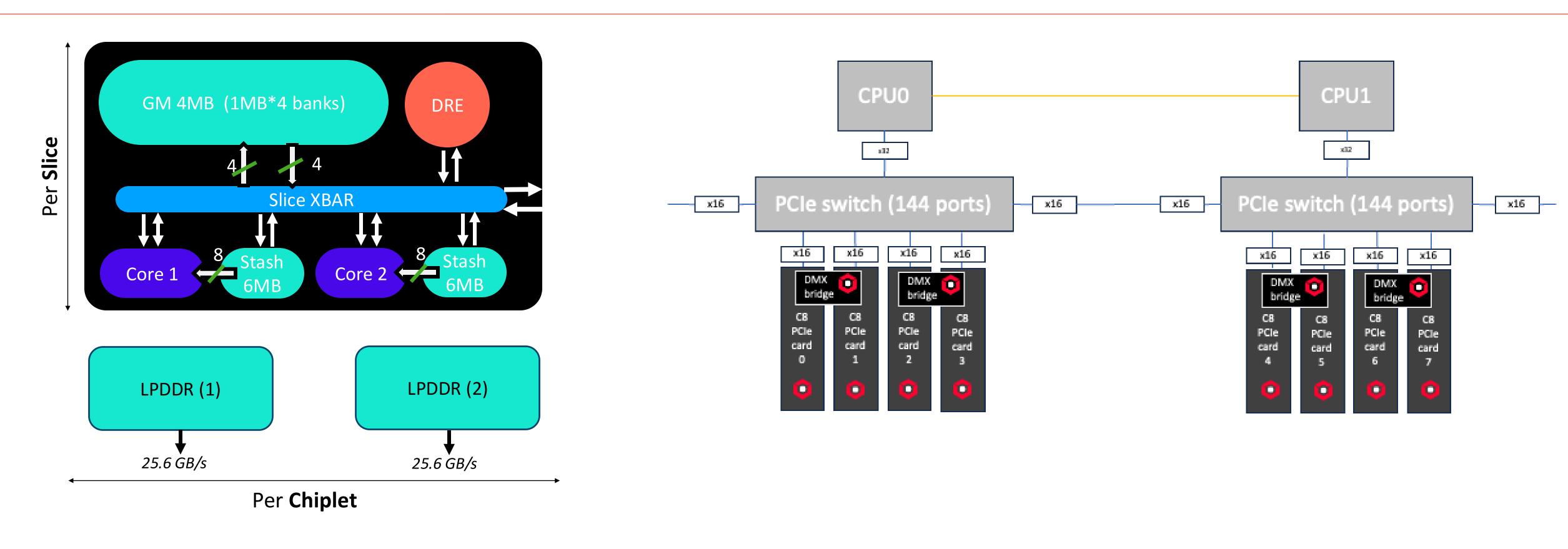

# Harnessing Memory Hierarchy and Scalability

- Highest performance leverages fast, on-chip memory, closest to compute units

- Operations spread over chiplets/cards/servers/racks to aggregate compute and memory

- Parallelism strategy optimized for compute, memory, and communication costs

# Corsair ISA and Graph Representation

| DMA based data transfer from -            |

|-------------------------------------------|

| xxx: DDR, GM, ST, OB                      |

| yyy: DDR, GM, ST, OB, WB, IB, DRE, SIMD   |

| PCIe based peer-to-peer transfer          |

|                                           |

| Matrix multiplication using DIMC          |

| Direct convolution using DIMC             |

| Kernel function execution on SIMD cores   |

| Control function execution using gang CPU |

|                                           |

| Array transpose                           |

| Rule-based sub-view extraction            |

| Rule-based sub-tensor insertion           |

|                                           |

| Nestable iterators                        |

| CPU messaging via mailboxes               |

| Pre-configure units (AC, SIMD, GM, ST)    |

| Various barriers for stalling graph exec  |

| Software triggered reset                  |

| Dummy, filler ops used for graph sync     |

|                                           |

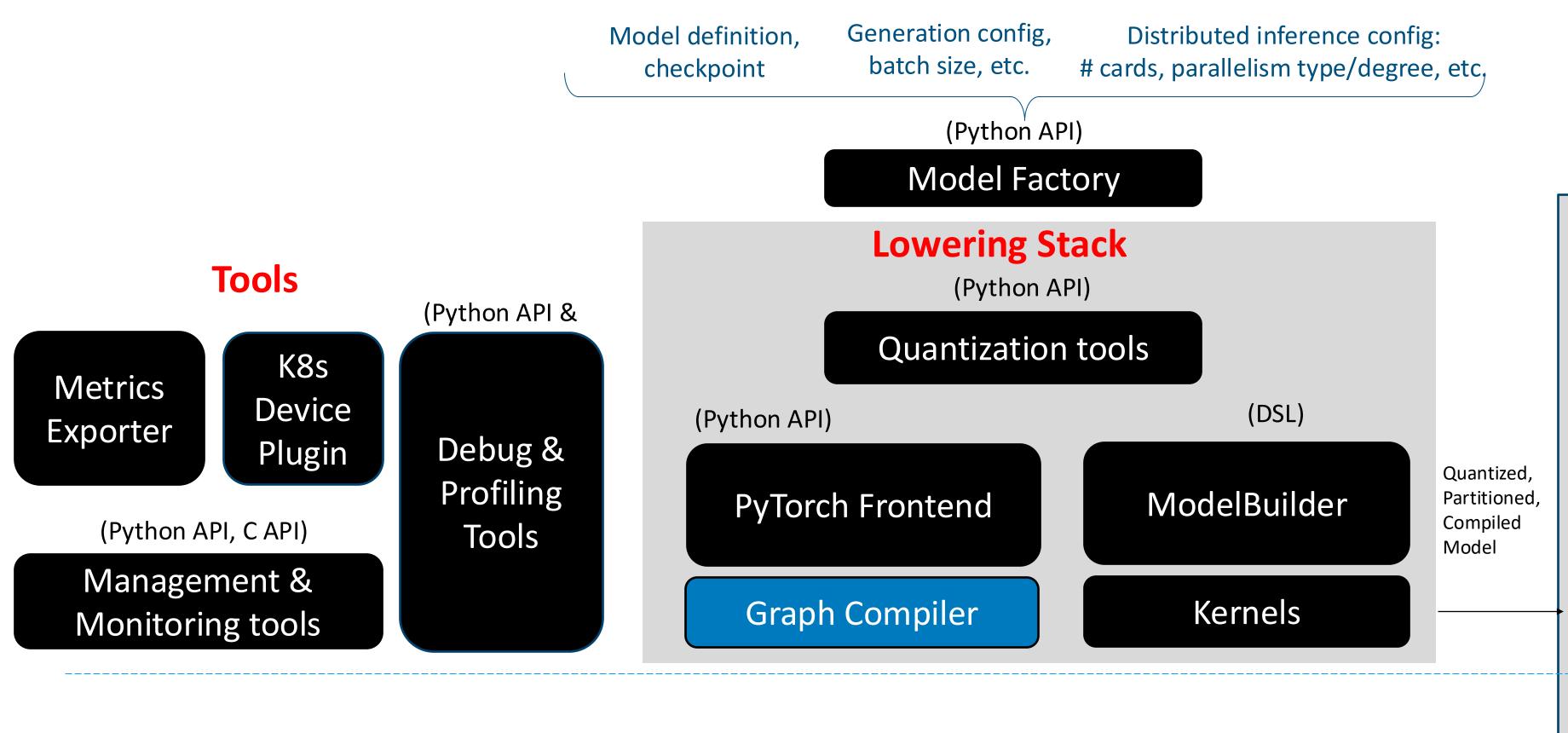

#### Aviator Software Stack for Efficient, Scalable Inference

# Graph Compiler for In-Memory Computing: Challenges

- Support of standard and custom ML operations

- Dynamic tensor shapes, conditions, autoregression

- Multi-device parallel model adaptation

- Tensor placement across memory hierarchy levels

- Fusion of large subgraphs into mega-kernels

- Resource sharing and lifetime management across multiple kernels

- Tiling, balance of spatial and temporal spread

- Stationarity, proximity, concurrency of operations

Ease, coverage of algorithm expression

Developer intent and control

Hardware features and utilization

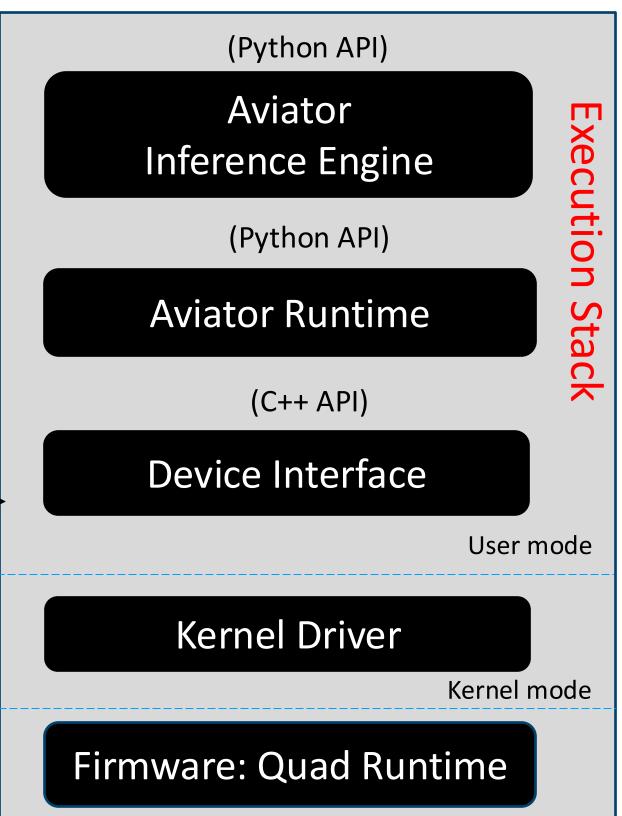

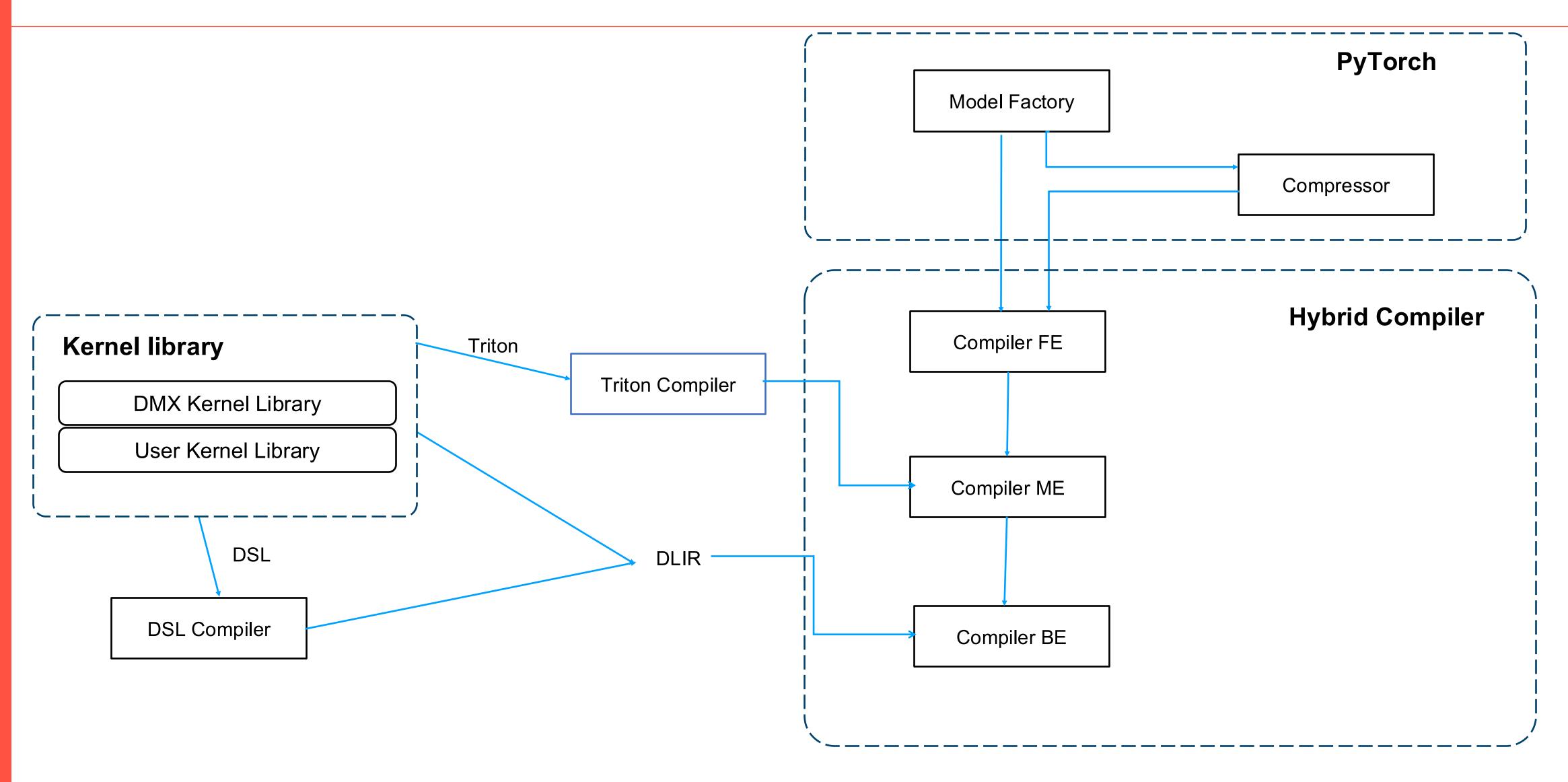

## Aviator Lowering Stack: High Perf Kernels and MLIR Compiler

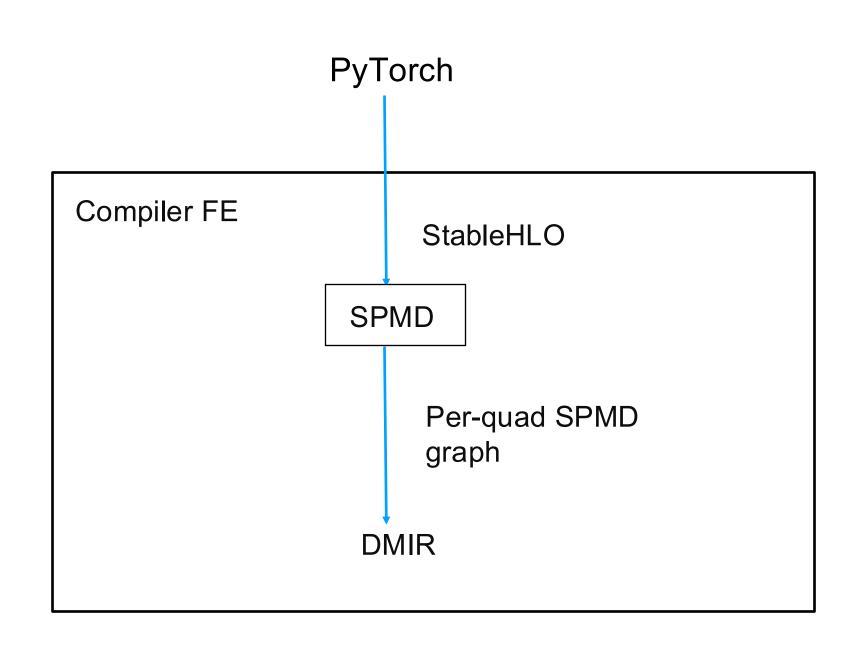

## MLIR Graph Compiler Stack

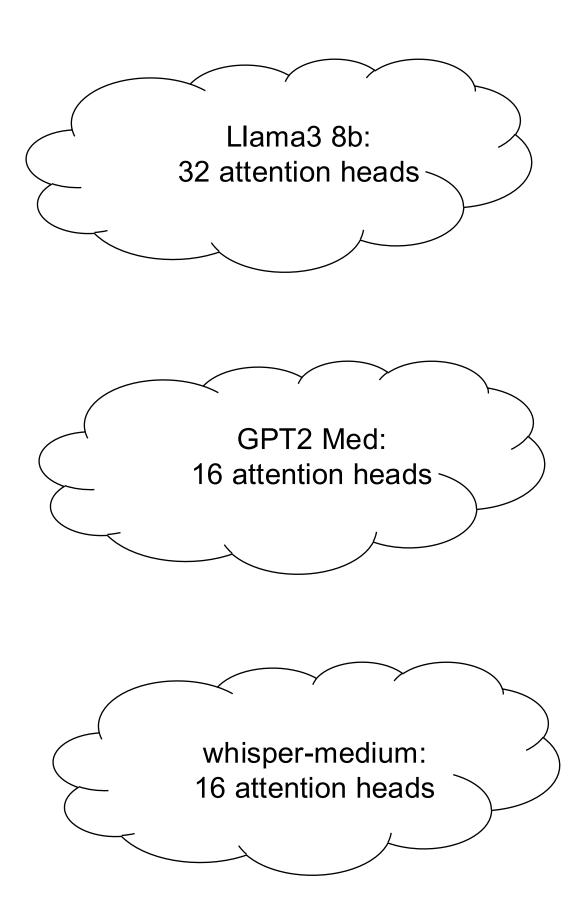

## SPMD partitioning

This per-quad symmetry maps quite nicely to multiheaded Attention models

#### Remember:

Card => 2 Packages

Package => 4 Chiplets

Chiplet => 4 quads

Total of 32 quads per card

```

module attributes {dm.model_inputs.type = [tensor<512x512xf32>], dm.model_outputs.type = [tensor<512x512xf32>]} {

func.func @main(%arg0: tensor<512x512xf32>) → tensor<512x512xf32> {

%0 = "dmir.const"() <{value = dense<_____> : tensor<512x512xf32>}> : () -> tensor<512x512xf32>

%1 = "dmir.matmul"(%arg0, %0) : (tensor<512x512xf32>, tensor<512x512xf32>) -> tensor<512x512xf32>

return %1 : tensor<512x512xf32>

func.func @main(\%arg0: tensor<512x512x!dmir.block_fp<8FP16\_64R>>) -> tensor<512x512xf16> \{ for example of the content of the

%0 = "dmir.const"() <{value = dense<"...">: tensor<512x512xf32>}> : () -> tensor<512x512x!dmir.block_fp<BFP16_64C>> %1 = "dmir.undef"() : () -> tensor<512x512xf16>

affine.for %arg1 = 0 to 8 {

affine.for %arg2 = 0 to 8 {

%7 = "dmir.matmul"(%extracted_slice, %extracted_slice_0) : (tensor<64x512x!dmir.block_fp<BFP16_64R>>, tensor<512x64x!dmir.block_fp<BFP16_64C>>) -> tensor<64x64x!dmir.block_fp<BFP32>>

return %1 : tensor<512x512xf16>

44 = "dmir.matmul"(%1, %3) : (!affine_ext.vec_ext<5x8x!affine_ext.vec_ext<5x6x64x!dmir.block_fp<8FP16_64R>>>, !affine_ext.vec_ext<8x1x!affine_ext.vec_ext<6x6x64x!dmir.block_fp<8FP16_64C>>>)

func.func @main(%arg8: memref<8x8x!affine_ext.vec_ext<64x64x!dmir.block_fp<8FP16_64C>>>) {

%alloc = memref.alloc() : memref<8x8x!affine_ext.vec_ext<64x64x!fi>> affine.for %arg3 = 0 to 8 {

%affine_for %arg4 = 0 to 8 {

!affine_ext.vec_ext<64x64x!dmir.block_fp<8FP16_64R>>,

!affine_ext.vec_ext<64x64x!dmir.block_fp<8FP16_64R>>,

!affine_ext.vec_ext<64x64x!dmir.block_fp<8FP16_64R>>,

!affine_ext.vec_ext<64x64x!dmir.block_fp<BFP16_64R>>,

laffine_ext.vec_ext<64x64xldmir.block_fp<BFP16_64R>>,

!affine_ext.vec_ext<64x64x!dmir.block_fp<BFP16_64R>>,

!affine_ext.vec_ext<64x64x!dmir.block_fp<BFP16_64R>>

// 8 64x64 blocks of weights

laffine_ext.vec_ext<64x64x!dmir.block_fp<8FP16_64C>>,

!affine_ext.vec_ext<64x64x!dmir.block_fp<8FP16_64C>>,

!affine_ext.vec_ext<64x64x!dmir.block_fp<8FP16_64C>>,

!affine_ext.vec_ext<64x64x!dmir.block_fp<BFP16_64C>>

// Partial product reduction to calculate a single 64x64 block of output

num_imc 8 ppr_mode 3 -> !affine_ext.vec_ext<64x64xf16>

```

```

module attributes {dm.model_constants.type = [tensor<512x512x|dmir.block_fp<BFP16_64C>>], dm.model_inputs.type = [tensor<512x512xf32>], dm.model_outputs.type = [tensor<512x512xf32>], gpu.container_module} {

func.func {main(%arg@: memref<8x8x|affine_ext.vec_ext<64x64x|dmir.block_fp<BFP16_64C>>>) {

%c8 = arith.constant 8 : index

%c1 = arith.constant 1 : index

%alloc = memref.alloc() : memref<8x8x|affine_ext.vec_ext<64x64xf16>>

%gpu_lauych_func {main_kernel : gmain_kernel blocks in (%c1, %c1)

threads in (%c8, %c1, %c1)

args(%arg2 : memref<8x8x|affine_ext.vec_ext<64x64x|dmir.block_fp<BFP16_64C>>>,

%alloc : memref<8x8x|affine_ext.vec_ext<64x64x|dmir.block_fp<BFP16_64C>>>,

%alloc : memref<8x8x|affine_ext.vec_ext<64x64x|dmir.block_fp<BFP16_64C>>>,

%alloc : memref<8x8x|affine_ext.vec_ext<64x64x|dmir.block_fp<BFP16_64C>>>,

%alloc : memref<8x8x|affine_ext.vec_ext<64x64x|dmir.block_fp<BFP16_64C>>>,

%arg9: memref<8x8x|affine_ext.vec_ext<64x64x|dmir.

```

#### A 512 x512 matmul through our compiler

```

module attributes {dm.model_inputs.type = [tensor<512x512xf32>], dm.model_outputs.type = [tensor<512x512xf32>]} {

func.func @main(%arg0: tensor<512x512xf32>) -> tensor<512x512xf32> {

| %0 = "dmir.const"() <{value = dense<"...">: tensor<512x512xf32>} : () -> tensor<512x512xf32>

| %1 = "dmir.matmul"(%arg0, %0) : (tensor<512x512xf32>, tensor<512x512xf32>) -> tensor<512x512xf32>

| return %1 : tensor<512x512xf32>

| }

}

```

```

func.func @main(%arg0: tensor<512x512x!dmir.block_fp<BFP16_64R>>) -> tensor<512x512xf16> {

%c0 = arith.constant 0 : index

%0 = "dmir.const"() <{value = dense<"___"> : tensor<512x512xf32>}> : () -> tensor<512x512x!dmir.block_fp<BFP16_64C>>

%1 = "dmir.undef"() : () -> tensor<512x512xf16>    affine.for %arg1 = 0 to 8 {

index

index

```

```

module attributes {dm.model_inputs.type = [tensor<512x512xf32>], dm.model_outputs.type = [tensor<512x512xf32>]} {

func.func @main(%arg0: tensor<512x512xf32>) -> tensor<512x512xf32> {

| %0 = "dmir.const"() <{value = dense<_"..."> : tensor<512x512xf32>}> : () -> tensor<512x512xf32>

| %1 = "dmir.matmul"(%arg0, %0) : (tensor<512x512xf32>, tensor<512x512xf32>) -> tensor<512x512xf32>

| return %1 : tensor<512x512xf32>

| }

}

```

#### A 512 x512 matmul through our compiler

module attributes {dm.model\_inputs.type = [tensor<512x512xf32>], dm.model\_outputs.type = [tensor<512x512xf32>]} {

#### A 512 x512 matmul through our compiler

```

func.func @main(\arg0: tensor<512x512xf32>) -> tensor<512x512xf32> -> tensor<512x512xf32>) -> tensor<512x512xf32> -> tensor<51

```

```

module attributes {dm.model_constants.type = [tensor<512x512x!dmir.block_fp<BFP16_64C>>], dm.model_inputs.type = [tensor<512x512xf32>], dm.model_outputs.type = [tensor<512x512xf32>]} {

func.func @main(%arg0: memref<8x8x!affine_ext.vec_ext<64x64x!dmir.block_fp<BFP16_64C>>>) {

%alloc = memref.alloc() : memref<8x8x!affine_ext.vec_ext<64x64xf16>>

affine.for %arg3 = 0 to 8 {

affine.for %arg4 = 0 to 8 {

// 8 64x64 blocks of activation

%18 = lldmir.matmul %1, %2, %3, %4, %5, %6, %7, %8 : !affine_ext.vec_ext<64x64x!dmir.block_fp<BFP16_64R>>,

!affine_ext.vec_ext<64x64x!dmir.block_fp<BFP16_64R>>,

!affine_ext.vec_ext<64x64x!dmir.block_fp<BFP16_64R>>,

!affine_ext.vec_ext<64x64x!dmir.block_fp<BFP16_64R>>,

!affine_ext.vec_ext<64x64x!dmir.block_fp<BFP16_64R>>,

!affine_ext.vec_ext<64x64x!dmir.block_fp<BFP16_64R>>,

!affine_ext.vec_ext<64x64x!dmir.block_fp<BFP16_64R>>,

!affine_ext.vec_ext<64x64x!dmir.block_fp<BFP16_64R>>

// 8 64x64 blocks of weights

%10, %11, %12, %13, %14, %15, %16, %17 : !affine_ext.vec_ext<64x64x!dmir.block_fp<BFP16_64C>>,

!affine_ext.vec_ext<64x64x!dmir.block_fp<BFP16_64C>>,

!affine_ext.vec_ext<64x64x!dmir.block_fp<BFP16_64C>>,

!affine_ext.vec_ext<64x64x!dmir.block_fp<BFP16_64C>>,

!affine_ext.vec_ext<64x64x!dmir.block_fp<BFP16_64C>>,

!affine_ext.vec_ext<64x64x!dmir.block_fp<BFP16_64C>>,

!affine_ext.vec_ext<64x64x!dmir.block_fp<BFP16_64C>>,

!affine_ext.vec_ext<64x64x!dmir.block_fp<BFP16_64C>>

// Partial product reduction to calculate a single 64x64 block of output

num_imc 8 ppr_mode 3 -> !affine_ext.vec_ext<64x64xf16>

```

module attributes {dm.model\_inputs.type = [tensor<512x512xf32>], dm.model\_outputs.type = [tensor<512x512xf32>]} {

%0 = "dmir.const"() <{value = dense<"..."> : tensor<512x512xf32>}> : () -> tensor<512x512xf32>

func.func @main(%arg0: tensor<512x512xf32>) -> tensor<512x512xf32> {

```

%1 = "dmir.matmul"(%arg0, %0) : (tensor<512x512xf32>, tensor<512x512xf32>) -> tensor<512x512xf32>

return %1 : tensor<512x512xf32>

func.func @main(\%arg0: tensor<512x512x!dmir.block_fp<8FP16\_64R>>) -> tensor<512x512xf16> \{ for example of the content of the

%0 = "dmir.const"() <{value = dense<"...">: tensor<512x512xf32>}> : () -> tensor<512x512x!dmir.block_fp<BFP16_64C>> %1 = "dmir.undef"() : () -> tensor<512x512xf16>

affine.for %arg1 = 0 to 8 {

affine.for %arg2 = 0 to 8 {

7 = "dmir.matmul"(%extracted_slice, %extracted_slice_0): (tensor<64x512x!dmir.block_fp<BFP16_64R>>, tensor<512x64x!dmir.block_fp<BFP16_64C>>) -> tensor<64x64x!dmir.block_fp<BFP32>>

return %1 : tensor<512x512xf16>

44 = "dmir.matmul"(%1, %3) : (!affine_ext.vec_ext<5x8x!affine_ext.vec_ext<5x6x64x!dmir.block_fp<8FP16_64R>>>, !affine_ext.vec_ext<8x1x!affine_ext.vec_ext<6x6x64x!dmir.block_fp<8FP16_64C>>>)

func.func @main(%arg8: memref<8x8x!affine_ext.vec_ext<64x64x!dmir.block_fp<8FP16_64C>>>) {

%alloc = memref.alloc() : memref<8x8x!affine_ext.vec_ext<64x64x!fi>> affine.for %arg3 = 0 to 8 {

%affine_for %arg4 = 0 to 8 {

!affine_ext.vec_ext<64x64x!dmir.block_fp<BFP16_64R>>,

!affine_ext.vec_ext<64x64x!dmir.block_fp<BFP16_64R>>,

!affine_ext.vec_ext<64x64x!dmir.block_fp<BFP16_64R>>,

!affine_ext.vec_ext<64x64x!dmir.block_fp<BFP16_64R>>,

laffine_ext.vec_ext-64x64x1dmir.block_fp<8FP16_64R>>,

!affine_ext.vec_ext-64x64x1dmir.block_fp<8FP16_64R>>,

!affine_ext.vec_ext-64x64x1dmir.block_fp<8FP16_64R>>

// 8 64x64 blocks of weights

laffine_ext.vec_ext<64x64x!dmir.block_fp<8FP16_64C>>,

!affine_ext.vec_ext<64x64x!dmir.block_fp<8FP16_64C>>,

!affine_ext.vec_ext<64x64x!dmir.block_fp<8FP16_64C>>,

!affine_ext.vec_ext<64x64x!dmir.block_fp<BFP16_64C>>

// Partial product reduction to calculate a single 64x64 block of output

num_imc 8 ppr_mode 3 -> !affine_ext.vec_ext<64x64xf16>

```

## Number of Affine Dialect Based Optimizations b/w FE/ME and ME/BE

#### FE/ME

- 1. Loop permutation Make loops w/ highest trip counts outermost

- 2. Single trip loop promotion Promote single iteration loops (inner-most only)

- 3. Normalization Normalize loop nests to enable producer-consumer fusion

#### ME/BE

1. Affine scalar replacement – Forward affine memref stores to loads, remove redundant loads, remove dead stores

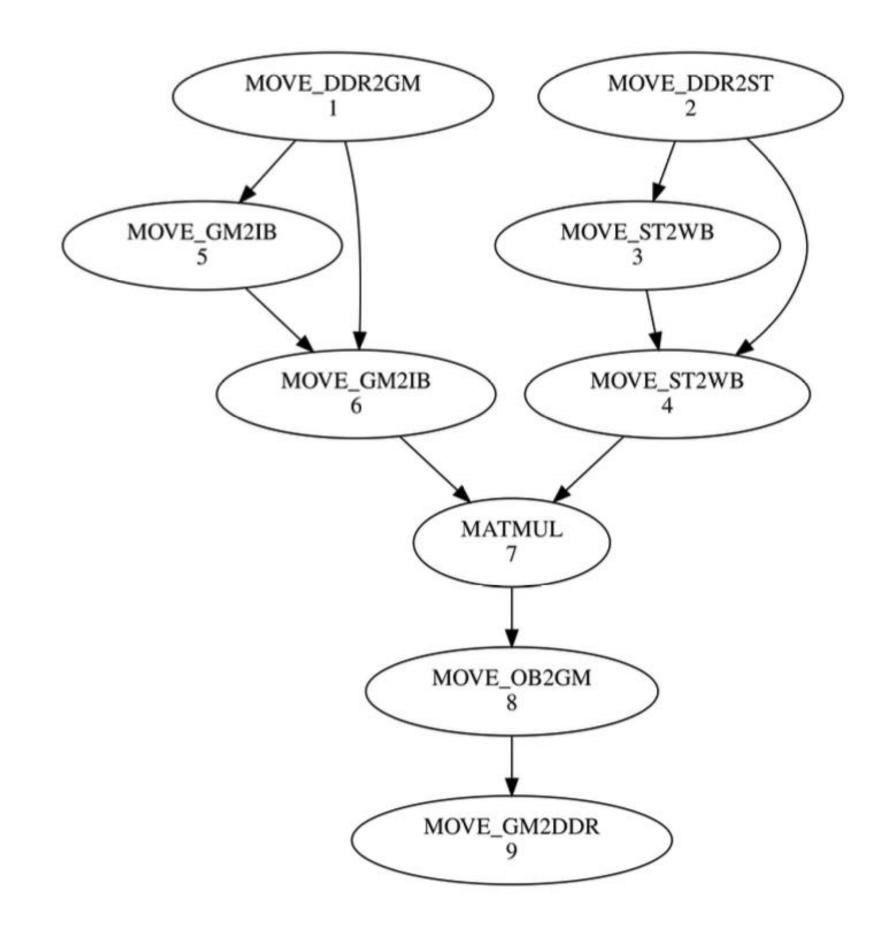

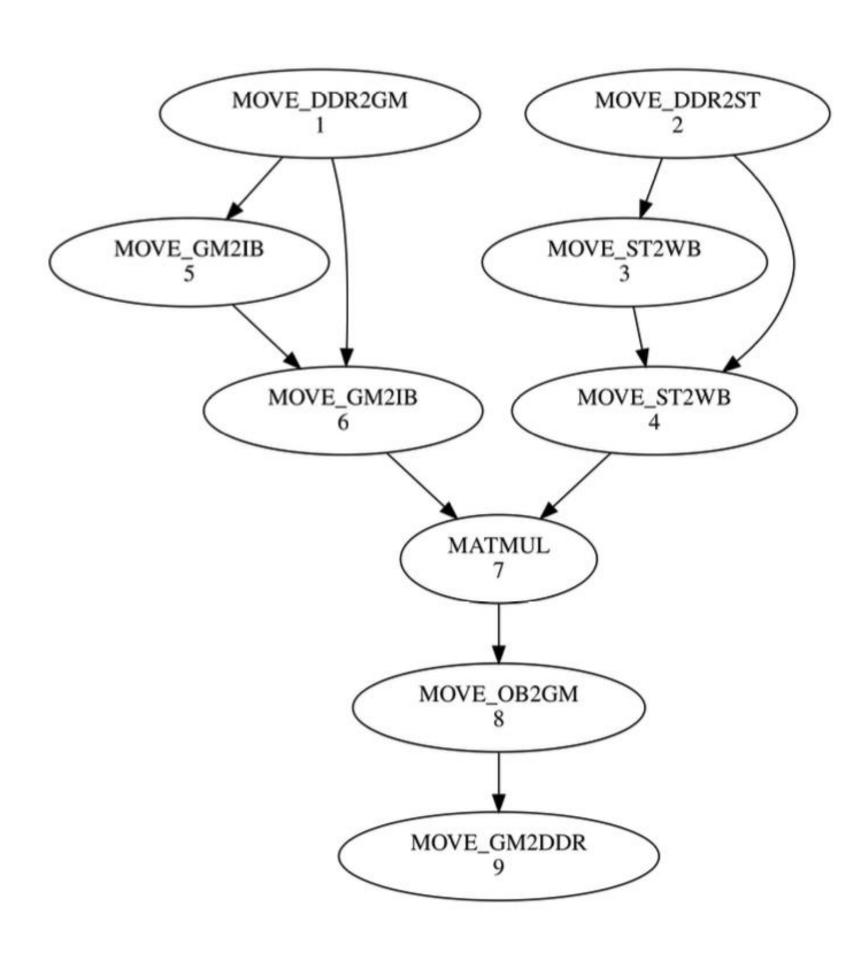

## DLIR: MLIR Egress to DMX ISA

```

"dlir.dmmq"() <{sym_name = "scmm"}> ({

"dlir.scheduled_graph"() <{sym_name = "scmm"}> ({

"dlir.dispatch_queue"() <{sym_name = "queue_0"}> ({

%1 = "dlir.task_group"(%0) ({

// DDR2GM

%9 = "dlir.dma_config"(...)

%10 = "dlir.copy"(%9, ...)

// DDR2ST

%11 = "dlir.dma_config"(...)

%12 = "dlir.copy"(%11, ...)

}) : (index) -> !dlir.token

%3 = "dlir.task_group"(%2) ({

// GM2IB

%13 = "dlir.dma_config"(...)

%14 = "dlir.copy"(%13, ...)

// ST2WB

%15 = "dlir.dma_config"(...)

%16 = "dlir.copy"(%15, ...)

%17 = "dlir.task_barrier"(%14, %16) : (index) -> !dlir.token

// Produces result in OB

%18 = "dlir.matmul"(...)

%19 = "dlir.task_barrier"(%18) : (index) -> !dlir.token

// OB2GM

%20 = "dlir.dma_config"(...)

%21 = "dlir.copy"(%20, ...)

%22 = "dlir.task_barrier"(%21) : (index) -> !dlir.token

// GM2DDR

%23 = "dlir.dma_config"(...)

%24 = "dlir.copy"(%23, ...)

}) : (!dlir.token) -> !dlir.token

}) : () -> ()

}) : () -> ()

```

#### Conclusion

MLIR enabled us to build an ergonomic S/W stack that we're confident can realize the full potential of our hardware.

- Compatibility with PyTorch allowed us to meet users where they are.

- Flexibility and extensible dialect system -

- Allowed us to faithfully model and thereby optimize for our hardware and numerics, via custom IRs.

- Allowed us to support both code-gen and kernel-native approaches via a single compiler.

#### Next steps

- Op coverage

- Performance

- Kernel libraries