## Enhancing MLGO Inlining with IR2Vec Embeddings

#### S. VenkataKeerthy

IIT Hyderabad, Google

US LLVM Developers' Meeting 28<sup>th</sup> October 2025

## **Program Representations**

## Features Vs. Embeddings

Features capture what we think is important; embeddings discover what is important.

| <b>%</b> Features                                | Embeddings                |

|--------------------------------------------------|---------------------------|

| Handcrafted                                      | Learned automatically     |

| Task-specific                                    | General-purpose, reusable |

| Shallow statistics (counts, depths, CFG metrics) | Deep semantics            |

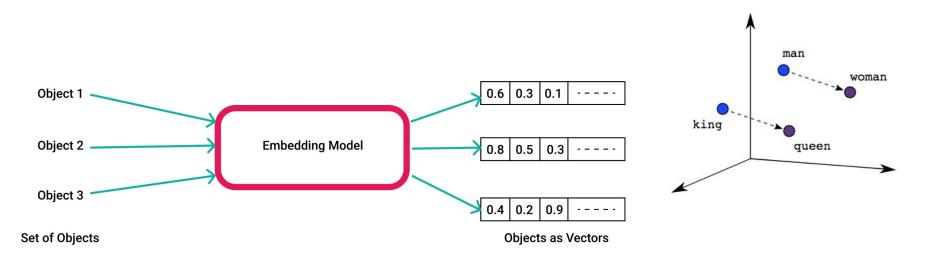

## Embeddings: Brief Background

Male-Female

## **Program Representations**

#### IR2Vec

#### **LLVM IR Based**

Language & Machine Independent Program Analysis based approach

#### **Distributed Encodings**

semantic meaning is 'distributed' across components of the vector

#### Agglomerative / Bottom-Up Approach

Doesn't need complex ML models Independent of Applications

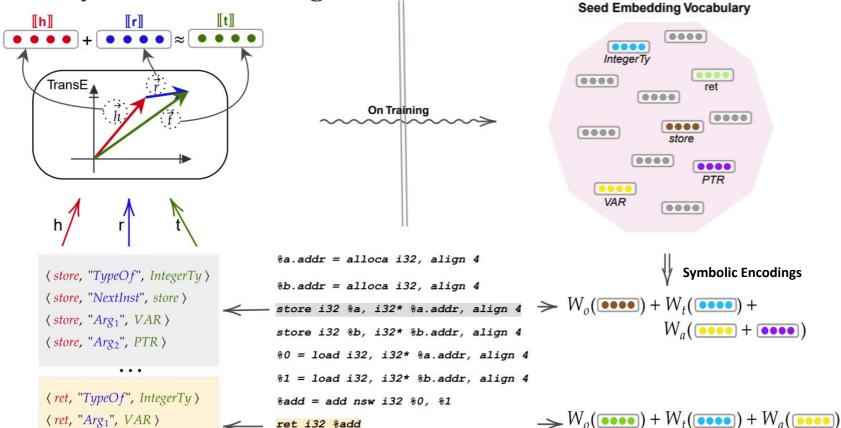

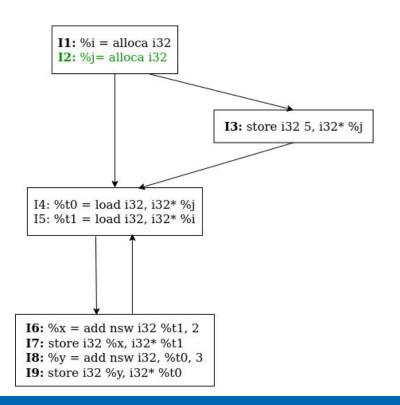

## IR2Vec (Symbolic Encodings)

## Flow-Aware Encodings: Symbolic + Flow Information

Improving Symbolic Encodings with Flow Information

$\llbracket \mathbf{I}_2 \rrbracket = W_o(\llbracket \mathbf{alloca} \rrbracket) + W_t(\llbracket \mathbf{IntegerTy} \rrbracket)$

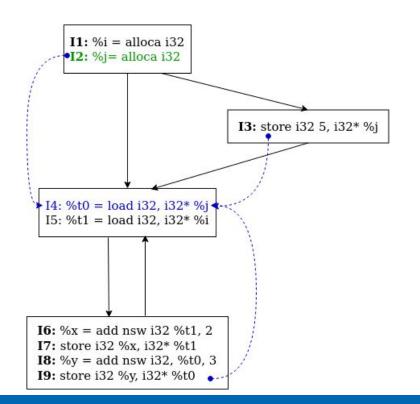

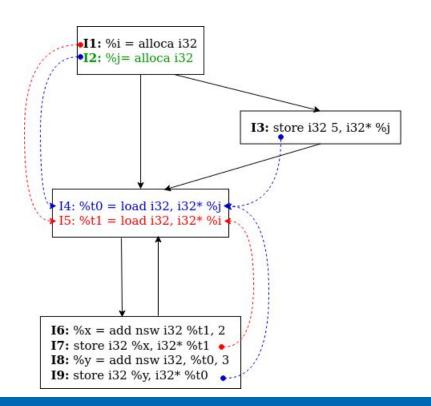

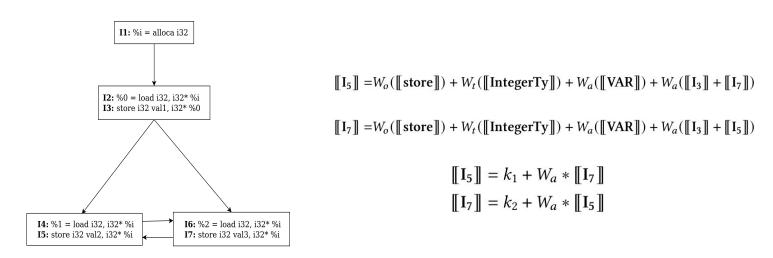

## Flow-Aware Encodings: Symbolic + Flow Information

Improving Symbolic Encodings with Flow Information

## Flow-Aware Encodings: Symbolic + Flow Information

Improving Symbolic Encodings with Flow Information

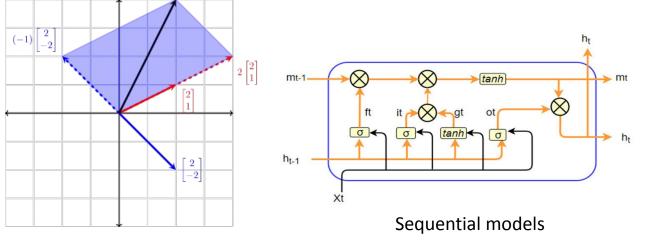

## Code Vectors: Beyond Instruction Representation

### Aggregators to effectively compose Instruction vectors

Non-Sequential models

**Linear Combination**

## Extensions to IR2Vec

#### IR2Vec

#### MIR2Vec

#### VexIR2Vec

- Machine Independent

- From Source Code

- Machine Specific

- From Source Code

- Machine Specific

- From Binary

#### IR2VEC: LLVM IR Based Scalable Program Embeddings

S. VENKATAKEERTHY, ROHIT AGGARWAL, SHALINI IAIN. MAUNENDRA SANKAR DESARKAR, and RAMAKRISHNA UPADRASTA, Indian Institute of Technology Hyderabad Y. N. SRIKANT, Indian Institute of Science

We propose IR2VEC, a Concise and Scalable encoding infrastructure to represent programs as a distributed embedding in continuous space. This distributed embedding is obtained by combining representation learning methods with flow information to capture the syntax as well as the semantics of the input programs. As our infrastructure is based on the Intermediate Representation (IR) of the source code, obtained embeddings are both language and machine independent. The entities of the IR are modeled as relationships, and their representations are learned to form a seed embedding vocabulary. Using this infrastructure, we propose two incremental encodings: Symbolic and Flow-Aware. Symbolic encodings are obtained from the seed embedding vocabulary, and Flow-Aware encodings are obtained by augmenting the Symbolic encodings with the flow

We show the effectiveness of our methodology on two optimization tasks (Heterogeneous device mapping and Thread coarsening). Our way of representing the programs enables us to use non-sequential models resulting in orders of magnitude of faster training time. Both the encodings generated by IR2VEC outperform the existing methods in both the tasks, even while using simple machine learning models. In particular, our results improve or match the state-of-the-art speedup in 11/14 benchmark-suites in the device mapping task across two platforms and 53/68 handsmarks in the thread governing task across four different platforms

#### RL4REAL: Reinforcement Learning for Register

Allocation Siddharth Jain S. VenkataKeerthy IIT Hyderabad

IIT Hydershad Rohit Aggarwal IIT Hyderabad

Albert Cohen

IIT Hyderabad Ramakrishna Unadrasta IIT Hydershad

Anilava Kundu

problem is reducible to graph coloring, which is one of the classical NP-Complete problems [8, 22]. Register allocation We aim to automate decades of research and experience in as an optimization involves additional sub-tasks, more than register allocation, leveraging machine learning. We tackle this problem by embedding a multi-agent reinforcement learning algorithm within LLVM, training it with the state of the art techniques. We formalize the constraints that precisely define the problem for a given instruction-set architecture, while ensuring that the generated code preserves semantic correctness. We also develop a gRPC based frame-

work providing a modular and efficient compiler interface

for training and inference. Our approach is architecture in-

graph coloring itself [8]. Several formulations have been proposed that return exact, or heuristic-based solutions. Broadly, solutions are often formulated as constraint-based optimizations [34, 38], ILP [3, 5, 12, 42], PBOP [31], gametheoretic approaches [45], and are fed to a variety of solvers. In general, these approaches are known to have scalability issues. On the other hand, heuristic-based approaches have been widely used owing to their scalability: reasonable solu-

#### VEXIR2VEC: An Architecture-Neutral Embedding Framework for Binary Similarity

S. VENKATAKEERTHY, SOUMYA BANERIEE, SAYAN DEY, YASHAS ANDALURI, RAGHUL PS, and SUBRAHMANYAM KALYANASUNDARAM, IIT Hyderabad, India FERNANDO MAGNO OUINTÃO PEREIRA, UFMG, Brazil

RAMAKRISHNA UPADRASTA, IIT Hyderabad, India

Binary similarity involves determining whether two binary programs exhibit similar functionality with applications in vulnerability detection, malware analysis, and copyright detection. However, variations in compiler settings, target architectures, and deliberate code obfuscations significantly complicate the similarity measurement by effectively altering the syntax, semantics, and structure of the underlying binary. To address these challenges, we propose VexIR2Vec, a robust, architecture-neutral approach based on VEX-IR to solve binary similarity tasks. VEXIR2VEC consists of three key components: a peephole extractor, a normalization engine (VexINE), and an embedding model (VexNet). The process to build program embeddings starts with the extraction of sequences of basic blocks, or peepholes, from control-flow graphs via random walks, capturing structural information. These generated peepholes are then normalized using VEXINE, which applies compilerinspired transformations to reduce architectural and compiler-induced variations. Embeddings of peepholes are generated

## IR2Vec in LLVM

- RFC and Discussions\*

- LLVM Upstreaming

- IR2Vec integrated under llvm/Analysis

- MIR2Vec in llvm/CodeGen

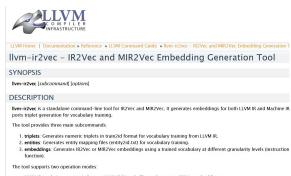

- llvm-ir2vec standalone tool in llvm/tools

- Supports embedding and vocab generation

- Upcoming

- Python library, installable via pip

- Source code (Research) <a href="https://github.com/IITH-Compilers/IR2Vec">https://github.com/IITH-Compilers/IR2Vec</a>

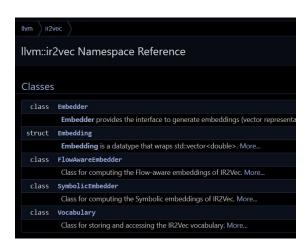

## IR2Vec in LLVM

- Vocabulary Analyses

- IR2VecVocabAnalysis, MIR2VecVocabLegacyAnalysis

- Embedder classes

- o ir2vec::Embedder, mir2vec::MIREmbedder

- Embeddings class

- O Wrapper around std::vector<double>

## Using IR2Vec

#### Programmatically in LLVM Passes

- Query vocabulary via IR2VecVocabAnalysis / MIR2VecVocabLegacyAnalysis

- Create an Embedder and extract embeddings at function or block or instruction level.

```

auto &VocabRes = MAM.getResult<IR2VecVocabAnalysis>(M);

if (!VocabRes.isValid()) { ... }

const ir2vec::Vocab &Vocabulary = VocabRes.getVocabulary();

auto Emb = ir2vec::Embedder::create(IR2VecKind::Symbolic, F, Vocabulary);

Embedding FVec = Emb->getFunctionVector();

```

## Using IR2Vec

Via standalone llvm-ir2vec Tool

Generates embeddings from .bc or .ll files.

llvm-ir2vec embeddings --ir2vec-vocab-path=vocab.json input.bc -o embeddings.txt

#### Vocabulary Training

11vm-ir2vec also helps in generating data for training vocabulary

```

llvm-ir2vec triplets input.bc -o train2id.txt

```

- Planning to automate the vocab generation

- see llvm/utils/mlgo-utils/IR2Vec/generateTriplets.py

## **ML-Driven Compiler Optimizations**

[VenkataKeerthy, et al, TACO'20]

ML-Compiler-Bridge

[VenkataKeerthy, Jain, et al, CC'24]

### **ML-Driven Optimizations**

#### **RL-Loop Distribution**

[Jain, VenkataKeerthy, et al, LLVM HPC'22]

# Phase Ordering (POSET-RL)

[Jain, VenkataKeerthy, et al, ISPASS'22]

## Register Allocation (RL4ReAl)

[VenkataKeerthy, Jain, et al, CC'23]

#### In LLVM

**Function Inlining**

Register Eviction in RegallocGreedy

\*Planned - MIR2Vec application

## **MLInlineAdvisor**

- Feature-based, Uses 32 hand-picked features

- Optimization for size

- PPO, ES, Imitation Learning based approaches

- C++ related code available in LLVM

- Python based training infra <a href="https://github.com/google/ml-compiler-opt">https://github.com/google/ml-compiler-opt</a>

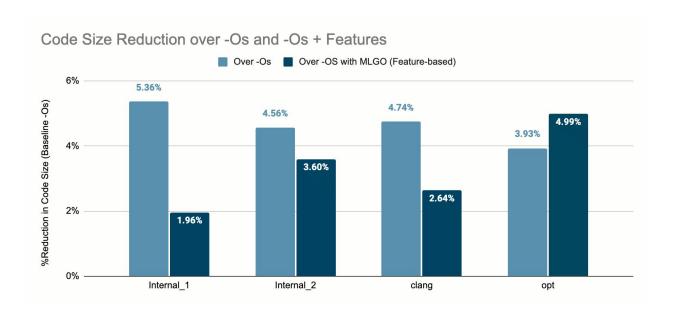

### IR2Vec with MLInlineAdvisor

#### Concatenating embeddings with features

Trained models from scratch on internal datacenter binaries, ~50K modules, PPO policy, ~20M steps

# Open Challenges & the road ahead

## Flow-Aware Embeddings: Cyclic dependencies!

### Linear Solver for Flow-Aware Embeddings / Cyclic Dependencies

#### Design trade-offs

- Simple linear solver Handwritten (where llvm/utils?) or eigen like libraries?

- Iterative solution

## **Encoding More Information**

- Memory dependences

- Memdep analysis or MemorySSA can make Flow-Aware embeddings more elegant

- But they are highly conservative!

- Embeddings can tolerate False-negatives unlike optimizations

- Specialize them?

- Biasing based on memtrace profiling?

- Profile Information

## MIR Vocabulary

- Vocabulary uses regex to group MIR opcodes (target specific)

- Eg: "ADD32rr" -> "ADD"

- This is mainly a learning quality enhancer

- x86 → 6.8K opcodes after grouping

- In comparison, IR2Vec vocab has only ~100 entities in total

- Need for better "canonicalization", beyond regex

- x86 has a systematic approach (uses TableGen)

- OpPrefix PD, PS, XS, XD, etc.

- Width 32, 64, etc.

- OpForm rm, rr, ri, etc.

- ...

- These prefixes and suffixes are attached with the "generic" opcodes

- But such an approach is not generalizable across architectures

## **Automating Vocab Generation**

- Buildbots to generate dataset (triplets) using the latest compiler

- On LLVM codebase

- Lightweight (<10 mins with 64 vCPUs)</li>

- Can also serve as an integration test

- Training Job on the generated data

- Uses the last generated dataset to train the vocabulary

- Can be less-frequent

## In Summary...

- IR2Vec: learned, scalable, architecture-independent program embeddings

- Upstreamed, addressed performance related issues, ready to use

- Aims to reduce and remove efforts towards feature engineering

- Demonstrates potential in both research and real-world production environments

### **Next Steps**

- Replace features, instead of concatenation

- Using MIR2Vec for eviction decisions in Regalloc Greedy

- Automating vocabulary training pipelines

- Improving Flow-Aware infrastructure

- ...

## Thank You!

S. VenkataKeerthy

https://svkeerthy.github.io

### **Acknowledgements**

Mircea Trofin, Albert Cohen, Ramakrishna Upadrasta, Other contributors and co-authors

Interested? Let's talk!

(discourse @svkeerthy)