#include "Target/AMDGPU/AMDGPUTargetMachine.h"

Additional Inherited Members | |

Protected Types inherited from llvm::CodeGenPassBuilder< AMDGPUCodeGenPassBuilder, GCNTargetMachine > Protected Types inherited from llvm::CodeGenPassBuilder< AMDGPUCodeGenPassBuilder, GCNTargetMachine > | |

| using | has_required_t = decltype(std::declval< PassT & >().isRequired()) |

| using | is_module_pass_t = decltype(std::declval< PassT & >().run(std::declval< Module & >(), std::declval< ModuleAnalysisManager & >())) |

| using | is_function_pass_t = decltype(std::declval< PassT & >().run(std::declval< Function & >(), std::declval< FunctionAnalysisManager & >())) |

| using | is_machine_function_pass_t = decltype(std::declval< PassT & >().run(std::declval< MachineFunction & >(), std::declval< MachineFunctionAnalysisManager & >())) |

| using | CreateMCStreamer = std::function< Expected< std::unique_ptr< MCStreamer > >(MCContext &)> |

Protected Member Functions inherited from llvm::CodeGenPassBuilder< AMDGPUCodeGenPassBuilder, GCNTargetMachine > Protected Member Functions inherited from llvm::CodeGenPassBuilder< AMDGPUCodeGenPassBuilder, GCNTargetMachine > | |

| TMC & | getTM () const |

| CodeGenOptLevel | getOptLevel () const |

| bool | isGlobalISelAbortEnabled () const |

| Check whether or not GlobalISel should abort on error. | |

| bool | reportDiagnosticWhenGlobalISelFallback () const |

| Check whether or not a diagnostic should be emitted when GlobalISel uses the fallback path. | |

| Error | addInstSelector (AddMachinePass &) const |

| addInstSelector - This method should install an instruction selector pass, which converts from LLVM code to machine instructions. | |

| void | addGlobalMergePass (AddIRPass &) const |

| Target can override this to add GlobalMergePass before all IR passes. | |

| void | addILPOpts (AddMachinePass &) const |

| Add passes that optimize instruction level parallelism for out-of-order targets. | |

| void | addPreRegAlloc (AddMachinePass &) const |

| This method may be implemented by targets that want to run passes immediately before register allocation. | |

| void | addPreRewrite (AddMachinePass &) const |

| addPreRewrite - Add passes to the optimized register allocation pipeline after register allocation is complete, but before virtual registers are rewritten to physical registers. | |

| void | addPostRewrite (AddMachinePass &) const |

| Add passes to be run immediately after virtual registers are rewritten to physical registers. | |

| void | addPostRegAlloc (AddMachinePass &) const |

| This method may be implemented by targets that want to run passes after register allocation pass pipeline but before prolog-epilog insertion. | |

| void | addPreSched2 (AddMachinePass &) const |

| This method may be implemented by targets that want to run passes after prolog-epilog insertion and before the second instruction scheduling pass. | |

| void | addPreEmitPass (AddMachinePass &) const |

| This pass may be implemented by targets that want to run passes immediately before machine code is emitted. | |

| void | addPreEmitPass2 (AddMachinePass &) const |

| Targets may add passes immediately before machine code is emitted in this callback. | |

| void | addPreISel (AddIRPass &) const |

| {{@ For GlobalISel | |

| Error | addIRTranslator (AddMachinePass &) const |

| This method should install an IR translator pass, which converts from LLVM code to machine instructions with possibly generic opcodes. | |

| void | addPreLegalizeMachineIR (AddMachinePass &) const |

| This method may be implemented by targets that want to run passes immediately before legalization. | |

| Error | addLegalizeMachineIR (AddMachinePass &) const |

| This method should install a legalize pass, which converts the instruction sequence into one that can be selected by the target. | |

| void | addPreRegBankSelect (AddMachinePass &) const |

| This method may be implemented by targets that want to run passes immediately before the register bank selection. | |

| Error | addRegBankSelect (AddMachinePass &) const |

| This method should install a register bank selector pass, which assigns register banks to virtual registers without a register class or register banks. | |

| void | addPreGlobalInstructionSelect (AddMachinePass &) const |

| This method may be implemented by targets that want to run passes immediately before the (global) instruction selection. | |

| Error | addGlobalInstructionSelect (AddMachinePass &) const |

| This method should install a (global) instruction selector pass, which converts possibly generic instructions to fully target-specific instructions, thereby constraining all generic virtual registers to register classes. | |

| void | addISelPasses (AddIRPass &) const |

| High level function that adds all passes necessary to go from llvm IR representation to the MI representation. | |

| Error | addCoreISelPasses (AddMachinePass &) const |

| Add the actual instruction selection passes. | |

| Error | addMachinePasses (AddMachinePass &) const |

| Add the complete, standard set of LLVM CodeGen passes. | |

| void | addPassesToHandleExceptions (AddIRPass &) const |

| Add passes to lower exception handling for the code generator. | |

| void | addIRPasses (AddIRPass &) const |

| Add common target configurable passes that perform LLVM IR to IR transforms following machine independent optimization. | |

| void | addCodeGenPrepare (AddIRPass &) const |

| Add pass to prepare the LLVM IR for code generation. | |

| void | addISelPrepare (AddIRPass &) const |

| Add common passes that perform LLVM IR to IR transforms in preparation for instruction selection. | |

| void | addMachineSSAOptimization (AddMachinePass &) const |

| Methods with trivial inline returns are convenient points in the common codegen pass pipeline where targets may insert passes. | |

| Error | addFastRegAlloc (AddMachinePass &) const |

| addFastRegAlloc - Add the minimum set of target-independent passes that are required for fast register allocation. | |

| void | addOptimizedRegAlloc (AddMachinePass &) const |

| addOptimizedRegAlloc - Add passes related to register allocation. | |

| void | addMachineLateOptimization (AddMachinePass &) const |

| Add passes that optimize machine instructions after register allocation. | |

| void | addGCPasses (AddMachinePass &) const |

| addGCPasses - Add late codegen passes that analyze code for garbage collection. | |

| void | addBlockPlacement (AddMachinePass &) const |

| Add standard basic block placement passes. | |

| void | addAsmPrinter (AddMachinePass &, CreateMCStreamer) const |

| void | addTargetRegisterAllocator (AddMachinePass &, bool Optimized) const |

| Utilities for targets to add passes to the pass manager. | |

| void | addRegAllocPass (AddMachinePass &, bool Optimized) const |

| addMachinePasses helper to create the target-selected or overriden regalloc pass. | |

| Error | addRegAssignmentFast (AddMachinePass &) const |

| Add core register alloator passes which do the actual register assignment and rewriting. | |

| Error | addRegAssignmentOptimized (AddMachinePass &) const |

| void | disablePass () |

| Allow the target to disable a specific pass by default. | |

| void | insertPass (InsertedPassT &&Pass) |

| Insert InsertedPass pass after TargetPass pass. | |

Protected Attributes inherited from llvm::CodeGenPassBuilder< AMDGPUCodeGenPassBuilder, GCNTargetMachine > Protected Attributes inherited from llvm::CodeGenPassBuilder< AMDGPUCodeGenPassBuilder, GCNTargetMachine > | |

| GCNTargetMachine & | TM |

| CGPassBuilderOption | Opt |

| PassInstrumentationCallbacks * | PIC |

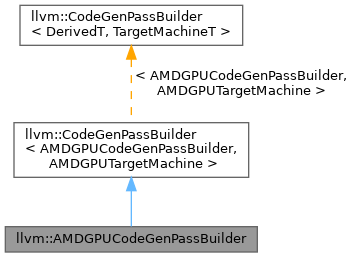

Detailed Description

Definition at line 163 of file AMDGPUTargetMachine.h.

Constructor & Destructor Documentation

◆ AMDGPUCodeGenPassBuilder()

| AMDGPUCodeGenPassBuilder::AMDGPUCodeGenPassBuilder | ( | GCNTargetMachine & | TM, |

| const CGPassBuilderOption & | Opts, | ||

| PassInstrumentationCallbacks * | PIC | ||

| ) |

Member Function Documentation

◆ addAsmPrinter()

| void AMDGPUCodeGenPassBuilder::addAsmPrinter | ( | AddMachinePass & | addPass, |

| CreateMCStreamer | |||

| ) | const |

Definition at line 2077 of file AMDGPUTargetMachine.cpp.

◆ addCodeGenPrepare()

| void AMDGPUCodeGenPassBuilder::addCodeGenPrepare | ( | AddIRPass & | addPass | ) | const |

Definition at line 1996 of file AMDGPUTargetMachine.cpp.

References llvm::CodeGenPassBuilder< AMDGPUCodeGenPassBuilder, GCNTargetMachine >::addCodeGenPrepare(), EnableLoadStoreVectorizer, EnableLowerKernelArguments, isPassEnabled(), and llvm::CodeGenPassBuilder< AMDGPUCodeGenPassBuilder, GCNTargetMachine >::TM.

◆ addEarlyCSEOrGVNPass()

| void AMDGPUCodeGenPassBuilder::addEarlyCSEOrGVNPass | ( | AddIRPass & | addPass | ) | const |

Definition at line 2117 of file AMDGPUTargetMachine.cpp.

References llvm::Aggressive, llvm::TargetMachine::getOptLevel(), and llvm::CodeGenPassBuilder< AMDGPUCodeGenPassBuilder, GCNTargetMachine >::TM.

Referenced by addIRPasses(), and addStraightLineScalarOptimizationPasses().

◆ addILPOpts()

| void AMDGPUCodeGenPassBuilder::addILPOpts | ( | AddMachinePass & | addPass | ) | const |

Definition at line 2070 of file AMDGPUTargetMachine.cpp.

References llvm::CodeGenPassBuilder< AMDGPUCodeGenPassBuilder, GCNTargetMachine >::addILPOpts(), and EnableEarlyIfConversion.

◆ addInstSelector()

| Error AMDGPUCodeGenPassBuilder::addInstSelector | ( | AddMachinePass & | addPass | ) | const |

Definition at line 2082 of file AMDGPUTargetMachine.cpp.

References llvm::Error::success(), and llvm::CodeGenPassBuilder< AMDGPUCodeGenPassBuilder, GCNTargetMachine >::TM.

◆ addIRPasses()

| void AMDGPUCodeGenPassBuilder::addIRPasses | ( | AddIRPass & | addPass | ) | const |

Definition at line 1931 of file AMDGPUTargetMachine.cpp.

References addEarlyCSEOrGVNPass(), llvm::CodeGenPassBuilder< AMDGPUCodeGenPassBuilder, GCNTargetMachine >::addIRPasses(), addStraightLineScalarOptimizationPasses(), AMDGPUAtomicOptimizerStrategy, EnableImageIntrinsicOptimizer, EnableLowerModuleLDS, EnableScalarIRPasses, llvm::TargetMachine::getOptLevel(), llvm::TargetMachine::getTargetTriple(), llvm::Triple::isAMDGCN(), isPassEnabled(), llvm::Less, LowerCtorDtor, llvm::Lowering, llvm::None, RemoveIncompatibleFunctions, and llvm::CodeGenPassBuilder< AMDGPUCodeGenPassBuilder, GCNTargetMachine >::TM.

◆ addMachineSSAOptimization()

| void AMDGPUCodeGenPassBuilder::addMachineSSAOptimization | ( | AddMachinePass & | addPass | ) | const |

Definition at line 2089 of file AMDGPUTargetMachine.cpp.

References llvm::CodeGenPassBuilder< AMDGPUCodeGenPassBuilder, GCNTargetMachine >::addMachineSSAOptimization(), EnableDPPCombine, EnableSDWAPeephole, and isPassEnabled().

◆ addPreISel()

| void AMDGPUCodeGenPassBuilder::addPreISel | ( | AddIRPass & | addPass | ) | const |

Definition at line 2033 of file AMDGPUTargetMachine.cpp.

References llvm::TargetMachine::getOptLevel(), llvm::Less, llvm::None, and llvm::CodeGenPassBuilder< AMDGPUCodeGenPassBuilder, GCNTargetMachine >::TM.

◆ addStraightLineScalarOptimizationPasses()

| void AMDGPUCodeGenPassBuilder::addStraightLineScalarOptimizationPasses | ( | AddIRPass & | addPass | ) | const |

Definition at line 2124 of file AMDGPUTargetMachine.cpp.

References addEarlyCSEOrGVNPass(), llvm::Aggressive, EnableLoopPrefetch, and isPassEnabled().

Referenced by addIRPasses().

◆ isPassEnabled()

| bool AMDGPUCodeGenPassBuilder::isPassEnabled | ( | const cl::opt< bool > & | Opt, |

| CodeGenOptLevel | Level = CodeGenOptLevel::Default |

||

| ) | const |

Check if a pass is enabled given Opt option.

The option always overrides defaults if explicitly used. Otherwise its default will be used given that a pass shall work at an optimization Level minimum.

Definition at line 2108 of file AMDGPUTargetMachine.cpp.

References llvm::TargetMachine::getOptLevel(), llvm::CodeGenPassBuilder< AMDGPUCodeGenPassBuilder, GCNTargetMachine >::Opt, and llvm::CodeGenPassBuilder< AMDGPUCodeGenPassBuilder, GCNTargetMachine >::TM.

Referenced by addCodeGenPrepare(), addIRPasses(), addMachineSSAOptimization(), and addStraightLineScalarOptimizationPasses().

The documentation for this class was generated from the following files:

- lib/Target/AMDGPU/AMDGPUTargetMachine.h

- lib/Target/AMDGPU/AMDGPUTargetMachine.cpp