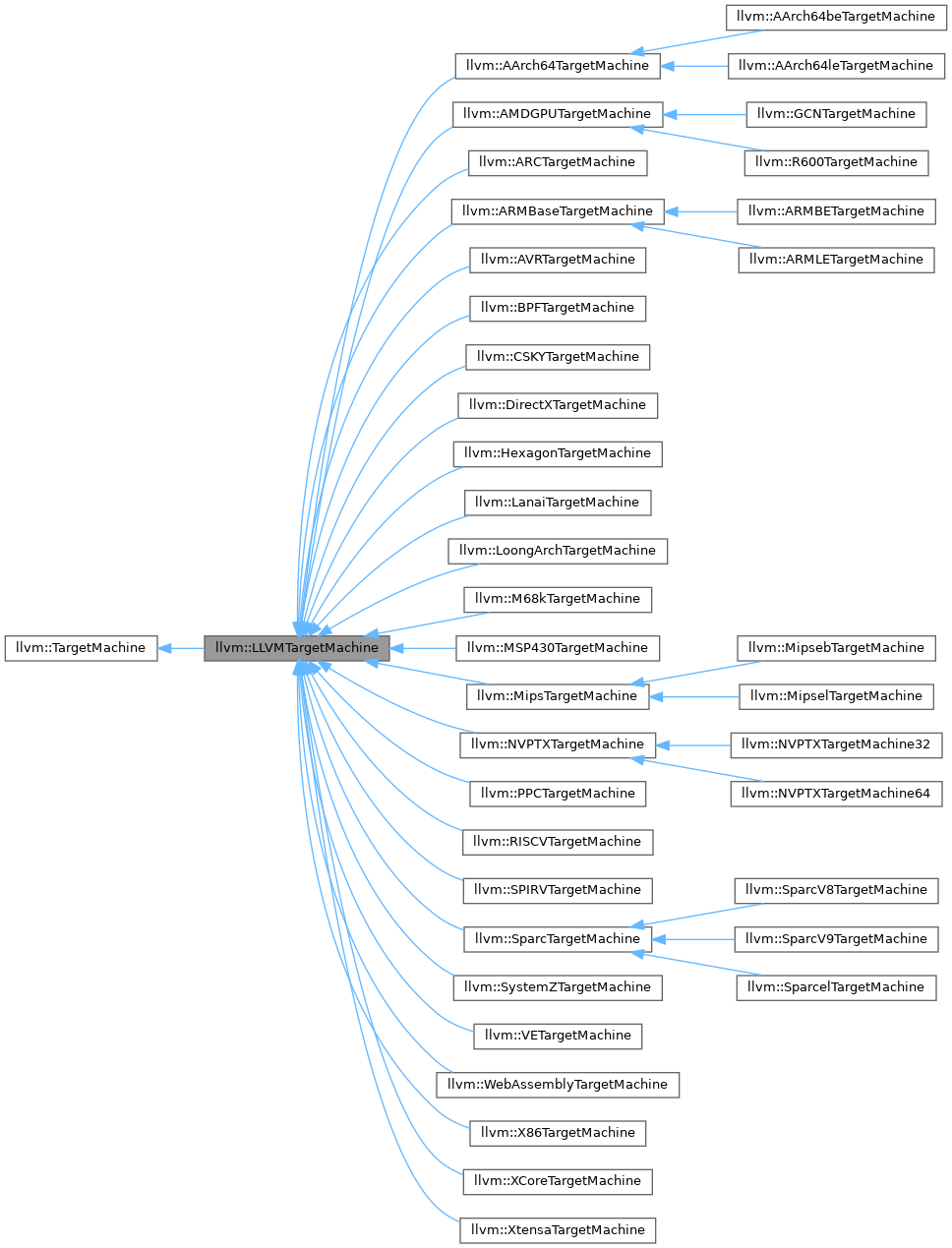

This class describes a target machine that is implemented with the LLVM target-independent code generator. More...

#include "llvm/Target/TargetMachine.h"

Public Member Functions | |

| TargetTransformInfo | getTargetTransformInfo (const Function &F) const override |

| Get a TargetTransformInfo implementation for the target. | |

| virtual TargetPassConfig * | createPassConfig (PassManagerBase &PM) |

| Create a pass configuration object to be used by addPassToEmitX methods for generating a pipeline of CodeGen passes. | |

| bool | addPassesToEmitFile (PassManagerBase &PM, raw_pwrite_stream &Out, raw_pwrite_stream *DwoOut, CodeGenFileType FileType, bool DisableVerify=true, MachineModuleInfoWrapperPass *MMIWP=nullptr) override |

| Add passes to the specified pass manager to get the specified file emitted. | |

| virtual Error | buildCodeGenPipeline (ModulePassManager &, raw_pwrite_stream &, raw_pwrite_stream *, CodeGenFileType, const CGPassBuilderOption &, PassInstrumentationCallbacks *) |

| bool | addPassesToEmitMC (PassManagerBase &PM, MCContext *&Ctx, raw_pwrite_stream &Out, bool DisableVerify=true) override |

| Add passes to the specified pass manager to get machine code emitted with the MCJIT. | |

| virtual bool | isMachineVerifierClean () const |

| Returns true if the target is expected to pass all machine verifier checks. | |

| bool | addAsmPrinter (PassManagerBase &PM, raw_pwrite_stream &Out, raw_pwrite_stream *DwoOut, CodeGenFileType FileType, MCContext &Context) |

| Adds an AsmPrinter pass to the pipeline that prints assembly or machine code from the MI representation. | |

| Expected< std::unique_ptr< MCStreamer > > | createMCStreamer (raw_pwrite_stream &Out, raw_pwrite_stream *DwoOut, CodeGenFileType FileType, MCContext &Ctx) |

| virtual bool | usesPhysRegsForValues () const |

| True if the target uses physical regs (as nearly all targets do). | |

| virtual bool | useIPRA () const |

| True if the target wants to use interprocedural register allocation by default. | |

| virtual int | unqualifiedInlineAsmVariant () const |

The default variant to use in unqualified asm instructions. | |

| virtual void | registerMachineRegisterInfoCallback (MachineFunction &MF) const |

Public Member Functions inherited from llvm::TargetMachine Public Member Functions inherited from llvm::TargetMachine | |

| TargetMachine (const TargetMachine &)=delete | |

| void | operator= (const TargetMachine &)=delete |

| virtual | ~TargetMachine () |

| const Target & | getTarget () const |

| const Triple & | getTargetTriple () const |

| StringRef | getTargetCPU () const |

| StringRef | getTargetFeatureString () const |

| void | setTargetFeatureString (StringRef FS) |

| virtual const TargetSubtargetInfo * | getSubtargetImpl (const Function &) const |

| Virtual method implemented by subclasses that returns a reference to that target's TargetSubtargetInfo-derived member variable. | |

| virtual TargetLoweringObjectFile * | getObjFileLowering () const |

| virtual MachineFunctionInfo * | createMachineFunctionInfo (BumpPtrAllocator &Allocator, const Function &F, const TargetSubtargetInfo *STI) const |

| Create the target's instance of MachineFunctionInfo. | |

| virtual yaml::MachineFunctionInfo * | createDefaultFuncInfoYAML () const |

| Allocate and return a default initialized instance of the YAML representation for the MachineFunctionInfo. | |

| virtual yaml::MachineFunctionInfo * | convertFuncInfoToYAML (const MachineFunction &MF) const |

| Allocate and initialize an instance of the YAML representation of the MachineFunctionInfo. | |

| virtual bool | parseMachineFunctionInfo (const yaml::MachineFunctionInfo &, PerFunctionMIParsingState &PFS, SMDiagnostic &Error, SMRange &SourceRange) const |

| Parse out the target's MachineFunctionInfo from the YAML reprsentation. | |

| template<typename STC > | |

| const STC & | getSubtarget (const Function &F) const |

| This method returns a pointer to the specified type of TargetSubtargetInfo. | |

| const DataLayout | createDataLayout () const |

| Create a DataLayout. | |

| bool | isCompatibleDataLayout (const DataLayout &Candidate) const |

| Test if a DataLayout if compatible with the CodeGen for this target. | |

| unsigned | getPointerSize (unsigned AS) const |

| Get the pointer size for this target. | |

| unsigned | getPointerSizeInBits (unsigned AS) const |

| unsigned | getProgramPointerSize () const |

| unsigned | getAllocaPointerSize () const |

| void | resetTargetOptions (const Function &F) const |

| Reset the target options based on the function's attributes. | |

| const MCAsmInfo * | getMCAsmInfo () const |

| Return target specific asm information. | |

| const MCRegisterInfo * | getMCRegisterInfo () const |

| const MCInstrInfo * | getMCInstrInfo () const |

| const MCSubtargetInfo * | getMCSubtargetInfo () const |

| virtual const TargetIntrinsicInfo * | getIntrinsicInfo () const |

| If intrinsic information is available, return it. If not, return null. | |

| bool | requiresStructuredCFG () const |

| void | setRequiresStructuredCFG (bool Value) |

| Reloc::Model | getRelocationModel () const |

| Returns the code generation relocation model. | |

| CodeModel::Model | getCodeModel () const |

| Returns the code model. | |

| uint64_t | getMaxCodeSize () const |

| Returns the maximum code size possible under the code model. | |

| void | setCodeModel (CodeModel::Model CM) |

| Set the code model. | |

| void | setLargeDataThreshold (uint64_t LDT) |

| bool | isLargeGlobalValue (const GlobalValue *GV) const |

| bool | isPositionIndependent () const |

| bool | shouldAssumeDSOLocal (const GlobalValue *GV) const |

| bool | useEmulatedTLS () const |

| Returns true if this target uses emulated TLS. | |

| bool | useTLSDESC () const |

| Returns true if this target uses TLS Descriptors. | |

| TLSModel::Model | getTLSModel (const GlobalValue *GV) const |

| Returns the TLS model which should be used for the given global variable. | |

| CodeGenOptLevel | getOptLevel () const |

| Returns the optimization level: None, Less, Default, or Aggressive. | |

| void | setOptLevel (CodeGenOptLevel Level) |

| Overrides the optimization level. | |

| void | setFastISel (bool Enable) |

| bool | getO0WantsFastISel () |

| void | setO0WantsFastISel (bool Enable) |

| void | setGlobalISel (bool Enable) |

| void | setGlobalISelAbort (GlobalISelAbortMode Mode) |

| void | setMachineOutliner (bool Enable) |

| void | setSupportsDefaultOutlining (bool Enable) |

| void | setSupportsDebugEntryValues (bool Enable) |

| void | setCFIFixup (bool Enable) |

| bool | getAIXExtendedAltivecABI () const |

| bool | getUniqueSectionNames () const |

| bool | getUniqueBasicBlockSectionNames () const |

| Return true if unique basic block section names must be generated. | |

| bool | getSeparateNamedSections () const |

| bool | getDataSections () const |

| Return true if data objects should be emitted into their own section, corresponds to -fdata-sections. | |

| bool | getFunctionSections () const |

| Return true if functions should be emitted into their own section, corresponding to -ffunction-sections. | |

| bool | getIgnoreXCOFFVisibility () const |

| Return true if visibility attribute should not be emitted in XCOFF, corresponding to -mignore-xcoff-visibility. | |

| bool | getXCOFFTracebackTable () const |

| Return true if XCOFF traceback table should be emitted, corresponding to -xcoff-traceback-table. | |

| llvm::BasicBlockSection | getBBSectionsType () const |

| If basic blocks should be emitted into their own section, corresponding to -fbasic-block-sections. | |

| const MemoryBuffer * | getBBSectionsFuncListBuf () const |

| Get the list of functions and basic block ids that need unique sections. | |

| virtual bool | isNoopAddrSpaceCast (unsigned SrcAS, unsigned DestAS) const |

| Returns true if a cast between SrcAS and DestAS is a noop. | |

| void | setPGOOption (std::optional< PGOOptions > PGOOpt) |

| const std::optional< PGOOptions > & | getPGOOption () const |

| virtual unsigned | getAssumedAddrSpace (const Value *V) const |

| If the specified generic pointer could be assumed as a pointer to a specific address space, return that address space. | |

| virtual std::pair< const Value *, unsigned > | getPredicatedAddrSpace (const Value *V) const |

| If the specified predicate checks whether a generic pointer falls within a specified address space, return that generic pointer and the address space being queried. | |

| TargetIRAnalysis | getTargetIRAnalysis () const |

Get a TargetIRAnalysis appropriate for the target. | |

| virtual TargetTransformInfo | getTargetTransformInfo (const Function &F) const |

| Return a TargetTransformInfo for a given function. | |

| virtual void | registerPassBuilderCallbacks (PassBuilder &) |

| Allow the target to modify the pass pipeline. | |

| virtual void | registerDefaultAliasAnalyses (AAManager &) |

| Allow the target to register alias analyses with the AAManager for use with the new pass manager. | |

| virtual bool | addPassesToEmitFile (PassManagerBase &, raw_pwrite_stream &, raw_pwrite_stream *, CodeGenFileType, bool=true, MachineModuleInfoWrapperPass *MMIWP=nullptr) |

| Add passes to the specified pass manager to get the specified file emitted. | |

| virtual bool | addPassesToEmitMC (PassManagerBase &, MCContext *&, raw_pwrite_stream &, bool=true) |

| Add passes to the specified pass manager to get machine code emitted with the MCJIT. | |

| virtual bool | targetSchedulesPostRAScheduling () const |

| True if subtarget inserts the final scheduling pass on its own. | |

| void | getNameWithPrefix (SmallVectorImpl< char > &Name, const GlobalValue *GV, Mangler &Mang, bool MayAlwaysUsePrivate=false) const |

| MCSymbol * | getSymbol (const GlobalValue *GV) const |

| virtual unsigned | getSjLjDataSize () const |

| virtual unsigned | getAddressSpaceForPseudoSourceKind (unsigned Kind) const |

| getAddressSpaceForPseudoSourceKind - Given the kind of memory (e.g. | |

| virtual bool | splitModule (Module &M, unsigned NumParts, function_ref< void(std::unique_ptr< Module > MPart)> ModuleCallback) |

| Entry point for module splitting. | |

Protected Member Functions | |

| LLVMTargetMachine (const Target &T, StringRef DataLayoutString, const Triple &TT, StringRef CPU, StringRef FS, const TargetOptions &Options, Reloc::Model RM, CodeModel::Model CM, CodeGenOptLevel OL) | |

| void | initAsmInfo () |

Protected Member Functions inherited from llvm::TargetMachine Protected Member Functions inherited from llvm::TargetMachine | |

| TargetMachine (const Target &T, StringRef DataLayoutString, const Triple &TargetTriple, StringRef CPU, StringRef FS, const TargetOptions &Options) | |

Additional Inherited Members | |

Static Public Member Functions inherited from llvm::TargetMachine Static Public Member Functions inherited from llvm::TargetMachine | |

| static std::pair< int, int > | parseBinutilsVersion (StringRef Version) |

Public Attributes inherited from llvm::TargetMachine Public Attributes inherited from llvm::TargetMachine | |

| TargetOptions | Options |

Static Public Attributes inherited from llvm::TargetMachine Static Public Attributes inherited from llvm::TargetMachine | |

| static constexpr unsigned | DefaultSjLjDataSize = 32 |

| The integer bit size to use for SjLj based exception handling. | |

Protected Attributes inherited from llvm::TargetMachine Protected Attributes inherited from llvm::TargetMachine | |

| const Target & | TheTarget |

| The Target that this machine was created for. | |

| const DataLayout | DL |

| DataLayout for the target: keep ABI type size and alignment. | |

| Triple | TargetTriple |

| Triple string, CPU name, and target feature strings the TargetMachine instance is created with. | |

| std::string | TargetCPU |

| std::string | TargetFS |

| Reloc::Model | RM = Reloc::Static |

| CodeModel::Model | CMModel = CodeModel::Small |

| uint64_t | LargeDataThreshold = 0 |

| CodeGenOptLevel | OptLevel = CodeGenOptLevel::Default |

| std::unique_ptr< const MCAsmInfo > | AsmInfo |

| Contains target specific asm information. | |

| std::unique_ptr< const MCRegisterInfo > | MRI |

| std::unique_ptr< const MCInstrInfo > | MII |

| std::unique_ptr< const MCSubtargetInfo > | STI |

| unsigned | RequireStructuredCFG: 1 |

| unsigned | O0WantsFastISel: 1 |

| std::optional< PGOOptions > | PGOOption |

Detailed Description

This class describes a target machine that is implemented with the LLVM target-independent code generator.

Definition at line 442 of file TargetMachine.h.

Constructor & Destructor Documentation

◆ LLVMTargetMachine()

|

protected |

Definition at line 88 of file LLVMTargetMachine.cpp.

References llvm::TargetMachine::CMModel, EnableNoTrapAfterNoreturn, EnableTrapUnreachable, llvm::TargetOptions::NoTrapAfterNoreturn, llvm::TargetMachine::OptLevel, llvm::TargetMachine::RM, and llvm::TargetOptions::TrapUnreachable.

Member Function Documentation

◆ addAsmPrinter()

| bool LLVMTargetMachine::addAsmPrinter | ( | PassManagerBase & | PM, |

| raw_pwrite_stream & | Out, | ||

| raw_pwrite_stream * | DwoOut, | ||

| CodeGenFileType | FileType, | ||

| MCContext & | Context | ||

| ) |

Adds an AsmPrinter pass to the pipeline that prints assembly or machine code from the MI representation.

Definition at line 130 of file LLVMTargetMachine.cpp.

References llvm::legacy::PassManagerBase::add(), llvm::Target::createAsmPrinter(), createMCStreamer(), llvm::TargetMachine::getTarget(), Printer, and llvm::Expected< T >::takeError().

Referenced by llvm::DirectXTargetMachine::addPassesToEmitFile(), and addPassesToEmitFile().

◆ addPassesToEmitFile()

|

overridevirtual |

Add passes to the specified pass manager to get the specified file emitted.

Typically this will involve several steps of code generation. MMIWP is an optional parameter that, if set to non-nullptr, will be used to set the MachineModuloInfo for this PM.

Reimplemented from llvm::TargetMachine.

Reimplemented in llvm::DirectXTargetMachine.

Definition at line 209 of file LLVMTargetMachine.cpp.

References llvm::legacy::PassManagerBase::add(), addAsmPrinter(), addPassesToGenerateCode(), llvm::createFreeMachineFunctionPass(), llvm::createPrintMIRPass(), llvm::MachineModuleInfo::getContext(), llvm::MachineModuleInfoWrapperPass::getMMI(), llvm::Null, and llvm::TargetPassConfig::willCompleteCodeGenPipeline().

◆ addPassesToEmitMC()

|

overridevirtual |

Add passes to the specified pass manager to get machine code emitted with the MCJIT.

addPassesToEmitMC - Add passes to the specified pass manager to get machine code emitted with the MCJIT.

This method returns true if machine code is not supported. It fills the MCContext Ctx pointer which can be used to build custom MCStreamer.

Reimplemented from llvm::TargetMachine.

Reimplemented in llvm::NVPTXTargetMachine, and llvm::DirectXTargetMachine.

Definition at line 239 of file LLVMTargetMachine.cpp.

References llvm::legacy::PassManagerBase::add(), addPassesToGenerateCode(), llvm::Always, assert(), llvm::Target::createAsmPrinter(), llvm::createFreeMachineFunctionPass(), llvm::Target::createMCAsmBackend(), llvm::MCAsmBackend::createObjectWriter(), llvm::MCTargetOptions::EmitDwarfUnwind, llvm::MachineModuleInfo::getContext(), llvm::TargetMachine::getMCInstrInfo(), llvm::TargetMachine::getMCRegisterInfo(), llvm::TargetMachine::getMCSubtargetInfo(), llvm::MachineModuleInfoWrapperPass::getMMI(), llvm::TargetMachine::getTarget(), llvm::TargetMachine::getTargetTriple(), llvm::TargetOptions::MCOptions, llvm::TargetMachine::MRI, llvm::TargetMachine::Options, Printer, llvm::TargetMachine::STI, and llvm::TargetPassConfig::willCompleteCodeGenPipeline().

◆ buildCodeGenPipeline()

|

inlinevirtual |

Reimplemented in llvm::X86TargetMachine, llvm::R600TargetMachine, and llvm::GCNTargetMachine.

Definition at line 472 of file TargetMachine.h.

References llvm::inconvertibleErrorCode().

◆ createMCStreamer()

| Expected< std::unique_ptr< MCStreamer > > LLVMTargetMachine::createMCStreamer | ( | raw_pwrite_stream & | Out, |

| raw_pwrite_stream * | DwoOut, | ||

| CodeGenFileType | FileType, | ||

| MCContext & | Ctx | ||

| ) |

Definition at line 150 of file LLVMTargetMachine.cpp.

References llvm::AssemblyFile, llvm::Target::createAsmStreamer(), llvm::MCAsmBackend::createDwoObjectWriter(), llvm::Target::createMCAsmBackend(), llvm::Target::createMCCodeEmitter(), llvm::Target::createMCInstPrinter(), llvm::createNullStreamer(), llvm::MCAsmBackend::createObjectWriter(), llvm::MCAsmInfo::getAssemblerDialect(), llvm::TargetMachine::getMCAsmInfo(), llvm::TargetMachine::getMCInstrInfo(), llvm::TargetMachine::getMCRegisterInfo(), llvm::TargetMachine::getMCSubtargetInfo(), llvm::TargetMachine::getTarget(), llvm::TargetMachine::getTargetTriple(), llvm::inconvertibleErrorCode(), llvm::TargetOptions::MCOptions, llvm::TargetMachine::MII, llvm::TargetMachine::MRI, llvm::Null, llvm::ObjectFile, llvm::TargetMachine::Options, llvm::MCStreamer::reset(), llvm::MCTargetOptions::ShowMCEncoding, and llvm::TargetMachine::STI.

Referenced by addAsmPrinter().

◆ createPassConfig()

|

virtual |

Create a pass configuration object to be used by addPassToEmitX methods for generating a pipeline of CodeGen passes.

createPassConfig - Create a pass configuration object to be used by addPassToEmitX methods for generating a pipeline of CodeGen passes.

Targets may override this to extend TargetPassConfig.

Reimplemented in llvm::LanaiTargetMachine, llvm::AArch64TargetMachine, llvm::GCNTargetMachine, llvm::R600TargetMachine, llvm::ARCTargetMachine, llvm::ARMBaseTargetMachine, llvm::AVRTargetMachine, llvm::BPFTargetMachine, llvm::CSKYTargetMachine, llvm::DirectXTargetMachine, llvm::HexagonTargetMachine, llvm::LoongArchTargetMachine, llvm::M68kTargetMachine, llvm::MipsTargetMachine, llvm::MSP430TargetMachine, llvm::NVPTXTargetMachine, llvm::PPCTargetMachine, llvm::RISCVTargetMachine, llvm::SparcTargetMachine, llvm::SPIRVTargetMachine, llvm::SystemZTargetMachine, llvm::VETargetMachine, llvm::WebAssemblyTargetMachine, llvm::X86TargetMachine, llvm::XCoreTargetMachine, and llvm::XtensaTargetMachine.

Definition at line 623 of file TargetPassConfig.cpp.

◆ getTargetTransformInfo()

|

overridevirtual |

Get a TargetTransformInfo implementation for the target.

The TTI returned uses the common code generator to answer queries about the IR.

Reimplemented from llvm::TargetMachine.

Reimplemented in llvm::AArch64TargetMachine, llvm::GCNTargetMachine, llvm::R600TargetMachine, llvm::ARCTargetMachine, llvm::ARMBaseTargetMachine, llvm::BPFTargetMachine, llvm::DirectXTargetMachine, llvm::HexagonTargetMachine, llvm::LanaiTargetMachine, llvm::LoongArchTargetMachine, llvm::MipsTargetMachine, llvm::NVPTXTargetMachine, llvm::PPCTargetMachine, llvm::RISCVTargetMachine, llvm::SPIRVTargetMachine, llvm::SystemZTargetMachine, llvm::VETargetMachine, llvm::WebAssemblyTargetMachine, llvm::X86TargetMachine, and llvm::XCoreTargetMachine.

Definition at line 106 of file LLVMTargetMachine.cpp.

References F.

◆ initAsmInfo()

|

protected |

Definition at line 45 of file LLVMTargetMachine.cpp.

References llvm::TargetMachine::AsmInfo, assert(), llvm::TargetOptions::BinutilsVersion, llvm::Target::createMCAsmInfo(), llvm::Target::createMCInstrInfo(), llvm::Target::createMCRegInfo(), llvm::Target::createMCSubtargetInfo(), llvm::TargetOptions::DisableIntegratedAS, llvm::TargetOptions::ExceptionModel, llvm::TargetMachine::getTargetCPU(), llvm::TargetMachine::getTargetFeatureString(), llvm::TargetMachine::getTargetTriple(), llvm::TargetOptions::MCOptions, llvm::TargetMachine::MII, llvm::TargetMachine::MRI, llvm::None, llvm::TargetMachine::Options, llvm::MCTargetOptions::PPCUseFullRegisterNames, llvm::MCTargetOptions::PreserveAsmComments, llvm::MCAsmInfo::setBinutilsVersion(), llvm::MCAsmInfo::setExceptionsType(), llvm::MCAsmInfo::setFullRegisterNames(), llvm::MCAsmInfo::setParseInlineAsmUsingAsmParser(), llvm::MCAsmInfo::setPreserveAsmComments(), llvm::MCAsmInfo::setUseIntegratedAssembler(), llvm::TargetMachine::STI, and llvm::TargetMachine::TheTarget.

Referenced by llvm::AArch64TargetMachine::AArch64TargetMachine(), llvm::AMDGPUTargetMachine::AMDGPUTargetMachine(), llvm::ARCTargetMachine::ARCTargetMachine(), llvm::ARMBaseTargetMachine::ARMBaseTargetMachine(), llvm::AVRTargetMachine::AVRTargetMachine(), llvm::BPFTargetMachine::BPFTargetMachine(), llvm::CSKYTargetMachine::CSKYTargetMachine(), llvm::DirectXTargetMachine::DirectXTargetMachine(), llvm::HexagonTargetMachine::HexagonTargetMachine(), llvm::LanaiTargetMachine::LanaiTargetMachine(), llvm::LoongArchTargetMachine::LoongArchTargetMachine(), llvm::M68kTargetMachine::M68kTargetMachine(), llvm::MipsTargetMachine::MipsTargetMachine(), llvm::MSP430TargetMachine::MSP430TargetMachine(), llvm::NVPTXTargetMachine::NVPTXTargetMachine(), llvm::PPCTargetMachine::PPCTargetMachine(), llvm::RISCVTargetMachine::RISCVTargetMachine(), llvm::SparcTargetMachine::SparcTargetMachine(), llvm::SPIRVTargetMachine::SPIRVTargetMachine(), llvm::SystemZTargetMachine::SystemZTargetMachine(), llvm::VETargetMachine::VETargetMachine(), llvm::WebAssemblyTargetMachine::WebAssemblyTargetMachine(), llvm::X86TargetMachine::X86TargetMachine(), llvm::XCoreTargetMachine::XCoreTargetMachine(), and llvm::XtensaTargetMachine::XtensaTargetMachine().

◆ isMachineVerifierClean()

|

inlinevirtual |

Returns true if the target is expected to pass all machine verifier checks.

This is a stopgap measure to fix targets one by one. We will remove this at some point and always enable the verifier when EXPENSIVE_CHECKS is enabled.

Reimplemented in llvm::R600TargetMachine, llvm::LanaiTargetMachine, llvm::NVPTXTargetMachine, and llvm::VETargetMachine.

Definition at line 492 of file TargetMachine.h.

Referenced by llvm::TargetPassConfig::addVerifyPass().

◆ registerMachineRegisterInfoCallback()

|

inlinevirtual |

Reimplemented in llvm::GCNTargetMachine.

Definition at line 523 of file TargetMachine.h.

Referenced by llvm::MachineModuleInfo::getOrCreateMachineFunction(), and llvm::MachineFunctionAnalysis::run().

◆ unqualifiedInlineAsmVariant()

|

inlinevirtual |

The default variant to use in unqualified asm instructions.

If this returns 0, asm "$(foo$|bar$)" will evaluate to asm "foo".

Reimplemented in llvm::PPCTargetMachine.

Definition at line 520 of file TargetMachine.h.

Referenced by EmitInlineAsmStr().

◆ useIPRA()

|

inlinevirtual |

True if the target wants to use interprocedural register allocation by default.

The -enable-ipra flag can be used to override this.

Reimplemented in llvm::GCNTargetMachine.

Definition at line 514 of file TargetMachine.h.

Referenced by llvm::TargetPassConfig::TargetPassConfig().

◆ usesPhysRegsForValues()

|

inlinevirtual |

True if the target uses physical regs (as nearly all targets do).

False for stack machines such as WebAssembly and other virtual-register machines. If true, all vregs must be allocated before PEI. If false, then callee-save register spilling and scavenging are not needed or used. If false, implicitly defined registers will still be assumed to be physical registers, except that variadic defs will be allocated vregs.

Reimplemented in llvm::SPIRVTargetMachine, and llvm::WebAssemblyTargetMachine.

Definition at line 510 of file TargetMachine.h.

The documentation for this class was generated from the following files:

- include/llvm/Target/TargetMachine.h

- lib/CodeGen/LLVMTargetMachine.cpp

- lib/CodeGen/TargetPassConfig.cpp