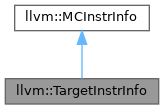

TargetInstrInfo - Interface to description of machine instruction set. More...

#include "llvm/CodeGen/TargetInstrInfo.h"

Classes | |

| struct | MachineBranchPredicate |

| Represents a predicate at the MachineFunction level. More... | |

| class | PipelinerLoopInfo |

| Object returned by analyzeLoopForPipelining. More... | |

| struct | RegSubRegPair |

| A pair composed of a register and a sub-register index. More... | |

| struct | RegSubRegPairAndIdx |

| A pair composed of a pair of a register and a sub-register index, and another sub-register index. More... | |

Public Member Functions | |

| TargetInstrInfo (unsigned CFSetupOpcode=~0u, unsigned CFDestroyOpcode=~0u, unsigned CatchRetOpcode=~0u, unsigned ReturnOpcode=~0u) | |

| TargetInstrInfo (const TargetInstrInfo &)=delete | |

| TargetInstrInfo & | operator= (const TargetInstrInfo &)=delete |

| virtual | ~TargetInstrInfo () |

| virtual const TargetRegisterClass * | getRegClass (const MCInstrDesc &MCID, unsigned OpNum, const TargetRegisterInfo *TRI, const MachineFunction &MF) const |

| Given a machine instruction descriptor, returns the register class constraint for OpNum, or NULL. | |

| bool | isTriviallyReMaterializable (const MachineInstr &MI) const |

| Return true if the instruction is trivially rematerializable, meaning it has no side effects and requires no operands that aren't always available. | |

| virtual bool | isIgnorableUse (const MachineOperand &MO) const |

Given MO is a PhysReg use return if it can be ignored for the purpose of instruction rematerialization or sinking. | |

| virtual bool | isSafeToSink (MachineInstr &MI, MachineBasicBlock *SuccToSinkTo, MachineCycleInfo *CI) const |

| unsigned | getCallFrameSetupOpcode () const |

| These methods return the opcode of the frame setup/destroy instructions if they exist (-1 otherwise). | |

| unsigned | getCallFrameDestroyOpcode () const |

| bool | isFrameInstr (const MachineInstr &I) const |

| Returns true if the argument is a frame pseudo instruction. | |

| bool | isFrameSetup (const MachineInstr &I) const |

| Returns true if the argument is a frame setup pseudo instruction. | |

| int64_t | getFrameSize (const MachineInstr &I) const |

| Returns size of the frame associated with the given frame instruction. | |

| int64_t | getFrameTotalSize (const MachineInstr &I) const |

| Returns the total frame size, which is made up of the space set up inside the pair of frame start-stop instructions and the space that is set up prior to the pair. | |

| unsigned | getCatchReturnOpcode () const |

| unsigned | getReturnOpcode () const |

| virtual int | getSPAdjust (const MachineInstr &MI) const |

| Returns the actual stack pointer adjustment made by an instruction as part of a call sequence. | |

| virtual bool | isCoalescableExtInstr (const MachineInstr &MI, Register &SrcReg, Register &DstReg, unsigned &SubIdx) const |

| Return true if the instruction is a "coalescable" extension instruction. | |

| virtual Register | isLoadFromStackSlot (const MachineInstr &MI, int &FrameIndex) const |

| If the specified machine instruction is a direct load from a stack slot, return the virtual or physical register number of the destination along with the FrameIndex of the loaded stack slot. | |

| virtual Register | isLoadFromStackSlot (const MachineInstr &MI, int &FrameIndex, unsigned &MemBytes) const |

| Optional extension of isLoadFromStackSlot that returns the number of bytes loaded from the stack. | |

| virtual Register | isLoadFromStackSlotPostFE (const MachineInstr &MI, int &FrameIndex) const |

| Check for post-frame ptr elimination stack locations as well. | |

| virtual bool | hasLoadFromStackSlot (const MachineInstr &MI, SmallVectorImpl< const MachineMemOperand * > &Accesses) const |

| If the specified machine instruction has a load from a stack slot, return true along with the FrameIndices of the loaded stack slot and the machine mem operands containing the reference. | |

| virtual Register | isStoreToStackSlot (const MachineInstr &MI, int &FrameIndex) const |

| If the specified machine instruction is a direct store to a stack slot, return the virtual or physical register number of the source reg along with the FrameIndex of the loaded stack slot. | |

| virtual Register | isStoreToStackSlot (const MachineInstr &MI, int &FrameIndex, unsigned &MemBytes) const |

| Optional extension of isStoreToStackSlot that returns the number of bytes stored to the stack. | |

| virtual Register | isStoreToStackSlotPostFE (const MachineInstr &MI, int &FrameIndex) const |

| Check for post-frame ptr elimination stack locations as well. | |

| virtual bool | hasStoreToStackSlot (const MachineInstr &MI, SmallVectorImpl< const MachineMemOperand * > &Accesses) const |

| If the specified machine instruction has a store to a stack slot, return true along with the FrameIndices of the loaded stack slot and the machine mem operands containing the reference. | |

| virtual bool | isStackSlotCopy (const MachineInstr &MI, int &DestFrameIndex, int &SrcFrameIndex) const |

| Return true if the specified machine instruction is a copy of one stack slot to another and has no other effect. | |

| virtual bool | getStackSlotRange (const TargetRegisterClass *RC, unsigned SubIdx, unsigned &Size, unsigned &Offset, const MachineFunction &MF) const |

| Compute the size in bytes and offset within a stack slot of a spilled register or subregister. | |

| bool | isUnspillableTerminator (const MachineInstr *MI) const |

| Return true if the given instruction is terminator that is unspillable, according to isUnspillableTerminatorImpl. | |

| virtual unsigned | getInstSizeInBytes (const MachineInstr &MI) const |

| Returns the size in bytes of the specified MachineInstr, or ~0U when this function is not implemented by a target. | |

| virtual bool | isAsCheapAsAMove (const MachineInstr &MI) const |

| Return true if the instruction is as cheap as a move instruction. | |

| virtual bool | shouldSink (const MachineInstr &MI) const |

| Return true if the instruction should be sunk by MachineSink. | |

| virtual bool | shouldHoist (const MachineInstr &MI, const MachineLoop *FromLoop) const |

| Return false if the instruction should not be hoisted by MachineLICM. | |

| virtual void | reMaterialize (MachineBasicBlock &MBB, MachineBasicBlock::iterator MI, Register DestReg, unsigned SubIdx, const MachineInstr &Orig, const TargetRegisterInfo &TRI) const |

| Re-issue the specified 'original' instruction at the specific location targeting a new destination register. | |

| virtual MachineInstr & | duplicate (MachineBasicBlock &MBB, MachineBasicBlock::iterator InsertBefore, const MachineInstr &Orig) const |

Clones instruction or the whole instruction bundle Orig and insert into MBB before InsertBefore. | |

| virtual MachineInstr * | convertToThreeAddress (MachineInstr &MI, LiveVariables *LV, LiveIntervals *LIS) const |

| This method must be implemented by targets that set the M_CONVERTIBLE_TO_3_ADDR flag. | |

| MachineInstr * | commuteInstruction (MachineInstr &MI, bool NewMI=false, unsigned OpIdx1=CommuteAnyOperandIndex, unsigned OpIdx2=CommuteAnyOperandIndex) const |

| This method commutes the operands of the given machine instruction MI. | |

| virtual bool | findCommutedOpIndices (const MachineInstr &MI, unsigned &SrcOpIdx1, unsigned &SrcOpIdx2) const |

| Returns true iff the routine could find two commutable operands in the given machine instruction. | |

| virtual bool | hasCommutePreference (MachineInstr &MI, bool &Commute) const |

| Returns true if the target has a preference on the operands order of the given machine instruction. | |

| bool | getRegSequenceInputs (const MachineInstr &MI, unsigned DefIdx, SmallVectorImpl< RegSubRegPairAndIdx > &InputRegs) const |

Build the equivalent inputs of a REG_SEQUENCE for the given MI and DefIdx. | |

| bool | getExtractSubregInputs (const MachineInstr &MI, unsigned DefIdx, RegSubRegPairAndIdx &InputReg) const |

Build the equivalent inputs of a EXTRACT_SUBREG for the given MI and DefIdx. | |

| bool | getInsertSubregInputs (const MachineInstr &MI, unsigned DefIdx, RegSubRegPair &BaseReg, RegSubRegPairAndIdx &InsertedReg) const |

Build the equivalent inputs of a INSERT_SUBREG for the given MI and DefIdx. | |

| virtual bool | produceSameValue (const MachineInstr &MI0, const MachineInstr &MI1, const MachineRegisterInfo *MRI=nullptr) const |

| Return true if two machine instructions would produce identical values. | |

| virtual bool | isBranchOffsetInRange (unsigned BranchOpc, int64_t BrOffset) const |

| virtual MachineBasicBlock * | getBranchDestBlock (const MachineInstr &MI) const |

| virtual void | insertIndirectBranch (MachineBasicBlock &MBB, MachineBasicBlock &NewDestBB, MachineBasicBlock &RestoreBB, const DebugLoc &DL, int64_t BrOffset=0, RegScavenger *RS=nullptr) const |

Insert an unconditional indirect branch at the end of MBB to NewDestBB. | |

| virtual bool | analyzeBranch (MachineBasicBlock &MBB, MachineBasicBlock *&TBB, MachineBasicBlock *&FBB, SmallVectorImpl< MachineOperand > &Cond, bool AllowModify=false) const |

| Analyze the branching code at the end of MBB, returning true if it cannot be understood (e.g. | |

| virtual bool | analyzeBranchPredicate (MachineBasicBlock &MBB, MachineBranchPredicate &MBP, bool AllowModify=false) const |

| Analyze the branching code at the end of MBB and parse it into the MachineBranchPredicate structure if possible. | |

| virtual unsigned | removeBranch (MachineBasicBlock &MBB, int *BytesRemoved=nullptr) const |

| Remove the branching code at the end of the specific MBB. | |

| virtual unsigned | insertBranch (MachineBasicBlock &MBB, MachineBasicBlock *TBB, MachineBasicBlock *FBB, ArrayRef< MachineOperand > Cond, const DebugLoc &DL, int *BytesAdded=nullptr) const |

| Insert branch code into the end of the specified MachineBasicBlock. | |

| unsigned | insertUnconditionalBranch (MachineBasicBlock &MBB, MachineBasicBlock *DestBB, const DebugLoc &DL, int *BytesAdded=nullptr) const |

| virtual std::unique_ptr< PipelinerLoopInfo > | analyzeLoopForPipelining (MachineBasicBlock *LoopBB) const |

| Analyze loop L, which must be a single-basic-block loop, and if the conditions can be understood enough produce a PipelinerLoopInfo object. | |

| virtual bool | analyzeLoop (MachineLoop &L, MachineInstr *&IndVarInst, MachineInstr *&CmpInst) const |

| Analyze the loop code, return true if it cannot be understood. | |

| virtual unsigned | reduceLoopCount (MachineBasicBlock &MBB, MachineBasicBlock &PreHeader, MachineInstr *IndVar, MachineInstr &Cmp, SmallVectorImpl< MachineOperand > &Cond, SmallVectorImpl< MachineInstr * > &PrevInsts, unsigned Iter, unsigned MaxIter) const |

| Generate code to reduce the loop iteration by one and check if the loop is finished. | |

| virtual void | ReplaceTailWithBranchTo (MachineBasicBlock::iterator Tail, MachineBasicBlock *NewDest) const |

| Delete the instruction OldInst and everything after it, replacing it with an unconditional branch to NewDest. | |

| virtual bool | isLegalToSplitMBBAt (MachineBasicBlock &MBB, MachineBasicBlock::iterator MBBI) const |

| Return true if it's legal to split the given basic block at the specified instruction (i.e. | |

| virtual bool | isProfitableToIfCvt (MachineBasicBlock &MBB, unsigned NumCycles, unsigned ExtraPredCycles, BranchProbability Probability) const |

| Return true if it's profitable to predicate instructions with accumulated instruction latency of "NumCycles" of the specified basic block, where the probability of the instructions being executed is given by Probability, and Confidence is a measure of our confidence that it will be properly predicted. | |

| virtual bool | isProfitableToIfCvt (MachineBasicBlock &TMBB, unsigned NumTCycles, unsigned ExtraTCycles, MachineBasicBlock &FMBB, unsigned NumFCycles, unsigned ExtraFCycles, BranchProbability Probability) const |

| Second variant of isProfitableToIfCvt. | |

| virtual bool | isProfitableToDupForIfCvt (MachineBasicBlock &MBB, unsigned NumCycles, BranchProbability Probability) const |

| Return true if it's profitable for if-converter to duplicate instructions of specified accumulated instruction latencies in the specified MBB to enable if-conversion. | |

| virtual unsigned | extraSizeToPredicateInstructions (const MachineFunction &MF, unsigned NumInsts) const |

| Return the increase in code size needed to predicate a contiguous run of NumInsts instructions. | |

| virtual unsigned | predictBranchSizeForIfCvt (MachineInstr &MI) const |

| Return an estimate for the code size reduction (in bytes) which will be caused by removing the given branch instruction during if-conversion. | |

| virtual bool | isProfitableToUnpredicate (MachineBasicBlock &TMBB, MachineBasicBlock &FMBB) const |

| Return true if it's profitable to unpredicate one side of a 'diamond', i.e. | |

| virtual bool | canInsertSelect (const MachineBasicBlock &MBB, ArrayRef< MachineOperand > Cond, Register DstReg, Register TrueReg, Register FalseReg, int &CondCycles, int &TrueCycles, int &FalseCycles) const |

| Return true if it is possible to insert a select instruction that chooses between TrueReg and FalseReg based on the condition code in Cond. | |

| virtual void | insertSelect (MachineBasicBlock &MBB, MachineBasicBlock::iterator I, const DebugLoc &DL, Register DstReg, ArrayRef< MachineOperand > Cond, Register TrueReg, Register FalseReg) const |

| Insert a select instruction into MBB before I that will copy TrueReg to DstReg when Cond is true, and FalseReg to DstReg when Cond is false. | |

| virtual bool | analyzeSelect (const MachineInstr &MI, SmallVectorImpl< MachineOperand > &Cond, unsigned &TrueOp, unsigned &FalseOp, bool &Optimizable) const |

| Analyze the given select instruction, returning true if it cannot be understood. | |

| virtual MachineInstr * | optimizeSelect (MachineInstr &MI, SmallPtrSetImpl< MachineInstr * > &NewMIs, bool PreferFalse=false) const |

| Given a select instruction that was understood by analyzeSelect and returned Optimizable = true, attempt to optimize MI by merging it with one of its operands. | |

| virtual void | copyPhysReg (MachineBasicBlock &MBB, MachineBasicBlock::iterator MI, const DebugLoc &DL, MCRegister DestReg, MCRegister SrcReg, bool KillSrc) const |

| Emit instructions to copy a pair of physical registers. | |

| virtual bool | isPCRelRegisterOperandLegal (const MachineOperand &MO) const |

| Allow targets to tell MachineVerifier whether a specific register MachineOperand can be used as part of PC-relative addressing. | |

| virtual int | getJumpTableIndex (const MachineInstr &MI) const |

Return an index for MachineJumpTableInfo if insn is an indirect jump using a jump table, otherwise -1. | |

| std::optional< DestSourcePair > | isCopyInstr (const MachineInstr &MI) const |

| If the specific machine instruction is a instruction that moves/copies value from one register to another register return destination and source registers as machine operands. | |

| std::optional< DestSourcePair > | isCopyLikeInstr (const MachineInstr &MI) const |

| bool | isFullCopyInstr (const MachineInstr &MI) const |

| virtual std::optional< RegImmPair > | isAddImmediate (const MachineInstr &MI, Register Reg) const |

If the specific machine instruction is an instruction that adds an immediate value and a register, and stores the result in the given register Reg, return a pair of the source register and the offset which has been added. | |

| virtual bool | getConstValDefinedInReg (const MachineInstr &MI, const Register Reg, int64_t &ImmVal) const |

| Returns true if MI is an instruction that defines Reg to have a constant value and the value is recorded in ImmVal. | |

| virtual void | storeRegToStackSlot (MachineBasicBlock &MBB, MachineBasicBlock::iterator MI, Register SrcReg, bool isKill, int FrameIndex, const TargetRegisterClass *RC, const TargetRegisterInfo *TRI, Register VReg) const |

| Store the specified register of the given register class to the specified stack frame index. | |

| virtual void | loadRegFromStackSlot (MachineBasicBlock &MBB, MachineBasicBlock::iterator MI, Register DestReg, int FrameIndex, const TargetRegisterClass *RC, const TargetRegisterInfo *TRI, Register VReg) const |

| Load the specified register of the given register class from the specified stack frame index. | |

| virtual bool | expandPostRAPseudo (MachineInstr &MI) const |

| This function is called for all pseudo instructions that remain after register allocation. | |

| virtual bool | isSubregFoldable () const |

| Check whether the target can fold a load that feeds a subreg operand (or a subreg operand that feeds a store). | |

| virtual std::pair< unsigned, unsigned > | getPatchpointUnfoldableRange (const MachineInstr &MI) const |

| For a patchpoint, stackmap, or statepoint intrinsic, return the range of operands which can't be folded into stack references. | |

| MachineInstr * | foldMemoryOperand (MachineInstr &MI, ArrayRef< unsigned > Ops, int FI, LiveIntervals *LIS=nullptr, VirtRegMap *VRM=nullptr) const |

| Attempt to fold a load or store of the specified stack slot into the specified machine instruction for the specified operand(s). | |

| MachineInstr * | foldMemoryOperand (MachineInstr &MI, ArrayRef< unsigned > Ops, MachineInstr &LoadMI, LiveIntervals *LIS=nullptr) const |

| Same as the previous version except it allows folding of any load and store from / to any address, not just from a specific stack slot. | |

| void | lowerCopy (MachineInstr *MI, const TargetRegisterInfo *TRI) const |

| This function defines the logic to lower COPY instruction to target specific instruction(s). | |

| virtual bool | getMachineCombinerPatterns (MachineInstr &Root, SmallVectorImpl< unsigned > &Patterns, bool DoRegPressureReduce) const |

Return true when there is potentially a faster code sequence for an instruction chain ending in Root. | |

| virtual bool | shouldReduceRegisterPressure (const MachineBasicBlock *MBB, const RegisterClassInfo *RegClassInfo) const |

| Return true if target supports reassociation of instructions in machine combiner pass to reduce register pressure for a given BB. | |

| virtual void | finalizeInsInstrs (MachineInstr &Root, unsigned &Pattern, SmallVectorImpl< MachineInstr * > &InsInstrs) const |

| Fix up the placeholder we may add in genAlternativeCodeSequence(). | |

| virtual bool | isThroughputPattern (unsigned Pattern) const |

| Return true when a code sequence can improve throughput. | |

| virtual CombinerObjective | getCombinerObjective (unsigned Pattern) const |

| Return the objective of a combiner pattern. | |

| bool | isReassociationCandidate (const MachineInstr &Inst, bool &Commuted) const |

| Return true if the input \P Inst is part of a chain of dependent ops that are suitable for reassociation, otherwise return false. | |

| virtual bool | isAssociativeAndCommutative (const MachineInstr &Inst, bool Invert=false) const |

| Return true when \P Inst is both associative and commutative. | |

| virtual std::optional< unsigned > | getInverseOpcode (unsigned Opcode) const |

| Return the inverse operation opcode if it exists for \P Opcode (e.g. | |

| bool | areOpcodesEqualOrInverse (unsigned Opcode1, unsigned Opcode2) const |

| Return true when \P Opcode1 or its inversion is equal to \P Opcode2. | |

| virtual bool | hasReassociableOperands (const MachineInstr &Inst, const MachineBasicBlock *MBB) const |

| Return true when \P Inst has reassociable operands in the same \P MBB. | |

| virtual bool | hasReassociableSibling (const MachineInstr &Inst, bool &Commuted) const |

| Return true when \P Inst has reassociable sibling. | |

| virtual void | genAlternativeCodeSequence (MachineInstr &Root, unsigned Pattern, SmallVectorImpl< MachineInstr * > &InsInstrs, SmallVectorImpl< MachineInstr * > &DelInstrs, DenseMap< unsigned, unsigned > &InstIdxForVirtReg) const |

| When getMachineCombinerPatterns() finds patterns, this function generates the instructions that could replace the original code sequence. | |

| virtual bool | accumulateInstrSeqToRootLatency (MachineInstr &Root) const |

| When calculate the latency of the root instruction, accumulate the latency of the sequence to the root latency. | |

| virtual void | getReassociateOperandIndices (const MachineInstr &Root, unsigned Pattern, std::array< unsigned, 5 > &OperandIndices) const |

| The returned array encodes the operand index for each parameter because the operands may be commuted; the operand indices for associative operations might also be target-specific. | |

| void | reassociateOps (MachineInstr &Root, MachineInstr &Prev, unsigned Pattern, SmallVectorImpl< MachineInstr * > &InsInstrs, SmallVectorImpl< MachineInstr * > &DelInstrs, ArrayRef< unsigned > OperandIndices, DenseMap< unsigned, unsigned > &InstrIdxForVirtReg) const |

| Attempt to reassociate \P Root and \P Prev according to \P Pattern to reduce critical path length. | |

| std::pair< unsigned, unsigned > | getReassociationOpcodes (unsigned Pattern, const MachineInstr &Root, const MachineInstr &Prev) const |

| Reassociation of some instructions requires inverse operations (e.g. | |

| virtual int | getExtendResourceLenLimit () const |

| The limit on resource length extension we accept in MachineCombiner Pass. | |

| virtual void | setSpecialOperandAttr (MachineInstr &OldMI1, MachineInstr &OldMI2, MachineInstr &NewMI1, MachineInstr &NewMI2) const |

| This is an architecture-specific helper function of reassociateOps. | |

| virtual bool | useMachineCombiner () const |

| Return true when a target supports MachineCombiner. | |

| virtual MachineTraceStrategy | getMachineCombinerTraceStrategy () const |

| Return a strategy that MachineCombiner must use when creating traces. | |

| virtual bool | canCopyGluedNodeDuringSchedule (SDNode *N) const |

| Return true if the given SDNode can be copied during scheduling even if it has glue. | |

| virtual bool | unfoldMemoryOperand (MachineFunction &MF, MachineInstr &MI, unsigned Reg, bool UnfoldLoad, bool UnfoldStore, SmallVectorImpl< MachineInstr * > &NewMIs) const |

| unfoldMemoryOperand - Separate a single instruction which folded a load or a store or a load and a store into two or more instruction. | |

| virtual bool | unfoldMemoryOperand (SelectionDAG &DAG, SDNode *N, SmallVectorImpl< SDNode * > &NewNodes) const |

| virtual unsigned | getOpcodeAfterMemoryUnfold (unsigned Opc, bool UnfoldLoad, bool UnfoldStore, unsigned *LoadRegIndex=nullptr) const |

| Returns the opcode of the would be new instruction after load / store are unfolded from an instruction of the specified opcode. | |

| virtual bool | areLoadsFromSameBasePtr (SDNode *Load1, SDNode *Load2, int64_t &Offset1, int64_t &Offset2) const |

| This is used by the pre-regalloc scheduler to determine if two loads are loading from the same base address. | |

| virtual bool | shouldScheduleLoadsNear (SDNode *Load1, SDNode *Load2, int64_t Offset1, int64_t Offset2, unsigned NumLoads) const |

| This is a used by the pre-regalloc scheduler to determine (in conjunction with areLoadsFromSameBasePtr) if two loads should be scheduled together. | |

| bool | getMemOperandWithOffset (const MachineInstr &MI, const MachineOperand *&BaseOp, int64_t &Offset, bool &OffsetIsScalable, const TargetRegisterInfo *TRI) const |

| Get the base operand and byte offset of an instruction that reads/writes memory. | |

| virtual bool | getMemOperandsWithOffsetWidth (const MachineInstr &MI, SmallVectorImpl< const MachineOperand * > &BaseOps, int64_t &Offset, bool &OffsetIsScalable, LocationSize &Width, const TargetRegisterInfo *TRI) const |

| Get zero or more base operands and the byte offset of an instruction that reads/writes memory. | |

| virtual bool | getBaseAndOffsetPosition (const MachineInstr &MI, unsigned &BasePos, unsigned &OffsetPos) const |

| Return true if the instruction contains a base register and offset. | |

| virtual std::optional< ExtAddrMode > | getAddrModeFromMemoryOp (const MachineInstr &MemI, const TargetRegisterInfo *TRI) const |

| Target dependent implementation to get the values constituting the address MachineInstr that is accessing memory. | |

| virtual bool | canFoldIntoAddrMode (const MachineInstr &MemI, Register Reg, const MachineInstr &AddrI, ExtAddrMode &AM) const |

Check if it's possible and beneficial to fold the addressing computation AddrI into the addressing mode of the load/store instruction MemI. | |

| virtual MachineInstr * | emitLdStWithAddr (MachineInstr &MemI, const ExtAddrMode &AM) const |

Emit a load/store instruction with the same value register as MemI, but using the address from AM. | |

| virtual bool | preservesZeroValueInReg (const MachineInstr *MI, const Register NullValueReg, const TargetRegisterInfo *TRI) const |

| Returns true if MI's Def is NullValueReg, and the MI does not change the Zero value. | |

| virtual bool | getIncrementValue (const MachineInstr &MI, int &Value) const |

| If the instruction is an increment of a constant value, return the amount. | |

| virtual bool | shouldClusterMemOps (ArrayRef< const MachineOperand * > BaseOps1, int64_t Offset1, bool OffsetIsScalable1, ArrayRef< const MachineOperand * > BaseOps2, int64_t Offset2, bool OffsetIsScalable2, unsigned ClusterSize, unsigned NumBytes) const |

| Returns true if the two given memory operations should be scheduled adjacent. | |

| virtual bool | reverseBranchCondition (SmallVectorImpl< MachineOperand > &Cond) const |

| Reverses the branch condition of the specified condition list, returning false on success and true if it cannot be reversed. | |

| virtual void | insertNoop (MachineBasicBlock &MBB, MachineBasicBlock::iterator MI) const |

| Insert a noop into the instruction stream at the specified point. | |

| virtual void | insertNoops (MachineBasicBlock &MBB, MachineBasicBlock::iterator MI, unsigned Quantity) const |

| Insert noops into the instruction stream at the specified point. | |

| virtual MCInst | getNop () const |

| Return the noop instruction to use for a noop. | |

| virtual bool | isPostIncrement (const MachineInstr &MI) const |

| Return true for post-incremented instructions. | |

| virtual bool | isPredicated (const MachineInstr &MI) const |

| Returns true if the instruction is already predicated. | |

| virtual bool | canPredicatePredicatedInstr (const MachineInstr &MI) const |

| Assumes the instruction is already predicated and returns true if the instruction can be predicated again. | |

| virtual std::string | createMIROperandComment (const MachineInstr &MI, const MachineOperand &Op, unsigned OpIdx, const TargetRegisterInfo *TRI) const |

| bool | isUnpredicatedTerminator (const MachineInstr &MI) const |

| Returns true if the instruction is a terminator instruction that has not been predicated. | |

| virtual bool | isUnconditionalTailCall (const MachineInstr &MI) const |

| Returns true if MI is an unconditional tail call. | |

| virtual bool | canMakeTailCallConditional (SmallVectorImpl< MachineOperand > &Cond, const MachineInstr &TailCall) const |

| Returns true if the tail call can be made conditional on BranchCond. | |

| virtual void | replaceBranchWithTailCall (MachineBasicBlock &MBB, SmallVectorImpl< MachineOperand > &Cond, const MachineInstr &TailCall) const |

| Replace the conditional branch in MBB with a conditional tail call. | |

| virtual bool | PredicateInstruction (MachineInstr &MI, ArrayRef< MachineOperand > Pred) const |

| Convert the instruction into a predicated instruction. | |

| virtual bool | SubsumesPredicate (ArrayRef< MachineOperand > Pred1, ArrayRef< MachineOperand > Pred2) const |

| Returns true if the first specified predicate subsumes the second, e.g. | |

| virtual bool | ClobbersPredicate (MachineInstr &MI, std::vector< MachineOperand > &Pred, bool SkipDead) const |

| If the specified instruction defines any predicate or condition code register(s) used for predication, returns true as well as the definition predicate(s) by reference. | |

| virtual bool | isPredicable (const MachineInstr &MI) const |

| Return true if the specified instruction can be predicated. | |

| virtual bool | isSafeToMoveRegClassDefs (const TargetRegisterClass *RC) const |

| Return true if it's safe to move a machine instruction that defines the specified register class. | |

| virtual bool | isSchedulingBoundary (const MachineInstr &MI, const MachineBasicBlock *MBB, const MachineFunction &MF) const |

| Test if the given instruction should be considered a scheduling boundary. | |

| virtual unsigned | getInlineAsmLength (const char *Str, const MCAsmInfo &MAI, const TargetSubtargetInfo *STI=nullptr) const |

| Measure the specified inline asm to determine an approximation of its length. | |

| virtual ScheduleHazardRecognizer * | CreateTargetHazardRecognizer (const TargetSubtargetInfo *STI, const ScheduleDAG *DAG) const |

| Allocate and return a hazard recognizer to use for this target when scheduling the machine instructions before register allocation. | |

| virtual ScheduleHazardRecognizer * | CreateTargetMIHazardRecognizer (const InstrItineraryData *, const ScheduleDAGMI *DAG) const |

| Allocate and return a hazard recognizer to use for this target when scheduling the machine instructions before register allocation. | |

| virtual ScheduleHazardRecognizer * | CreateTargetPostRAHazardRecognizer (const InstrItineraryData *, const ScheduleDAG *DAG) const |

| Allocate and return a hazard recognizer to use for this target when scheduling the machine instructions after register allocation. | |

| virtual ScheduleHazardRecognizer * | CreateTargetPostRAHazardRecognizer (const MachineFunction &MF) const |

| Allocate and return a hazard recognizer to use for by non-scheduling passes. | |

| bool | usePreRAHazardRecognizer () const |

| Provide a global flag for disabling the PreRA hazard recognizer that targets may choose to honor. | |

| virtual bool | analyzeCompare (const MachineInstr &MI, Register &SrcReg, Register &SrcReg2, int64_t &Mask, int64_t &Value) const |

| For a comparison instruction, return the source registers in SrcReg and SrcReg2 if having two register operands, and the value it compares against in CmpValue. | |

| virtual bool | optimizeCompareInstr (MachineInstr &CmpInstr, Register SrcReg, Register SrcReg2, int64_t Mask, int64_t Value, const MachineRegisterInfo *MRI) const |

| See if the comparison instruction can be converted into something more efficient. | |

| virtual bool | optimizeCondBranch (MachineInstr &MI) const |

| virtual MachineInstr * | optimizeLoadInstr (MachineInstr &MI, const MachineRegisterInfo *MRI, Register &FoldAsLoadDefReg, MachineInstr *&DefMI) const |

| Try to remove the load by folding it to a register operand at the use. | |

| virtual bool | foldImmediate (MachineInstr &UseMI, MachineInstr &DefMI, Register Reg, MachineRegisterInfo *MRI) const |

| 'Reg' is known to be defined by a move immediate instruction, try to fold the immediate into the use instruction. | |

| virtual unsigned | getNumMicroOps (const InstrItineraryData *ItinData, const MachineInstr &MI) const |

| Return the number of u-operations the given machine instruction will be decoded to on the target cpu. | |

| bool | isZeroCost (unsigned Opcode) const |

| Return true for pseudo instructions that don't consume any machine resources in their current form. | |

| virtual std::optional< unsigned > | getOperandLatency (const InstrItineraryData *ItinData, SDNode *DefNode, unsigned DefIdx, SDNode *UseNode, unsigned UseIdx) const |

| virtual std::optional< unsigned > | getOperandLatency (const InstrItineraryData *ItinData, const MachineInstr &DefMI, unsigned DefIdx, const MachineInstr &UseMI, unsigned UseIdx) const |

| Compute and return the use operand latency of a given pair of def and use. | |

| virtual unsigned | getInstrLatency (const InstrItineraryData *ItinData, const MachineInstr &MI, unsigned *PredCost=nullptr) const |

| Compute the instruction latency of a given instruction. | |

| virtual unsigned | getPredicationCost (const MachineInstr &MI) const |

| virtual unsigned | getInstrLatency (const InstrItineraryData *ItinData, SDNode *Node) const |

| unsigned | defaultDefLatency (const MCSchedModel &SchedModel, const MachineInstr &DefMI) const |

| Return the default expected latency for a def based on its opcode. | |

| virtual bool | isHighLatencyDef (int opc) const |

| Return true if this opcode has high latency to its result. | |

| virtual bool | hasHighOperandLatency (const TargetSchedModel &SchedModel, const MachineRegisterInfo *MRI, const MachineInstr &DefMI, unsigned DefIdx, const MachineInstr &UseMI, unsigned UseIdx) const |

| Compute operand latency between a def of 'Reg' and a use in the current loop. | |

| virtual bool | hasLowDefLatency (const TargetSchedModel &SchedModel, const MachineInstr &DefMI, unsigned DefIdx) const |

| Compute operand latency of a def of 'Reg'. | |

| virtual bool | verifyInstruction (const MachineInstr &MI, StringRef &ErrInfo) const |

| Perform target-specific instruction verification. | |

| virtual std::pair< uint16_t, uint16_t > | getExecutionDomain (const MachineInstr &MI) const |

| Return the current execution domain and bit mask of possible domains for instruction. | |

| virtual void | setExecutionDomain (MachineInstr &MI, unsigned Domain) const |

| Change the opcode of MI to execute in Domain. | |

| virtual unsigned | getPartialRegUpdateClearance (const MachineInstr &MI, unsigned OpNum, const TargetRegisterInfo *TRI) const |

| Returns the preferred minimum clearance before an instruction with an unwanted partial register update. | |

| virtual unsigned | getUndefRegClearance (const MachineInstr &MI, unsigned OpNum, const TargetRegisterInfo *TRI) const |

| Return the minimum clearance before an instruction that reads an unused register. | |

| virtual void | breakPartialRegDependency (MachineInstr &MI, unsigned OpNum, const TargetRegisterInfo *TRI) const |

| Insert a dependency-breaking instruction before MI to eliminate an unwanted dependency on OpNum. | |

| virtual DFAPacketizer * | CreateTargetScheduleState (const TargetSubtargetInfo &) const |

| Create machine specific model for scheduling. | |

| virtual bool | areMemAccessesTriviallyDisjoint (const MachineInstr &MIa, const MachineInstr &MIb) const |

| Sometimes, it is possible for the target to tell, even without aliasing information, that two MIs access different memory addresses. | |

| virtual unsigned | getMachineCSELookAheadLimit () const |

| Return the value to use for the MachineCSE's LookAheadLimit, which is a heuristic used for CSE'ing phys reg defs. | |

| virtual unsigned | getMemOperandAACheckLimit () const |

| Return the maximal number of alias checks on memory operands. | |

| virtual ArrayRef< std::pair< int, const char * > > | getSerializableTargetIndices () const |

| Return an array that contains the ids of the target indices (used for the TargetIndex machine operand) and their names. | |

| virtual std::pair< unsigned, unsigned > | decomposeMachineOperandsTargetFlags (unsigned) const |

| Decompose the machine operand's target flags into two values - the direct target flag value and any of bit flags that are applied. | |

| virtual ArrayRef< std::pair< unsigned, const char * > > | getSerializableDirectMachineOperandTargetFlags () const |

| Return an array that contains the direct target flag values and their names. | |

| virtual ArrayRef< std::pair< unsigned, const char * > > | getSerializableBitmaskMachineOperandTargetFlags () const |

| Return an array that contains the bitmask target flag values and their names. | |

| virtual ArrayRef< std::pair< MachineMemOperand::Flags, const char * > > | getSerializableMachineMemOperandTargetFlags () const |

| Return an array that contains the MMO target flag values and their names. | |

| virtual bool | isTailCall (const MachineInstr &Inst) const |

Determines whether Inst is a tail call instruction. | |

| virtual bool | isBasicBlockPrologue (const MachineInstr &MI, Register Reg=Register()) const |

| True if the instruction is bound to the top of its basic block and no other instructions shall be inserted before it. | |

| virtual unsigned | getLiveRangeSplitOpcode (Register Reg, const MachineFunction &MF) const |

| Allows targets to use appropriate copy instruction while spilitting live range of a register in register allocation. | |

| virtual MachineInstr * | createPHIDestinationCopy (MachineBasicBlock &MBB, MachineBasicBlock::iterator InsPt, const DebugLoc &DL, Register Src, Register Dst) const |

| During PHI eleimination lets target to make necessary checks and insert the copy to the PHI destination register in a target specific manner. | |

| virtual MachineInstr * | createPHISourceCopy (MachineBasicBlock &MBB, MachineBasicBlock::iterator InsPt, const DebugLoc &DL, Register Src, unsigned SrcSubReg, Register Dst) const |

| During PHI eleimination lets target to make necessary checks and insert the copy to the PHI destination register in a target specific manner. | |

| virtual std::optional< outliner::OutlinedFunction > | getOutliningCandidateInfo (std::vector< outliner::Candidate > &RepeatedSequenceLocs) const |

Returns a outliner::OutlinedFunction struct containing target-specific information for a set of outlining candidates. | |

| virtual void | mergeOutliningCandidateAttributes (Function &F, std::vector< outliner::Candidate > &Candidates) const |

| Optional target hook to create the LLVM IR attributes for the outlined function. | |

| outliner::InstrType | getOutliningType (MachineBasicBlock::iterator &MIT, unsigned Flags) const |

Returns how or if MIT should be outlined. | |

| virtual bool | isMBBSafeToOutlineFrom (MachineBasicBlock &MBB, unsigned &Flags) const |

Optional target hook that returns true if MBB is safe to outline from, and returns any target-specific information in Flags. | |

| virtual SmallVector< std::pair< MachineBasicBlock::iterator, MachineBasicBlock::iterator > > | getOutlinableRanges (MachineBasicBlock &MBB, unsigned &Flags) const |

Optional target hook which partitions MBB into outlinable ranges for instruction mapping purposes. | |

| virtual void | buildOutlinedFrame (MachineBasicBlock &MBB, MachineFunction &MF, const outliner::OutlinedFunction &OF) const |

| Insert a custom frame for outlined functions. | |

| virtual MachineBasicBlock::iterator | insertOutlinedCall (Module &M, MachineBasicBlock &MBB, MachineBasicBlock::iterator &It, MachineFunction &MF, outliner::Candidate &C) const |

| Insert a call to an outlined function into the program. | |

| virtual void | buildClearRegister (Register Reg, MachineBasicBlock &MBB, MachineBasicBlock::iterator Iter, DebugLoc &DL, bool AllowSideEffects=true) const |

| Insert an architecture-specific instruction to clear a register. | |

| virtual bool | isFunctionSafeToOutlineFrom (MachineFunction &MF, bool OutlineFromLinkOnceODRs) const |

| Return true if the function can safely be outlined from. | |

| virtual bool | shouldOutlineFromFunctionByDefault (MachineFunction &MF) const |

| Return true if the function should be outlined from by default. | |

| virtual bool | isFunctionSafeToSplit (const MachineFunction &MF) const |

| Return true if the function is a viable candidate for machine function splitting. | |

| virtual bool | isMBBSafeToSplitToCold (const MachineBasicBlock &MBB) const |

| Return true if the MachineBasicBlock can safely be split to the cold section. | |

| virtual std::optional< ParamLoadedValue > | describeLoadedValue (const MachineInstr &MI, Register Reg) const |

Produce the expression describing the MI loading a value into the physical register Reg. | |

| virtual bool | isExtendLikelyToBeFolded (MachineInstr &ExtMI, MachineRegisterInfo &MRI) const |

Given the generic extension instruction ExtMI, returns true if this extension is a likely candidate for being folded into an another instruction. | |

| virtual const MIRFormatter * | getMIRFormatter () const |

| Return MIR formatter to format/parse MIR operands. | |

| virtual unsigned | getTailDuplicateSize (CodeGenOptLevel OptLevel) const |

| Returns the target-specific default value for tail duplication. | |

| virtual const MachineOperand & | getCalleeOperand (const MachineInstr &MI) const |

Returns the callee operand from the given MI. | |

| virtual InstructionUniformity | getInstructionUniformity (const MachineInstr &MI) const |

| Return the uniformity behavior of the given instruction. | |

| virtual bool | isExplicitTargetIndexDef (const MachineInstr &MI, int &Index, int64_t &Offset) const |

Returns true if the given MI defines a TargetIndex operand that can be tracked by their offset, can have values, and can have debug info associated with it. | |

| unsigned | getCallFrameSizeAt (MachineInstr &MI) const |

| virtual void | getFrameIndexOperands (SmallVectorImpl< MachineOperand > &Ops, int FI) const |

| Fills in the necessary MachineOperands to refer to a frame index. | |

| virtual unsigned | getUndefInitOpcode (unsigned RegClassID) const |

| Gets the opcode for the Pseudo Instruction used to initialize the undef value. | |

Public Member Functions inherited from llvm::MCInstrInfo Public Member Functions inherited from llvm::MCInstrInfo | |

| void | InitMCInstrInfo (const MCInstrDesc *D, const unsigned *NI, const char *ND, const uint8_t *DF, const ComplexDeprecationPredicate *CDI, unsigned NO) |

| Initialize MCInstrInfo, called by TableGen auto-generated routines. | |

| unsigned | getNumOpcodes () const |

| const MCInstrDesc & | get (unsigned Opcode) const |

| Return the machine instruction descriptor that corresponds to the specified instruction opcode. | |

| StringRef | getName (unsigned Opcode) const |

| Returns the name for the instructions with the given opcode. | |

| bool | getDeprecatedInfo (MCInst &MI, const MCSubtargetInfo &STI, std::string &Info) const |

Returns true if a certain instruction is deprecated and if so returns the reason in Info. | |

Static Public Member Functions | |

| static bool | isGenericOpcode (unsigned Opc) |

| static bool | isGenericAtomicRMWOpcode (unsigned Opc) |

Static Public Attributes | |

| static const unsigned | CommuteAnyOperandIndex = ~0U |

Protected Member Functions | |

| virtual bool | isReallyTriviallyReMaterializable (const MachineInstr &MI) const |

| For instructions with opcodes for which the M_REMATERIALIZABLE flag is set, this hook lets the target specify whether the instruction is actually trivially rematerializable, taking into consideration its operands. | |

| virtual MachineInstr * | commuteInstructionImpl (MachineInstr &MI, bool NewMI, unsigned OpIdx1, unsigned OpIdx2) const |

| This method commutes the operands of the given machine instruction MI. | |

| virtual std::optional< DestSourcePair > | isCopyInstrImpl (const MachineInstr &MI) const |

| Target-dependent implementation for IsCopyInstr. | |

| virtual std::optional< DestSourcePair > | isCopyLikeInstrImpl (const MachineInstr &MI) const |

| virtual bool | isUnspillableTerminatorImpl (const MachineInstr *MI) const |

| Return true if the given terminator MI is not expected to spill. | |

| virtual MachineInstr * | foldMemoryOperandImpl (MachineFunction &MF, MachineInstr &MI, ArrayRef< unsigned > Ops, MachineBasicBlock::iterator InsertPt, int FrameIndex, LiveIntervals *LIS=nullptr, VirtRegMap *VRM=nullptr) const |

| Target-dependent implementation for foldMemoryOperand. | |

| virtual MachineInstr * | foldMemoryOperandImpl (MachineFunction &MF, MachineInstr &MI, ArrayRef< unsigned > Ops, MachineBasicBlock::iterator InsertPt, MachineInstr &LoadMI, LiveIntervals *LIS=nullptr) const |

| Target-dependent implementation for foldMemoryOperand. | |

| virtual bool | getRegSequenceLikeInputs (const MachineInstr &MI, unsigned DefIdx, SmallVectorImpl< RegSubRegPairAndIdx > &InputRegs) const |

| Target-dependent implementation of getRegSequenceInputs. | |

| virtual bool | getExtractSubregLikeInputs (const MachineInstr &MI, unsigned DefIdx, RegSubRegPairAndIdx &InputReg) const |

| Target-dependent implementation of getExtractSubregInputs. | |

| virtual bool | getInsertSubregLikeInputs (const MachineInstr &MI, unsigned DefIdx, RegSubRegPair &BaseReg, RegSubRegPairAndIdx &InsertedReg) const |

| Target-dependent implementation of getInsertSubregInputs. | |

| virtual outliner::InstrType | getOutliningTypeImpl (MachineBasicBlock::iterator &MIT, unsigned Flags) const |

| Target-dependent implementation for getOutliningTypeImpl. | |

Static Protected Member Functions | |

| static bool | fixCommutedOpIndices (unsigned &ResultIdx1, unsigned &ResultIdx2, unsigned CommutableOpIdx1, unsigned CommutableOpIdx2) |

| Assigns the (CommutableOpIdx1, CommutableOpIdx2) pair of commutable operand indices to (ResultIdx1, ResultIdx2). | |

Additional Inherited Members | |

Public Types inherited from llvm::MCInstrInfo Public Types inherited from llvm::MCInstrInfo | |

| using | ComplexDeprecationPredicate = bool(*)(MCInst &, const MCSubtargetInfo &, std::string &) |

Detailed Description

TargetInstrInfo - Interface to description of machine instruction set.

Definition at line 111 of file TargetInstrInfo.h.

Constructor & Destructor Documentation

◆ TargetInstrInfo() [1/2]

|

inline |

Definition at line 113 of file TargetInstrInfo.h.

◆ TargetInstrInfo() [2/2]

|

delete |

◆ ~TargetInstrInfo()

|

virtualdefault |

Member Function Documentation

◆ accumulateInstrSeqToRootLatency()

|

inlinevirtual |

When calculate the latency of the root instruction, accumulate the latency of the sequence to the root latency.

- Parameters

-

Root - Instruction that could be combined with one of its operands

Definition at line 1271 of file TargetInstrInfo.h.

◆ analyzeBranch()

|

inlinevirtual |

Analyze the branching code at the end of MBB, returning true if it cannot be understood (e.g.

it's a switch dispatch or isn't implemented for a target). Upon success, this returns false and returns with the following information in various cases:

- If this block ends with no branches (it just falls through to its succ) just return false, leaving TBB/FBB null.

- If this block ends with only an unconditional branch, it sets TBB to be the destination block.

- If this block ends with a conditional branch and it falls through to a successor block, it sets TBB to be the branch destination block and a list of operands that evaluate the condition. These operands can be passed to other TargetInstrInfo methods to create new branches.

- If this block ends with a conditional branch followed by an unconditional branch, it returns the 'true' destination in TBB, the 'false' destination in FBB, and a list of operands that evaluate the condition. These operands can be passed to other TargetInstrInfo methods to create new branches.

Note that removeBranch and insertBranch must be implemented to support cases where this method returns success.

If AllowModify is true, then this routine is allowed to modify the basic block (e.g. delete instructions after the unconditional branch).

The CFG information in MBB.Predecessors and MBB.Successors must be valid before calling this function.

Definition at line 650 of file TargetInstrInfo.h.

Referenced by llvm::TailDuplicator::canTailDuplicate(), llvm::PeelingModuloScheduleExpander::CreateLCSSAExitingBlock(), and llvm::TailDuplicator::shouldTailDuplicate().

◆ analyzeBranchPredicate()

|

inlinevirtual |

Analyze the branching code at the end of MBB and parse it into the MachineBranchPredicate structure if possible.

Returns false on success and true on failure.

If AllowModify is true, then this routine is allowed to modify the basic block (e.g. delete instructions after the unconditional branch).

Definition at line 692 of file TargetInstrInfo.h.

◆ analyzeCompare()

|

inlinevirtual |

For a comparison instruction, return the source registers in SrcReg and SrcReg2 if having two register operands, and the value it compares against in CmpValue.

Return true if the comparison instruction can be analyzed.

Definition at line 1688 of file TargetInstrInfo.h.

◆ analyzeLoop()

|

inlinevirtual |

Analyze the loop code, return true if it cannot be understood.

Upon success, this function returns false and returns information about the induction variable and compare instruction used at the end.

Definition at line 795 of file TargetInstrInfo.h.

◆ analyzeLoopForPipelining()

|

inlinevirtual |

Analyze loop L, which must be a single-basic-block loop, and if the conditions can be understood enough produce a PipelinerLoopInfo object.

Definition at line 788 of file TargetInstrInfo.h.

Referenced by llvm::PeelingModuloScheduleExpander::expand().

◆ analyzeSelect()

|

inlinevirtual |

Analyze the given select instruction, returning true if it cannot be understood.

It is assumed that MI->isSelect() is true.

When successful, return the controlling condition and the operands that determine the true and false result values.

Result = SELECT Cond, TrueOp, FalseOp

Some targets can optimize select instructions, for example by predicating the instruction defining one of the operands. Such targets should set Optimizable.

- Parameters

-

MI Select instruction to analyze. Cond Condition controlling the select. TrueOp Operand number of the value selected when Cond is true. FalseOp Operand number of the value selected when Cond is false. Optimizable Returned as true if MI is optimizable.

- Returns

- False on success.

Definition at line 958 of file TargetInstrInfo.h.

◆ areLoadsFromSameBasePtr()

|

inlinevirtual |

This is used by the pre-regalloc scheduler to determine if two loads are loading from the same base address.

It should only return true if the base pointers are the same and the only differences between the two addresses are the offset. It also returns the offsets by reference.

Definition at line 1420 of file TargetInstrInfo.h.

◆ areMemAccessesTriviallyDisjoint()

|

inlinevirtual |

Sometimes, it is possible for the target to tell, even without aliasing information, that two MIs access different memory addresses.

This function returns true if two MIs access different memory addresses and false otherwise.

Assumes any physical registers used to compute addresses have the same value for both instructions. (This is the most useful assumption for post-RA scheduling.)

See also MachineInstr::mayAlias, which is implemented on top of this function.

Definition at line 1940 of file TargetInstrInfo.h.

References assert(), and llvm::MachineInstr::mayLoadOrStore().

◆ areOpcodesEqualOrInverse()

Return true when \P Opcode1 or its inversion is equal to \P Opcode2.

Definition at line 852 of file TargetInstrInfo.cpp.

References getInverseOpcode().

Referenced by getReassociationOpcodes(), and hasReassociableSibling().

◆ breakPartialRegDependency()

|

inlinevirtual |

Insert a dependency-breaking instruction before MI to eliminate an unwanted dependency on OpNum.

If it wasn't possible to avoid a def in the last N instructions before MI (see getPartialRegUpdateClearance), this hook will be called to break the unwanted dependency.

On x86, an xorps instruction can be used as a dependency breaker:

addps xmm1, xmm0 movaps xmm0, (rax) xorps xmm0, xmm0 cvtsi2ss rbx, xmm0

An <imp-kill> operand should be added to MI if an instruction was inserted. This ties the instructions together in the post-ra scheduler.

Definition at line 1919 of file TargetInstrInfo.h.

◆ buildClearRegister()

|

inlinevirtual |

Insert an architecture-specific instruction to clear a register.

If you need to avoid sideeffects (e.g. avoid XOR on x86, which sets EFLAGS), set AllowSideEffects to false.

Definition at line 2138 of file TargetInstrInfo.h.

References llvm_unreachable.

◆ buildOutlinedFrame()

|

inlinevirtual |

Insert a custom frame for outlined functions.

Definition at line 2118 of file TargetInstrInfo.h.

References llvm_unreachable.

◆ canCopyGluedNodeDuringSchedule()

|

inlinevirtual |

Return true if the given SDNode can be copied during scheduling even if it has glue.

Definition at line 1316 of file TargetInstrInfo.h.

◆ canFoldIntoAddrMode()

|

inlinevirtual |

Check if it's possible and beneficial to fold the addressing computation AddrI into the addressing mode of the load/store instruction MemI.

The memory instruction is a user of the virtual register Reg, which in turn is the ultimate destination of zero or more COPY instructions from the output register of AddrI. Return the adddressing mode after folding in AM.

Definition at line 1491 of file TargetInstrInfo.h.

◆ canInsertSelect()

|

inlinevirtual |

Return true if it is possible to insert a select instruction that chooses between TrueReg and FalseReg based on the condition code in Cond.

When successful, also return the latency in cycles from TrueReg, FalseReg, and Cond to the destination register. In most cases, a select instruction will be 1 cycle, so CondCycles = TrueCycles = FalseCycles = 1

Some x86 implementations have 2-cycle cmov instructions.

- Parameters

-

MBB Block where select instruction would be inserted. Cond Condition returned by analyzeBranch. DstReg Virtual dest register that the result should write to. TrueReg Virtual register to select when Cond is true. FalseReg Virtual register to select when Cond is false. CondCycles Latency from Cond+Branch to select output. TrueCycles Latency from TrueReg to select output. FalseCycles Latency from FalseReg to select output.

Definition at line 910 of file TargetInstrInfo.h.

◆ canMakeTailCallConditional()

|

inlinevirtual |

Returns true if the tail call can be made conditional on BranchCond.

Definition at line 1593 of file TargetInstrInfo.h.

◆ canPredicatePredicatedInstr()

|

inlinevirtual |

Assumes the instruction is already predicated and returns true if the instruction can be predicated again.

Definition at line 1573 of file TargetInstrInfo.h.

References assert(), isPredicated(), and MI.

◆ ClobbersPredicate()

|

inlinevirtual |

If the specified instruction defines any predicate or condition code register(s) used for predication, returns true as well as the definition predicate(s) by reference.

SkipDead should be set to false at any point that dead predicate instructions should be considered as being defined. A dead predicate instruction is one that is guaranteed to be removed after a call to PredicateInstruction.

Definition at line 1624 of file TargetInstrInfo.h.

◆ commuteInstruction()

| MachineInstr * TargetInstrInfo::commuteInstruction | ( | MachineInstr & | MI, |

| bool | NewMI = false, |

||

| unsigned | OpIdx1 = CommuteAnyOperandIndex, |

||

| unsigned | OpIdx2 = CommuteAnyOperandIndex |

||

| ) | const |

This method commutes the operands of the given machine instruction MI.

The operands to be commuted are specified by their indices OpIdx1 and OpIdx2. OpIdx1 and OpIdx2 arguments may be set to a special value 'CommuteAnyOperandIndex', which means that the method is free to choose any arbitrarily chosen commutable operand. If both arguments are set to 'CommuteAnyOperandIndex' then the method looks for 2 different commutable operands; then commutes them if such operands could be found.

If NewMI is false, MI is modified in place and returned; otherwise, a new machine instruction is created and returned.

Do not call this method for a non-commutable instruction or for non-commuable operands. Even though the instruction is commutable, the method may still fail to commute the operands, null pointer is returned in such cases.

Definition at line 249 of file TargetInstrInfo.cpp.

References assert(), CommuteAnyOperandIndex, commuteInstructionImpl(), findCommutedOpIndices(), and MI.

◆ commuteInstructionImpl()

|

protectedvirtual |

This method commutes the operands of the given machine instruction MI.

The operands to be commuted are specified by their indices OpIdx1 and OpIdx2.

If a target has any instructions that are commutable but require converting to different instructions or making non-trivial changes to commute them, this method can be overloaded to do that. The default implementation simply swaps the commutable operands.

If NewMI is false, MI is modified in place and returned; otherwise, a new machine instruction is created and returned.

Do not call this method for a non-commutable instruction. Even though the instruction is commutable, the method may still fail to commute the operands, null pointer is returned in such cases.

Definition at line 168 of file TargetInstrInfo.cpp.

References assert(), llvm::MachineFunction::CloneMachineInstr(), findCommutedOpIndices(), llvm::MCInstrDesc::getNumDefs(), llvm::MachineInstr::getOperand(), llvm::Register::isPhysical(), MI, llvm::MachineOperand::setIsInternalRead(), llvm::MachineOperand::setIsKill(), llvm::MachineOperand::setIsRenamable(), llvm::MachineOperand::setIsUndef(), llvm::MachineOperand::setReg(), llvm::MachineOperand::setSubReg(), and llvm::MCOI::TIED_TO.

Referenced by commuteInstruction(), llvm::SystemZInstrInfo::commuteInstructionImpl(), llvm::X86InstrInfo::commuteInstructionImpl(), llvm::SIInstrInfo::commuteInstructionImpl(), llvm::ARMBaseInstrInfo::commuteInstructionImpl(), llvm::PPCInstrInfo::commuteInstructionImpl(), llvm::RISCVInstrInfo::commuteInstructionImpl(), and llvm::WebAssemblyInstrInfo::commuteInstructionImpl().

◆ convertToThreeAddress()

|

inlinevirtual |

This method must be implemented by targets that set the M_CONVERTIBLE_TO_3_ADDR flag.

When this flag is set, the target may be able to convert a two-address instruction into one or more true three-address instructions on demand. This allows the X86 target (for example) to convert ADD and SHL instructions into LEA instructions if they would require register copies due to two-addressness.

This method returns a null pointer if the transformation cannot be performed, otherwise it returns the last new instruction.

If LIS is not nullptr, the LiveIntervals info should be updated for replacing MI with new instructions, even though this function does not remove MI.

Definition at line 440 of file TargetInstrInfo.h.

◆ copyPhysReg()

|

inlinevirtual |

Emit instructions to copy a pair of physical registers.

This function should support copies within any legal register class as well as any cross-class copies created during instruction selection.

The source and destination registers may overlap, which may require a careful implementation when multiple copy instructions are required for large registers. See for example the ARM target.

Definition at line 996 of file TargetInstrInfo.h.

References llvm_unreachable.

Referenced by lowerCopy().

◆ createMIROperandComment()

|

virtual |

Definition at line 1732 of file TargetInstrInfo.cpp.

References assert(), F, llvm::First, llvm::InlineAsm::getExtraInfoNames(), llvm::InlineAsm::getMemConstraintName(), Info, MI, llvm::InlineAsm::MIOp_ExtraInfo, OS, and TRI.

Referenced by llvm::ARMBaseInstrInfo::createMIROperandComment(), and llvm::RISCVInstrInfo::createMIROperandComment().

◆ createPHIDestinationCopy()

|

inlinevirtual |

During PHI eleimination lets target to make necessary checks and insert the copy to the PHI destination register in a target specific manner.

Definition at line 2045 of file TargetInstrInfo.h.

References llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), DL, llvm::MCInstrInfo::get(), and MBB.

Referenced by llvm::SIInstrInfo::createPHIDestinationCopy().

◆ createPHISourceCopy()

|

inlinevirtual |

During PHI eleimination lets target to make necessary checks and insert the copy to the PHI destination register in a target specific manner.

Definition at line 2055 of file TargetInstrInfo.h.

References llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), DL, llvm::MCInstrInfo::get(), and MBB.

Referenced by llvm::SIInstrInfo::createPHISourceCopy().

◆ CreateTargetHazardRecognizer()

|

virtual |

Allocate and return a hazard recognizer to use for this target when scheduling the machine instructions before register allocation.

Definition at line 1403 of file TargetInstrInfo.cpp.

Referenced by llvm::ARMBaseInstrInfo::CreateTargetHazardRecognizer(), and llvm::PPCInstrInfo::CreateTargetHazardRecognizer().

◆ CreateTargetMIHazardRecognizer()

|

virtual |

Allocate and return a hazard recognizer to use for this target when scheduling the machine instructions before register allocation.

Definition at line 1411 of file TargetInstrInfo.cpp.

Referenced by llvm::SIInstrInfo::CreateTargetMIHazardRecognizer(), llvm::ARMBaseInstrInfo::CreateTargetMIHazardRecognizer(), llvm::GenericScheduler::initialize(), and llvm::PostGenericScheduler::initialize().

◆ CreateTargetPostRAHazardRecognizer() [1/2]

|

virtual |

Allocate and return a hazard recognizer to use for this target when scheduling the machine instructions after register allocation.

Definition at line 1417 of file TargetInstrInfo.cpp.

Referenced by llvm::ARMBaseInstrInfo::CreateTargetPostRAHazardRecognizer(), and llvm::HexagonInstrInfo::CreateTargetPostRAHazardRecognizer().

◆ CreateTargetPostRAHazardRecognizer() [2/2]

|

inlinevirtual |

Allocate and return a hazard recognizer to use for by non-scheduling passes.

Definition at line 1676 of file TargetInstrInfo.h.

◆ CreateTargetScheduleState()

|

inlinevirtual |

Create machine specific model for scheduling.

Definition at line 1924 of file TargetInstrInfo.h.

Referenced by llvm::VLIWResourceModel::createPacketizer(), llvm::ResourcePriorityQueue::ResourcePriorityQueue(), and llvm::VLIWPacketizerList::VLIWPacketizerList().

◆ decomposeMachineOperandsTargetFlags()

|

inlinevirtual |

Decompose the machine operand's target flags into two values - the direct target flag value and any of bit flags that are applied.

Definition at line 1985 of file TargetInstrInfo.h.

◆ defaultDefLatency()

| unsigned TargetInstrInfo::defaultDefLatency | ( | const MCSchedModel & | SchedModel, |

| const MachineInstr & | DefMI | ||

| ) | const |

Return the default expected latency for a def based on its opcode.

Return the default expected latency for a def based on it's opcode.

Definition at line 1489 of file TargetInstrInfo.cpp.

References DefMI, llvm::MCSchedModel::HighLatency, isHighLatencyDef(), and llvm::MCSchedModel::LoadLatency.

Referenced by llvm::TargetSchedModel::computeInstrLatency(), and llvm::TargetSchedModel::computeOperandLatency().

◆ describeLoadedValue()

|

virtual |

Produce the expression describing the MI loading a value into the physical register Reg.

This hook should only be used with MIs belonging to VReg-less functions.

Definition at line 1548 of file TargetInstrInfo.cpp.

References llvm::DIExpression::appendOffset(), llvm::DIExpression::ApplyOffset, assert(), llvm::MachineOperand::CreateReg(), llvm::MDNode::get(), llvm::Function::getContext(), llvm::MachineFunction::getFrameInfo(), llvm::MachineFunction::getFunction(), llvm::TargetSubtargetInfo::getInstrInfo(), llvm::MachineFunction::getProperties(), llvm::MachineMemOperand::getPseudoValue(), llvm::TargetSubtargetInfo::getRegisterInfo(), llvm::MachineMemOperand::getSize(), llvm::MachineFunction::getSubtarget(), llvm::LocationSize::getValue(), llvm::MachineFunctionProperties::hasProperty(), llvm::LocationSize::hasValue(), isAddImmediate(), isCopyInstr(), llvm::PseudoSourceValue::mayAlias(), MI, llvm::MachineFunctionProperties::NoVRegs, llvm::Offset, llvm::DIExpression::prepend(), llvm::DIExpression::prependOpcodes(), llvm::SmallVectorTemplateBase< T, bool >::push_back(), TII, and TRI.

Referenced by llvm::AArch64InstrInfo::describeLoadedValue(), llvm::ARMBaseInstrInfo::describeLoadedValue(), llvm::MipsInstrInfo::describeLoadedValue(), and llvm::X86InstrInfo::describeLoadedValue().

◆ duplicate()

|

virtual |

Clones instruction or the whole instruction bundle Orig and insert into MBB before InsertBefore.

The target may update operands that are required to be unique.

Orig must not return true for MachineInstr::isNotDuplicable().

Definition at line 435 of file TargetInstrInfo.cpp.

References assert(), llvm::MachineFunction::cloneMachineInstrBundle(), llvm::MachineBasicBlock::getParent(), llvm::MachineFunction::getTarget(), llvm::TargetMachine::getTargetTriple(), llvm::MachineInstr::isCFIInstruction(), llvm::MachineInstr::isNotDuplicable(), llvm::Triple::isOSDarwin(), and MBB.

Referenced by llvm::ARMBaseInstrInfo::duplicate().

◆ emitLdStWithAddr()

|

inlinevirtual |

Emit a load/store instruction with the same value register as MemI, but using the address from AM.

The addressing mode must have been obtained from canFoldIntoAddr for the same memory instruction.

Definition at line 1500 of file TargetInstrInfo.h.

References llvm_unreachable.

◆ expandPostRAPseudo()

|

inlinevirtual |

This function is called for all pseudo instructions that remain after register allocation.

Many pseudo instructions are created to help register allocation. This is the place to convert them into real instructions. The target can edit MI in place, or it can insert new instructions and erase MI. The function should return true if anything was changed.

Definition at line 1139 of file TargetInstrInfo.h.

Referenced by llvm::SIInstrInfo::expandPostRAPseudo().

◆ extraSizeToPredicateInstructions()

|

inlinevirtual |

Return the increase in code size needed to predicate a contiguous run of NumInsts instructions.

Definition at line 865 of file TargetInstrInfo.h.

◆ finalizeInsInstrs()

|

inlinevirtual |

Fix up the placeholder we may add in genAlternativeCodeSequence().

Definition at line 1209 of file TargetInstrInfo.h.

◆ findCommutedOpIndices()

|

virtual |

Returns true iff the routine could find two commutable operands in the given machine instruction.

The 'SrcOpIdx1' and 'SrcOpIdx2' are INPUT and OUTPUT arguments. If any of the INPUT values is set to the special value 'CommuteAnyOperandIndex' then the method arbitrarily picks a commutable operand, then returns its index in the corresponding argument. If both of INPUT values are set to 'CommuteAnyOperandIndex' then method looks for 2 commutable operands. If INPUT values refer to some operands of MI, then the method simply returns true if the corresponding operands are commutable and returns false otherwise.

For example, calling this method this way: unsigned Op1 = 1, Op2 = CommuteAnyOperandIndex; findCommutedOpIndices(MI, Op1, Op2); can be interpreted as a query asking to find an operand that would be commutable with the operand#1.

Definition at line 295 of file TargetInstrInfo.cpp.

References assert(), fixCommutedOpIndices(), llvm::MCInstrDesc::getNumDefs(), llvm::MCInstrDesc::isCommutable(), and MI.

Referenced by commuteInstruction(), commuteInstructionImpl(), llvm::MipsInstrInfo::findCommutedOpIndices(), llvm::PPCInstrInfo::findCommutedOpIndices(), llvm::RISCVInstrInfo::findCommutedOpIndices(), and llvm::X86InstrInfo::findCommutedOpIndices().

◆ fixCommutedOpIndices()

|

staticprotected |

Assigns the (CommutableOpIdx1, CommutableOpIdx2) pair of commutable operand indices to (ResultIdx1, ResultIdx2).

One or both input values of the pair: (ResultIdx1, ResultIdx2) may be predefined to some indices or be undefined (designated by the special value 'CommuteAnyOperandIndex'). The predefined result indices cannot be re-defined. The function returns true iff after the result pair redefinition the fixed result pair is equal to or equivalent to the source pair of indices: (CommutableOpIdx1, CommutableOpIdx2). It is assumed here that the pairs (x,y) and (y,x) are equivalent.

Definition at line 264 of file TargetInstrInfo.cpp.

References CommuteAnyOperandIndex.

Referenced by findCommutedOpIndices().

◆ foldImmediate()

|

inlinevirtual |

'Reg' is known to be defined by a move immediate instruction, try to fold the immediate into the use instruction.

If MRI->hasOneNonDBGUse(Reg) is true, and this function returns true, then the caller may assume that DefMI has been erased from its parent block. The caller may assume that it will not be erased by this function otherwise.

Definition at line 1725 of file TargetInstrInfo.h.

◆ foldMemoryOperand() [1/2]

| MachineInstr * TargetInstrInfo::foldMemoryOperand | ( | MachineInstr & | MI, |

| ArrayRef< unsigned > | Ops, | ||

| int | FI, | ||

| LiveIntervals * | LIS = nullptr, |

||

| VirtRegMap * | VRM = nullptr |

||

| ) | const |

Attempt to fold a load or store of the specified stack slot into the specified machine instruction for the specified operand(s).

If this is possible, a new instruction is returned with the specified operand folded, otherwise NULL is returned. The new instruction is inserted before MI, and the client is responsible for removing the old instruction. If VRM is passed, the assigned physregs can be inspected by target to decide on using an opcode (note that those assignments can still change).

Definition at line 634 of file TargetInstrInfo.cpp.

References llvm::MachineInstr::addMemOperand(), assert(), canFoldCopy(), llvm::MachineInstr::cloneInstrSymbols(), foldInlineAsmMemOperand(), foldMemoryOperandImpl(), foldPatchpoint(), llvm::MachinePointerInfo::getFixedStack(), llvm::MachineFunction::getFrameInfo(), llvm::MachineFunction::getMachineMemOperand(), llvm::MachineFrameInfo::getObjectAlign(), llvm::MachineFrameInfo::getObjectOffset(), llvm::MachineFrameInfo::getObjectSize(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), llvm::TargetSubtargetInfo::getRegisterInfo(), llvm::MachineFunction::getSubtarget(), llvm::MachineBasicBlock::insert(), isCopyInstr(), llvm::MachineOperand::isKill(), loadRegFromStackSlot(), llvm::MachineInstr::mayLoad(), llvm::MachineInstr::mayStore(), MBB, MI, llvm::MachineMemOperand::MOLoad, llvm::MachineMemOperand::MONone, llvm::MachineMemOperand::MOStore, llvm::MachineInstr::setMemRefs(), llvm::ArrayRef< T >::size(), storeRegToStackSlot(), SubReg, and TRI.

◆ foldMemoryOperand() [2/2]

| MachineInstr * TargetInstrInfo::foldMemoryOperand | ( | MachineInstr & | MI, |

| ArrayRef< unsigned > | Ops, | ||

| MachineInstr & | LoadMI, | ||

| LiveIntervals * | LIS = nullptr |

||

| ) | const |

Same as the previous version except it allows folding of any load and store from / to any address, not just from a specific stack slot.

Definition at line 729 of file TargetInstrInfo.cpp.

References llvm::MachineInstr::addMemOperand(), assert(), llvm::MachineInstr::canFoldAsLoad(), foldInlineAsmMemOperand(), foldMemoryOperandImpl(), foldPatchpoint(), llvm::MachineBasicBlock::getParent(), I, llvm::MachineBasicBlock::insert(), isLoadFromStackSlot(), MBB, llvm::MachineInstr::memoperands(), llvm::MachineInstr::memoperands_begin(), llvm::MachineInstr::memoperands_end(), MI, and llvm::MachineInstr::setMemRefs().

◆ foldMemoryOperandImpl() [1/2]

|

inlineprotectedvirtual |

Target-dependent implementation for foldMemoryOperand.

Target-independent code in foldMemoryOperand will take care of adding a MachineMemOperand to the newly created instruction. The instruction and any auxiliary instructions necessary will be inserted at InsertPt.

Definition at line 1325 of file TargetInstrInfo.h.

Referenced by foldMemoryOperand().

◆ foldMemoryOperandImpl() [2/2]

|

inlineprotectedvirtual |

Target-dependent implementation for foldMemoryOperand.

Target-independent code in foldMemoryOperand will take care of adding a MachineMemOperand to the newly created instruction. The instruction and any auxiliary instructions necessary will be inserted at InsertPt.

Definition at line 1338 of file TargetInstrInfo.h.

◆ genAlternativeCodeSequence()

|

virtual |

When getMachineCombinerPatterns() finds patterns, this function generates the instructions that could replace the original code sequence.

The client has to decide whether the actual replacement is beneficial or not.

- Parameters

-

Root - Instruction that could be combined with one of its operands Pattern - Combination pattern for Root InsInstrs - Vector of new instructions that implement P DelInstrs - Old instructions, including Root, that could be replaced by InsInstr InstIdxForVirtReg - map of virtual register to instruction in InsInstr that defines it

Definition at line 1247 of file TargetInstrInfo.cpp.

References llvm::MachineInstr::getMF(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), getReassociateOperandIndices(), llvm::MachineOperand::getReg(), llvm::MachineFunction::getRegInfo(), MRI, and reassociateOps().

Referenced by llvm::AArch64InstrInfo::genAlternativeCodeSequence(), llvm::PPCInstrInfo::genAlternativeCodeSequence(), llvm::RISCVInstrInfo::genAlternativeCodeSequence(), and llvm::X86InstrInfo::genAlternativeCodeSequence().

◆ getAddrModeFromMemoryOp()

|

inlinevirtual |

Target dependent implementation to get the values constituting the address MachineInstr that is accessing memory.

These values are returned as a struct ExtAddrMode which contains all relevant information to make up the address.

Definition at line 1480 of file TargetInstrInfo.h.

◆ getBaseAndOffsetPosition()

|

inlinevirtual |

Return true if the instruction contains a base register and offset.

If true, the function also sets the operand position in the instruction for the base register and offset.

Definition at line 1469 of file TargetInstrInfo.h.

Referenced by llvm::SwingSchedulerDAG::applyInstrChange(), and llvm::SwingSchedulerDAG::fixupRegisterOverlaps().

◆ getBranchDestBlock()

|

inlinevirtual |

- Returns

- The block that branch instruction

MIjumps to.

Definition at line 607 of file TargetInstrInfo.h.

References llvm_unreachable.

◆ getCalleeOperand()

|

inlinevirtual |

Returns the callee operand from the given MI.

Definition at line 2206 of file TargetInstrInfo.h.

References MI.

◆ getCallFrameDestroyOpcode()

|

inline |

Definition at line 211 of file TargetInstrInfo.h.

Referenced by llvm::M68kFrameLowering::eliminateCallFramePseudoInstr(), getCallFrameSizeAt(), getSPAdjust(), isFrameInstr(), and llvm::FastISel::selectStackmap().

◆ getCallFrameSetupOpcode()

|

inline |

These methods return the opcode of the frame setup/destroy instructions if they exist (-1 otherwise).

Some targets use pseudo instructions in order to abstract away the difference between operating with a frame pointer and operating without, through the use of these two instructions. A FrameSetup MI in MF implies MFI::AdjustsStack.

Definition at line 210 of file TargetInstrInfo.h.

Referenced by getCallFrameSizeAt(), getSPAdjust(), isFrameInstr(), isFrameSetup(), and llvm::FastISel::selectStackmap().

◆ getCallFrameSizeAt()

| unsigned TargetInstrInfo::getCallFrameSizeAt | ( | MachineInstr & | MI | ) | const |

Definition at line 1626 of file TargetInstrInfo.cpp.

References getCallFrameDestroyOpcode(), getCallFrameSetupOpcode(), llvm::MachineBasicBlock::getCallFrameSize(), getFrameTotalSize(), llvm::MachineBasicBlock::instr_begin(), llvm::make_range(), MBB, MI, and llvm::reverse().

◆ getCatchReturnOpcode()

|

inline |

Definition at line 250 of file TargetInstrInfo.h.

◆ getCombinerObjective()

|

virtual |

Return the objective of a combiner pattern.

- Parameters

-

Pattern - combiner pattern

Definition at line 949 of file TargetInstrInfo.cpp.

References llvm::Default.

Referenced by llvm::AArch64InstrInfo::getCombinerObjective(), llvm::PPCInstrInfo::getCombinerObjective(), and llvm::RISCVInstrInfo::getCombinerObjective().

◆ getConstValDefinedInReg()

|

inlinevirtual |

Returns true if MI is an instruction that defines Reg to have a constant value and the value is recorded in ImmVal.