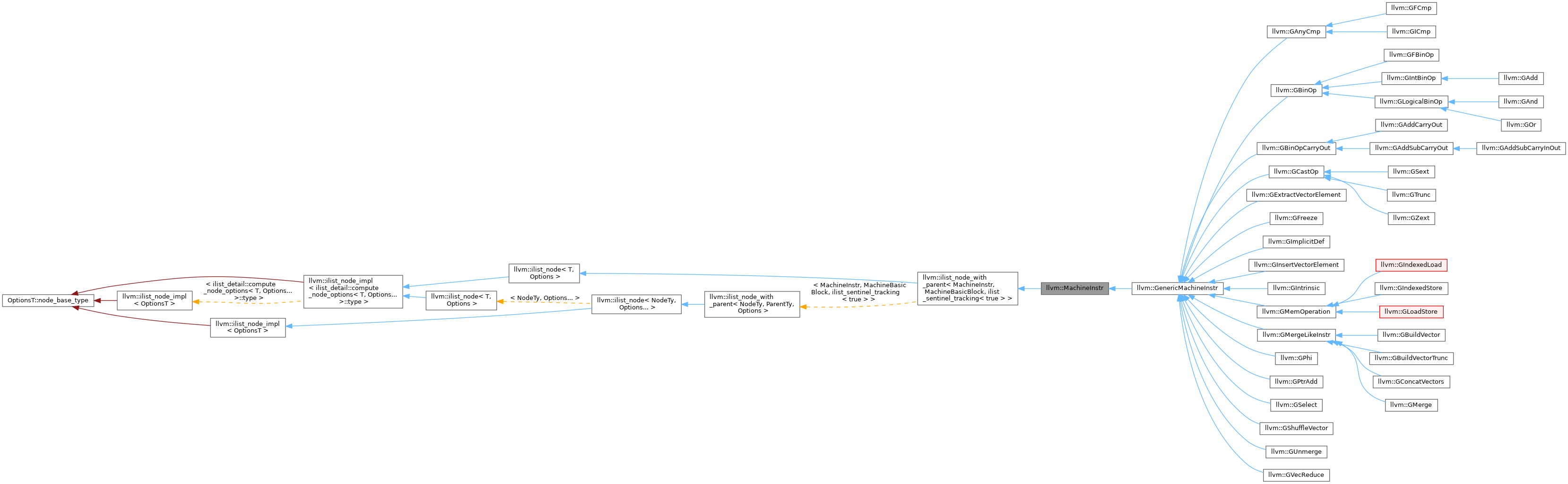

Representation of each machine instruction. More...

#include "llvm/CodeGen/MachineInstr.h"

Public Types | |

| enum | CommentFlag { ReloadReuse = 0x1 , NoSchedComment = 0x2 , TAsmComments = 0x4 } |

| Flags to specify different kinds of comments to output in assembly code. More... | |

| enum | MIFlag { NoFlags = 0 , FrameSetup = 1 << 0 , FrameDestroy = 1 << 1 , BundledPred = 1 << 2 , BundledSucc = 1 << 3 , FmNoNans = 1 << 4 , FmNoInfs = 1 << 5 , FmNsz = 1 << 6 , FmArcp = 1 << 7 , FmContract = 1 << 8 , FmAfn = 1 << 9 , FmReassoc = 1 << 10 , NoUWrap = 1 << 11 , NoSWrap = 1 << 12 , IsExact = 1 << 13 , NoFPExcept = 1 << 14 , NoMerge = 1 << 15 , Unpredictable = 1 << 16 , NoConvergent = 1 << 17 , NonNeg = 1 << 18 , Disjoint = 1 << 19 } |

| enum | QueryType { IgnoreBundle , AnyInBundle , AllInBundle } |

| API for querying MachineInstr properties. More... | |

| enum | MICheckType { CheckDefs , CheckKillDead , IgnoreDefs , IgnoreVRegDefs } |

| using | mmo_iterator = ArrayRef< MachineMemOperand * >::iterator |

| using | mop_iterator = MachineOperand * |

| iterator/begin/end - Iterate over all operands of a machine instruction. | |

| using | const_mop_iterator = const MachineOperand * |

| using | filtered_mop_iterator = filter_iterator< mop_iterator, bool(*)(const MachineOperand &)> |

| using | filtered_const_mop_iterator = filter_iterator< const_mop_iterator, bool(*)(const MachineOperand &)> |

Public Member Functions | |

| MachineInstr (const MachineInstr &)=delete | |

| MachineInstr & | operator= (const MachineInstr &)=delete |

| ~MachineInstr ()=delete | |

| const MachineBasicBlock * | getParent () const |

| MachineBasicBlock * | getParent () |

| void | moveBefore (MachineInstr *MovePos) |

Move the instruction before MovePos. | |

| const MachineFunction * | getMF () const |

| Return the function that contains the basic block that this instruction belongs to. | |

| MachineFunction * | getMF () |

| uint8_t | getAsmPrinterFlags () const |

| Return the asm printer flags bitvector. | |

| void | clearAsmPrinterFlags () |

| Clear the AsmPrinter bitvector. | |

| bool | getAsmPrinterFlag (CommentFlag Flag) const |

| Return whether an AsmPrinter flag is set. | |

| void | setAsmPrinterFlag (uint8_t Flag) |

| Set a flag for the AsmPrinter. | |

| void | clearAsmPrinterFlag (CommentFlag Flag) |

| Clear specific AsmPrinter flags. | |

| uint32_t | getFlags () const |

| Return the MI flags bitvector. | |

| bool | getFlag (MIFlag Flag) const |

| Return whether an MI flag is set. | |

| void | setFlag (MIFlag Flag) |

| Set a MI flag. | |

| void | setFlags (unsigned flags) |

| void | clearFlag (MIFlag Flag) |

| clearFlag - Clear a MI flag. | |

| bool | isInsideBundle () const |

| Return true if MI is in a bundle (but not the first MI in a bundle). | |

| bool | isBundled () const |

| Return true if this instruction part of a bundle. | |

| bool | isBundledWithPred () const |

| Return true if this instruction is part of a bundle, and it is not the first instruction in the bundle. | |

| bool | isBundledWithSucc () const |

| Return true if this instruction is part of a bundle, and it is not the last instruction in the bundle. | |

| void | bundleWithPred () |

| Bundle this instruction with its predecessor. | |

| void | bundleWithSucc () |

| Bundle this instruction with its successor. | |

| void | unbundleFromPred () |

| Break bundle above this instruction. | |

| void | unbundleFromSucc () |

| Break bundle below this instruction. | |

| const DebugLoc & | getDebugLoc () const |

| Returns the debug location id of this MachineInstr. | |

| const MachineOperand & | getDebugOffset () const |

| Return the operand containing the offset to be used if this DBG_VALUE instruction is indirect; will be an invalid register if this value is not indirect, and an immediate with value 0 otherwise. | |

| MachineOperand & | getDebugOffset () |

| const MachineOperand & | getDebugVariableOp () const |

| Return the operand for the debug variable referenced by this DBG_VALUE instruction. | |

| MachineOperand & | getDebugVariableOp () |

| const DILocalVariable * | getDebugVariable () const |

| Return the debug variable referenced by this DBG_VALUE instruction. | |

| const MachineOperand & | getDebugExpressionOp () const |

| Return the operand for the complex address expression referenced by this DBG_VALUE instruction. | |

| MachineOperand & | getDebugExpressionOp () |

| const DIExpression * | getDebugExpression () const |

| Return the complex address expression referenced by this DBG_VALUE instruction. | |

| const DILabel * | getDebugLabel () const |

| Return the debug label referenced by this DBG_LABEL instruction. | |

| unsigned | getDebugInstrNum () |

| Fetch the instruction number of this MachineInstr. | |

| unsigned | getDebugInstrNum (MachineFunction &MF) |

Fetch instruction number of this MachineInstr – but before it's inserted into MF. | |

| unsigned | peekDebugInstrNum () const |

| Examine the instruction number of this MachineInstr. | |

| void | setDebugInstrNum (unsigned Num) |

| Set instruction number of this MachineInstr. | |

| void | dropDebugNumber () |

| Drop any variable location debugging information associated with this instruction. | |

| void | emitError (StringRef Msg) const |

| Emit an error referring to the source location of this instruction. | |

| const MCInstrDesc & | getDesc () const |

| Returns the target instruction descriptor of this MachineInstr. | |

| unsigned | getOpcode () const |

| Returns the opcode of this MachineInstr. | |

| unsigned | getNumOperands () const |

| Retuns the total number of operands. | |

| unsigned | getNumDebugOperands () const |

| Returns the total number of operands which are debug locations. | |

| const MachineOperand & | getOperand (unsigned i) const |

| MachineOperand & | getOperand (unsigned i) |

| MachineOperand & | getDebugOperand (unsigned Index) |

| const MachineOperand & | getDebugOperand (unsigned Index) const |

| bool | hasDebugOperandForReg (Register Reg) const |

Returns whether this debug value has at least one debug operand with the register Reg. | |

| iterator_range< filter_iterator< const MachineOperand *, std::function< bool(const MachineOperand &Op)> > > | getDebugOperandsForReg (Register Reg) const |

| iterator_range< filter_iterator< MachineOperand *, std::function< bool(MachineOperand &Op)> > > | getDebugOperandsForReg (Register Reg) |

| bool | isDebugOperand (const MachineOperand *Op) const |

| unsigned | getDebugOperandIndex (const MachineOperand *Op) const |

| unsigned | getNumDefs () const |

| Returns the total number of definitions. | |

| bool | hasImplicitDef () const |

| Returns true if the instruction has implicit definition. | |

| unsigned | getNumImplicitOperands () const |

| Returns the implicit operands number. | |

| bool | isOperandSubregIdx (unsigned OpIdx) const |

Return true if operand OpIdx is a subregister index. | |

| unsigned | getNumExplicitOperands () const |

| Returns the number of non-implicit operands. | |

| unsigned | getNumExplicitDefs () const |

| Returns the number of non-implicit definitions. | |

| mop_iterator | operands_begin () |

| mop_iterator | operands_end () |

| const_mop_iterator | operands_begin () const |

| const_mop_iterator | operands_end () const |

| iterator_range< mop_iterator > | operands () |

| iterator_range< const_mop_iterator > | operands () const |

| iterator_range< mop_iterator > | explicit_operands () |

| iterator_range< const_mop_iterator > | explicit_operands () const |

| iterator_range< mop_iterator > | implicit_operands () |

| iterator_range< const_mop_iterator > | implicit_operands () const |

| iterator_range< mop_iterator > | debug_operands () |

| Returns a range over all operands that are used to determine the variable location for this DBG_VALUE instruction. | |

| iterator_range< const_mop_iterator > | debug_operands () const |

| Returns a range over all operands that are used to determine the variable location for this DBG_VALUE instruction. | |

| iterator_range< mop_iterator > | defs () |

| Returns a range over all explicit operands that are register definitions. | |

| iterator_range< const_mop_iterator > | defs () const |

| Returns a range over all explicit operands that are register definitions. | |

| iterator_range< mop_iterator > | uses () |

| Returns a range that includes all operands that are register uses. | |

| iterator_range< const_mop_iterator > | uses () const |

| Returns a range that includes all operands that are register uses. | |

| iterator_range< mop_iterator > | explicit_uses () |

| iterator_range< const_mop_iterator > | explicit_uses () const |

| iterator_range< filtered_mop_iterator > | all_defs () |

| Returns an iterator range over all operands that are (explicit or implicit) register defs. | |

| iterator_range< filtered_const_mop_iterator > | all_defs () const |

| Returns an iterator range over all operands that are (explicit or implicit) register defs. | |

| iterator_range< filtered_mop_iterator > | all_uses () |

| Returns an iterator range over all operands that are (explicit or implicit) register uses. | |

| iterator_range< filtered_const_mop_iterator > | all_uses () const |

| Returns an iterator range over all operands that are (explicit or implicit) register uses. | |

| unsigned | getOperandNo (const_mop_iterator I) const |

Returns the number of the operand iterator I points to. | |

| ArrayRef< MachineMemOperand * > | memoperands () const |

| Access to memory operands of the instruction. | |

| mmo_iterator | memoperands_begin () const |

| Access to memory operands of the instruction. | |

| mmo_iterator | memoperands_end () const |

| Access to memory operands of the instruction. | |

| bool | memoperands_empty () const |

| Return true if we don't have any memory operands which described the memory access done by this instruction. | |

| bool | hasOneMemOperand () const |

| Return true if this instruction has exactly one MachineMemOperand. | |

| unsigned | getNumMemOperands () const |

| Return the number of memory operands. | |

| MCSymbol * | getPreInstrSymbol () const |

| Helper to extract a pre-instruction symbol if one has been added. | |

| MCSymbol * | getPostInstrSymbol () const |

| Helper to extract a post-instruction symbol if one has been added. | |

| MDNode * | getHeapAllocMarker () const |

| Helper to extract a heap alloc marker if one has been added. | |

| MDNode * | getPCSections () const |

| Helper to extract PCSections metadata target sections. | |

| MDNode * | getMMRAMetadata () const |

| Helper to extract mmra.op metadata. | |

| uint32_t | getCFIType () const |

| Helper to extract a CFI type hash if one has been added. | |

| bool | hasProperty (unsigned MCFlag, QueryType Type=AnyInBundle) const |

| Return true if the instruction (or in the case of a bundle, the instructions inside the bundle) has the specified property. | |

| bool | isPreISelOpcode (QueryType Type=IgnoreBundle) const |

| Return true if this is an instruction that should go through the usual legalization steps. | |

| bool | isVariadic (QueryType Type=IgnoreBundle) const |

| Return true if this instruction can have a variable number of operands. | |

| bool | hasOptionalDef (QueryType Type=IgnoreBundle) const |

| Set if this instruction has an optional definition, e.g. | |

| bool | isPseudo (QueryType Type=IgnoreBundle) const |

| Return true if this is a pseudo instruction that doesn't correspond to a real machine instruction. | |

| bool | isMetaInstruction (QueryType Type=IgnoreBundle) const |

| Return true if this instruction doesn't produce any output in the form of executable instructions. | |

| bool | isReturn (QueryType Type=AnyInBundle) const |

| bool | isEHScopeReturn (QueryType Type=AnyInBundle) const |

| Return true if this is an instruction that marks the end of an EH scope, i.e., a catchpad or a cleanuppad instruction. | |

| bool | isCall (QueryType Type=AnyInBundle) const |

| bool | isCandidateForCallSiteEntry (QueryType Type=IgnoreBundle) const |

| Return true if this is a call instruction that may have an associated call site entry in the debug info. | |

| bool | shouldUpdateCallSiteInfo () const |

| Return true if copying, moving, or erasing this instruction requires updating Call Site Info (see copyCallSiteInfo, moveCallSiteInfo, eraseCallSiteInfo). | |

| bool | isBarrier (QueryType Type=AnyInBundle) const |

| Returns true if the specified instruction stops control flow from executing the instruction immediately following it. | |

| bool | isTerminator (QueryType Type=AnyInBundle) const |

| Returns true if this instruction part of the terminator for a basic block. | |

| bool | isBranch (QueryType Type=AnyInBundle) const |

| Returns true if this is a conditional, unconditional, or indirect branch. | |

| bool | isIndirectBranch (QueryType Type=AnyInBundle) const |

| Return true if this is an indirect branch, such as a branch through a register. | |

| bool | isConditionalBranch (QueryType Type=AnyInBundle) const |

| Return true if this is a branch which may fall through to the next instruction or may transfer control flow to some other block. | |

| bool | isUnconditionalBranch (QueryType Type=AnyInBundle) const |

| Return true if this is a branch which always transfers control flow to some other block. | |

| bool | isPredicable (QueryType Type=AllInBundle) const |

| Return true if this instruction has a predicate operand that controls execution. | |

| bool | isCompare (QueryType Type=IgnoreBundle) const |

| Return true if this instruction is a comparison. | |

| bool | isMoveImmediate (QueryType Type=IgnoreBundle) const |

| Return true if this instruction is a move immediate (including conditional moves) instruction. | |

| bool | isMoveReg (QueryType Type=IgnoreBundle) const |

| Return true if this instruction is a register move. | |

| bool | isBitcast (QueryType Type=IgnoreBundle) const |

| Return true if this instruction is a bitcast instruction. | |

| bool | isSelect (QueryType Type=IgnoreBundle) const |

| Return true if this instruction is a select instruction. | |

| bool | isNotDuplicable (QueryType Type=AnyInBundle) const |

| Return true if this instruction cannot be safely duplicated. | |

| bool | isConvergent (QueryType Type=AnyInBundle) const |

| Return true if this instruction is convergent. | |

| bool | hasDelaySlot (QueryType Type=AnyInBundle) const |

| Returns true if the specified instruction has a delay slot which must be filled by the code generator. | |

| bool | canFoldAsLoad (QueryType Type=IgnoreBundle) const |

| Return true for instructions that can be folded as memory operands in other instructions. | |

| bool | isRegSequenceLike (QueryType Type=IgnoreBundle) const |

| Return true if this instruction behaves the same way as the generic REG_SEQUENCE instructions. | |

| bool | isExtractSubregLike (QueryType Type=IgnoreBundle) const |

| Return true if this instruction behaves the same way as the generic EXTRACT_SUBREG instructions. | |

| bool | isInsertSubregLike (QueryType Type=IgnoreBundle) const |

| Return true if this instruction behaves the same way as the generic INSERT_SUBREG instructions. | |

| bool | mayLoad (QueryType Type=AnyInBundle) const |

| Return true if this instruction could possibly read memory. | |

| bool | mayStore (QueryType Type=AnyInBundle) const |

| Return true if this instruction could possibly modify memory. | |

| bool | mayLoadOrStore (QueryType Type=AnyInBundle) const |

| Return true if this instruction could possibly read or modify memory. | |

| bool | mayRaiseFPException () const |

| Return true if this instruction could possibly raise a floating-point exception. | |

| bool | isCommutable (QueryType Type=IgnoreBundle) const |

| Return true if this may be a 2- or 3-address instruction (of the form "X = op Y, Z, ..."), which produces the same result if Y and Z are exchanged. | |

| bool | isConvertibleTo3Addr (QueryType Type=IgnoreBundle) const |

| Return true if this is a 2-address instruction which can be changed into a 3-address instruction if needed. | |

| bool | usesCustomInsertionHook (QueryType Type=IgnoreBundle) const |

| Return true if this instruction requires custom insertion support when the DAG scheduler is inserting it into a machine basic block. | |

| bool | hasPostISelHook (QueryType Type=IgnoreBundle) const |

| Return true if this instruction requires adjustment after instruction selection by calling a target hook. | |

| bool | isRematerializable (QueryType Type=AllInBundle) const |

| Returns true if this instruction is a candidate for remat. | |

| bool | isAsCheapAsAMove (QueryType Type=AllInBundle) const |

| Returns true if this instruction has the same cost (or less) than a move instruction. | |

| bool | hasExtraSrcRegAllocReq (QueryType Type=AnyInBundle) const |

| Returns true if this instruction source operands have special register allocation requirements that are not captured by the operand register classes. | |

| bool | hasExtraDefRegAllocReq (QueryType Type=AnyInBundle) const |

| Returns true if this instruction def operands have special register allocation requirements that are not captured by the operand register classes. | |

| bool | isIdenticalTo (const MachineInstr &Other, MICheckType Check=CheckDefs) const |

Return true if this instruction is identical to Other. | |

| bool | isEquivalentDbgInstr (const MachineInstr &Other) const |

Returns true if this instruction is a debug instruction that represents an identical debug value to Other. | |

| MachineInstr * | removeFromParent () |

| Unlink 'this' from the containing basic block, and return it without deleting it. | |

| MachineInstr * | removeFromBundle () |

| Unlink this instruction from its basic block and return it without deleting it. | |

| void | eraseFromParent () |

| Unlink 'this' from the containing basic block and delete it. | |

| void | eraseFromBundle () |

| Unlink 'this' from its basic block and delete it. | |

| bool | isEHLabel () const |

| bool | isGCLabel () const |

| bool | isAnnotationLabel () const |

| bool | isLabel () const |

| Returns true if the MachineInstr represents a label. | |

| bool | isCFIInstruction () const |

| bool | isPseudoProbe () const |

| bool | isPosition () const |

| bool | isNonListDebugValue () const |

| bool | isDebugValueList () const |

| bool | isDebugValue () const |

| bool | isDebugLabel () const |

| bool | isDebugRef () const |

| bool | isDebugValueLike () const |

| bool | isDebugPHI () const |

| bool | isDebugInstr () const |

| bool | isDebugOrPseudoInstr () const |

| bool | isDebugOffsetImm () const |

| bool | isIndirectDebugValue () const |

| A DBG_VALUE is indirect iff the location operand is a register and the offset operand is an immediate. | |

| bool | isDebugEntryValue () const |

| A DBG_VALUE is an entry value iff its debug expression contains the DW_OP_LLVM_entry_value operation. | |

| bool | isUndefDebugValue () const |

| Return true if the instruction is a debug value which describes a part of a variable as unavailable. | |

| bool | isJumpTableDebugInfo () const |

| bool | isPHI () const |

| bool | isKill () const |

| bool | isImplicitDef () const |

| bool | isInlineAsm () const |

| bool | mayFoldInlineAsmRegOp (unsigned OpId) const |

| Returns true if the register operand can be folded with a load or store into a frame index. | |

| bool | isStackAligningInlineAsm () const |

| InlineAsm::AsmDialect | getInlineAsmDialect () const |

| bool | isInsertSubreg () const |

| bool | isSubregToReg () const |

| bool | isRegSequence () const |

| bool | isBundle () const |

| bool | isCopy () const |

| bool | isFullCopy () const |

| bool | isExtractSubreg () const |

| bool | isCopyLike () const |

| Return true if the instruction behaves like a copy. | |

| bool | isIdentityCopy () const |

| Return true is the instruction is an identity copy. | |

| bool | isTransient () const |

| Return true if this is a transient instruction that is either very likely to be eliminated during register allocation (such as copy-like instructions), or if this instruction doesn't have an execution-time cost. | |

| unsigned | getBundleSize () const |

| Return the number of instructions inside the MI bundle, excluding the bundle header. | |

| bool | readsRegister (Register Reg, const TargetRegisterInfo *TRI) const |

| Return true if the MachineInstr reads the specified register. | |

| bool | readsVirtualRegister (Register Reg) const |

| Return true if the MachineInstr reads the specified virtual register. | |

| std::pair< bool, bool > | readsWritesVirtualRegister (Register Reg, SmallVectorImpl< unsigned > *Ops=nullptr) const |

| Return a pair of bools (reads, writes) indicating if this instruction reads or writes Reg. | |

| bool | killsRegister (Register Reg, const TargetRegisterInfo *TRI) const |

| Return true if the MachineInstr kills the specified register. | |

| bool | definesRegister (Register Reg, const TargetRegisterInfo *TRI) const |

| Return true if the MachineInstr fully defines the specified register. | |

| bool | modifiesRegister (Register Reg, const TargetRegisterInfo *TRI) const |

| Return true if the MachineInstr modifies (fully define or partially define) the specified register. | |

| bool | registerDefIsDead (Register Reg, const TargetRegisterInfo *TRI) const |

| Returns true if the register is dead in this machine instruction. | |

| bool | hasRegisterImplicitUseOperand (Register Reg) const |

| Returns true if the MachineInstr has an implicit-use operand of exactly the given register (not considering sub/super-registers). | |

| int | findRegisterUseOperandIdx (Register Reg, const TargetRegisterInfo *TRI, bool isKill=false) const |

| Returns the operand index that is a use of the specific register or -1 if it is not found. | |

| MachineOperand * | findRegisterUseOperand (Register Reg, const TargetRegisterInfo *TRI, bool isKill=false) |

| Wrapper for findRegisterUseOperandIdx, it returns a pointer to the MachineOperand rather than an index. | |

| const MachineOperand * | findRegisterUseOperand (Register Reg, const TargetRegisterInfo *TRI, bool isKill=false) const |

| int | findRegisterDefOperandIdx (Register Reg, const TargetRegisterInfo *TRI, bool isDead=false, bool Overlap=false) const |

| Returns the operand index that is a def of the specified register or -1 if it is not found. | |

| MachineOperand * | findRegisterDefOperand (Register Reg, const TargetRegisterInfo *TRI, bool isDead=false, bool Overlap=false) |

| Wrapper for findRegisterDefOperandIdx, it returns a pointer to the MachineOperand rather than an index. | |

| const MachineOperand * | findRegisterDefOperand (Register Reg, const TargetRegisterInfo *TRI, bool isDead=false, bool Overlap=false) const |

| int | findFirstPredOperandIdx () const |

| Find the index of the first operand in the operand list that is used to represent the predicate. | |

| int | findInlineAsmFlagIdx (unsigned OpIdx, unsigned *GroupNo=nullptr) const |

| Find the index of the flag word operand that corresponds to operand OpIdx on an inline asm instruction. | |

| const TargetRegisterClass * | getRegClassConstraint (unsigned OpIdx, const TargetInstrInfo *TII, const TargetRegisterInfo *TRI) const |

| Compute the static register class constraint for operand OpIdx. | |

| const TargetRegisterClass * | getRegClassConstraintEffectForVReg (Register Reg, const TargetRegisterClass *CurRC, const TargetInstrInfo *TII, const TargetRegisterInfo *TRI, bool ExploreBundle=false) const |

Applies the constraints (def/use) implied by this MI on Reg to the given CurRC. | |

| const TargetRegisterClass * | getRegClassConstraintEffect (unsigned OpIdx, const TargetRegisterClass *CurRC, const TargetInstrInfo *TII, const TargetRegisterInfo *TRI) const |

Applies the constraints (def/use) implied by the OpIdx operand to the given CurRC. | |

| void | tieOperands (unsigned DefIdx, unsigned UseIdx) |

| Add a tie between the register operands at DefIdx and UseIdx. | |

| unsigned | findTiedOperandIdx (unsigned OpIdx) const |

| Given the index of a tied register operand, find the operand it is tied to. | |

| bool | isRegTiedToUseOperand (unsigned DefOpIdx, unsigned *UseOpIdx=nullptr) const |

| Given the index of a register def operand, check if the register def is tied to a source operand, due to either two-address elimination or inline assembly constraints. | |

| bool | isRegTiedToDefOperand (unsigned UseOpIdx, unsigned *DefOpIdx=nullptr) const |

| Return true if the use operand of the specified index is tied to a def operand. | |

| void | clearKillInfo () |

| Clears kill flags on all operands. | |

| void | substituteRegister (Register FromReg, Register ToReg, unsigned SubIdx, const TargetRegisterInfo &RegInfo) |

| Replace all occurrences of FromReg with ToReg:SubIdx, properly composing subreg indices where necessary. | |

| bool | addRegisterKilled (Register IncomingReg, const TargetRegisterInfo *RegInfo, bool AddIfNotFound=false) |

| We have determined MI kills a register. | |

| void | clearRegisterKills (Register Reg, const TargetRegisterInfo *RegInfo) |

| Clear all kill flags affecting Reg. | |

| bool | addRegisterDead (Register Reg, const TargetRegisterInfo *RegInfo, bool AddIfNotFound=false) |

| We have determined MI defined a register without a use. | |

| void | clearRegisterDeads (Register Reg) |

Clear all dead flags on operands defining register Reg. | |

| void | setRegisterDefReadUndef (Register Reg, bool IsUndef=true) |

Mark all subregister defs of register Reg with the undef flag. | |

| void | addRegisterDefined (Register Reg, const TargetRegisterInfo *RegInfo=nullptr) |

| We have determined MI defines a register. | |

| void | setPhysRegsDeadExcept (ArrayRef< Register > UsedRegs, const TargetRegisterInfo &TRI) |

| Mark every physreg used by this instruction as dead except those in the UsedRegs list. | |

| bool | isSafeToMove (AAResults *AA, bool &SawStore) const |

| Return true if it is safe to move this instruction. | |

| bool | mayAlias (AAResults *AA, const MachineInstr &Other, bool UseTBAA) const |

| Returns true if this instruction's memory access aliases the memory access of Other. | |

| bool | hasOrderedMemoryRef () const |

| Return true if this instruction may have an ordered or volatile memory reference, or if the information describing the memory reference is not available. | |

| bool | isDereferenceableInvariantLoad () const |

| Return true if this load instruction never traps and points to a memory location whose value doesn't change during the execution of this function. | |

| unsigned | isConstantValuePHI () const |

| If the specified instruction is a PHI that always merges together the same virtual register, return the register, otherwise return 0. | |

| bool | hasUnmodeledSideEffects () const |

| Return true if this instruction has side effects that are not modeled by mayLoad / mayStore, etc. | |

| bool | isLoadFoldBarrier () const |

| Returns true if it is illegal to fold a load across this instruction. | |

| bool | allDefsAreDead () const |

| Return true if all the defs of this instruction are dead. | |

| bool | allImplicitDefsAreDead () const |

| Return true if all the implicit defs of this instruction are dead. | |

| std::optional< LocationSize > | getSpillSize (const TargetInstrInfo *TII) const |

| Return a valid size if the instruction is a spill instruction. | |

| std::optional< LocationSize > | getFoldedSpillSize (const TargetInstrInfo *TII) const |

| Return a valid size if the instruction is a folded spill instruction. | |

| std::optional< LocationSize > | getRestoreSize (const TargetInstrInfo *TII) const |

| Return a valid size if the instruction is a restore instruction. | |

| std::optional< LocationSize > | getFoldedRestoreSize (const TargetInstrInfo *TII) const |

| Return a valid size if the instruction is a folded restore instruction. | |

| void | copyImplicitOps (MachineFunction &MF, const MachineInstr &MI) |

| Copy implicit register operands from specified instruction to this instruction. | |

| void | addOperand (MachineFunction &MF, const MachineOperand &Op) |

| Add the specified operand to the instruction. | |

| void | addOperand (const MachineOperand &Op) |

| Add an operand without providing an MF reference. | |

| void | insert (mop_iterator InsertBefore, ArrayRef< MachineOperand > Ops) |

| Inserts Ops BEFORE It. Can untie/retie tied operands. | |

| void | setDesc (const MCInstrDesc &TID) |

| Replace the instruction descriptor (thus opcode) of the current instruction with a new one. | |

| void | setDebugLoc (DebugLoc DL) |

| Replace current source information with new such. | |

| void | removeOperand (unsigned OpNo) |

| Erase an operand from an instruction, leaving it with one fewer operand than it started with. | |

| void | dropMemRefs (MachineFunction &MF) |

| Clear this MachineInstr's memory reference descriptor list. | |

| void | setMemRefs (MachineFunction &MF, ArrayRef< MachineMemOperand * > MemRefs) |

| Assign this MachineInstr's memory reference descriptor list. | |

| void | addMemOperand (MachineFunction &MF, MachineMemOperand *MO) |

| Add a MachineMemOperand to the machine instruction. | |

| void | cloneMemRefs (MachineFunction &MF, const MachineInstr &MI) |

| Clone another MachineInstr's memory reference descriptor list and replace ours with it. | |

| void | cloneMergedMemRefs (MachineFunction &MF, ArrayRef< const MachineInstr * > MIs) |

| Clone the merge of multiple MachineInstrs' memory reference descriptors list and replace ours with it. | |

| void | setPreInstrSymbol (MachineFunction &MF, MCSymbol *Symbol) |

| Set a symbol that will be emitted just prior to the instruction itself. | |

| void | setPostInstrSymbol (MachineFunction &MF, MCSymbol *Symbol) |

| Set a symbol that will be emitted just after the instruction itself. | |

| void | cloneInstrSymbols (MachineFunction &MF, const MachineInstr &MI) |

| Clone another MachineInstr's pre- and post- instruction symbols and replace ours with it. | |

| void | setHeapAllocMarker (MachineFunction &MF, MDNode *MD) |

| Set a marker on instructions that denotes where we should create and emit heap alloc site labels. | |

| void | setPCSections (MachineFunction &MF, MDNode *MD) |

| void | setMMRAMetadata (MachineFunction &MF, MDNode *MMRAs) |

| void | setCFIType (MachineFunction &MF, uint32_t Type) |

| Set the CFI type for the instruction. | |

| uint32_t | mergeFlagsWith (const MachineInstr &Other) const |

| Return the MIFlags which represent both MachineInstrs. | |

| void | copyIRFlags (const Instruction &I) |

| Copy all flags to MachineInst MIFlags. | |

| void | untieRegOperand (unsigned OpIdx) |

| Break any tie involving OpIdx. | |

| void | addImplicitDefUseOperands (MachineFunction &MF) |

| Add all implicit def and use operands to this instruction. | |

| void | collectDebugValues (SmallVectorImpl< MachineInstr * > &DbgValues) |

| Scan instructions immediately following MI and collect any matching DBG_VALUEs. | |

| void | changeDebugValuesDefReg (Register Reg) |

Find all DBG_VALUEs that point to the register def in this instruction and point them to Reg instead. | |

| void | setDebugValueUndef () |

| Sets all register debug operands in this debug value instruction to be undef. | |

| std::tuple< Register, Register > | getFirst2Regs () const |

| std::tuple< Register, Register, Register > | getFirst3Regs () const |

| std::tuple< Register, Register, Register, Register > | getFirst4Regs () const |

| std::tuple< Register, Register, Register, Register, Register > | getFirst5Regs () const |

| std::tuple< LLT, LLT > | getFirst2LLTs () const |

| std::tuple< LLT, LLT, LLT > | getFirst3LLTs () const |

| std::tuple< LLT, LLT, LLT, LLT > | getFirst4LLTs () const |

| std::tuple< LLT, LLT, LLT, LLT, LLT > | getFirst5LLTs () const |

| std::tuple< Register, LLT, Register, LLT > | getFirst2RegLLTs () const |

| std::tuple< Register, LLT, Register, LLT, Register, LLT > | getFirst3RegLLTs () const |

| std::tuple< Register, LLT, Register, LLT, Register, LLT, Register, LLT > | getFirst4RegLLTs () const |

| std::tuple< Register, LLT, Register, LLT, Register, LLT, Register, LLT, Register, LLT > | getFirst5RegLLTs () const |

| LLT | getTypeToPrint (unsigned OpIdx, SmallBitVector &PrintedTypes, const MachineRegisterInfo &MRI) const |

| Debugging supportDetermine the generic type to be printed (if needed) on uses and defs. | |

| bool | hasComplexRegisterTies () const |

| Return true when an instruction has tied register that can't be determined by the instruction's descriptor. | |

| void | print (raw_ostream &OS, bool IsStandalone=true, bool SkipOpers=false, bool SkipDebugLoc=false, bool AddNewLine=true, const TargetInstrInfo *TII=nullptr) const |

Print this MI to OS. | |

| void | print (raw_ostream &OS, ModuleSlotTracker &MST, bool IsStandalone=true, bool SkipOpers=false, bool SkipDebugLoc=false, bool AddNewLine=true, const TargetInstrInfo *TII=nullptr) const |

| void | dump () const |

| void | dumpr (const MachineRegisterInfo &MRI, unsigned MaxDepth=UINT_MAX) const |

Print on dbgs() the current instruction and the instructions defining its operands and so on until we reach MaxDepth. | |

Public Member Functions inherited from llvm::ilist_node_with_parent< MachineInstr, MachineBasicBlock, ilist_sentinel_tracking< true > > Public Member Functions inherited from llvm::ilist_node_with_parent< MachineInstr, MachineBasicBlock, ilist_sentinel_tracking< true > > | |

| MachineInstr * | getPrevNode () |

| const MachineInstr * | getPrevNode () const |

Get the previous node, or nullptr for the list head. | |

| MachineInstr * | getNextNode () |

Get the next node, or nullptr for the list tail. | |

| const MachineInstr * | getNextNode () const |

Get the next node, or nullptr for the list tail. | |

Public Member Functions inherited from llvm::ilist_node_impl< ilist_detail::compute_node_options< T, Options... >::type > Public Member Functions inherited from llvm::ilist_node_impl< ilist_detail::compute_node_options< T, Options... >::type > | |

| self_iterator | getIterator () |

| const_self_iterator | getIterator () const |

| reverse_self_iterator | getReverseIterator () |

| const_reverse_self_iterator | getReverseIterator () const |

| bool | isSentinel () const |

| Check whether this is the sentinel node. | |

Static Public Member Functions | |

| template<typename Operand , typename Instruction > | |

| static iterator_range< filter_iterator< Operand *, std::function< bool(Operand &Op)> > > | getDebugOperandsForReg (Instruction *MI, Register Reg) |

Returns a range of all of the operands that correspond to a debug use of Reg. | |

| static uint32_t | copyFlagsFromInstruction (const Instruction &I) |

Friends | |

| struct | ilist_traits< MachineInstr > |

| struct | ilist_callback_traits< MachineBasicBlock > |

| class | MachineFunction |

Detailed Description

Representation of each machine instruction.

This class isn't a POD type, but it must have a trivial destructor. When a MachineFunction is deleted, all the contained MachineInstrs are deallocated without having their destructor called.

Definition at line 67 of file MachineInstr.h.

Member Typedef Documentation

◆ const_mop_iterator

Definition at line 666 of file MachineInstr.h.

◆ filtered_const_mop_iterator

| using llvm::MachineInstr::filtered_const_mop_iterator = filter_iterator<const_mop_iterator, bool (*)(const MachineOperand &)> |

Definition at line 740 of file MachineInstr.h.

◆ filtered_mop_iterator

| using llvm::MachineInstr::filtered_mop_iterator = filter_iterator<mop_iterator, bool (*)(const MachineOperand &)> |

Definition at line 738 of file MachineInstr.h.

◆ mmo_iterator

| using llvm::MachineInstr::mmo_iterator = ArrayRef<MachineMemOperand *>::iterator |

Definition at line 71 of file MachineInstr.h.

◆ mop_iterator

iterator/begin/end - Iterate over all operands of a machine instruction.

Definition at line 665 of file MachineInstr.h.

Member Enumeration Documentation

◆ CommentFlag

Flags to specify different kinds of comments to output in assembly code.

These flags carry semantic information not otherwise easily derivable from the IR text.

| Enumerator | |

|---|---|

| ReloadReuse | |

| NoSchedComment | |

| TAsmComments | |

Definition at line 77 of file MachineInstr.h.

◆ MICheckType

| Enumerator | |

|---|---|

| CheckDefs | |

| CheckKillDead | |

| IgnoreDefs | |

| IgnoreVRegDefs | |

Definition at line 1260 of file MachineInstr.h.

◆ MIFlag

Definition at line 83 of file MachineInstr.h.

◆ QueryType

API for querying MachineInstr properties.

They are the same as MCInstrDesc queries but they are bundle aware.

| Enumerator | |

|---|---|

| IgnoreBundle | |

| AnyInBundle | |

| AllInBundle | |

Definition at line 875 of file MachineInstr.h.

Constructor & Destructor Documentation

◆ MachineInstr()

|

delete |

◆ ~MachineInstr()

|

delete |

Member Function Documentation

◆ addImplicitDefUseOperands()

| void MachineInstr::addImplicitDefUseOperands | ( | MachineFunction & | MF | ) |

Add all implicit def and use operands to this instruction.

Definition at line 88 of file MachineInstr.cpp.

References addOperand(), llvm::MachineOperand::CreateReg(), llvm::MCInstrDesc::implicit_defs(), and llvm::MCInstrDesc::implicit_uses().

Referenced by ExpandMOVImmSExti8().

◆ addMemOperand()

| void MachineInstr::addMemOperand | ( | MachineFunction & | MF, |

| MachineMemOperand * | MO | ||

| ) |

Add a MachineMemOperand to the machine instruction.

This function should be used only occasionally. The setMemRefs function is the primary method for setting up a MachineInstr's MemRefs list.

Definition at line 379 of file MachineInstr.cpp.

References llvm::SmallVectorImpl< T >::append(), memoperands_begin(), memoperands_end(), llvm::SmallVectorTemplateBase< T, bool >::push_back(), and setMemRefs().

Referenced by llvm::TargetLoweringBase::emitPatchPoint(), foldInlineAsmMemOperand(), and llvm::TargetInstrInfo::foldMemoryOperand().

◆ addOperand() [1/2]

| void MachineInstr::addOperand | ( | const MachineOperand & | Op | ) |

Add an operand without providing an MF reference.

This only works for instructions that are inserted in a basic block.

MachineInstrBuilder and the two-argument addOperand(MF, MO) should be preferred.

Definition at line 179 of file MachineInstr.cpp.

References addOperand(), assert(), llvm::MachineBasicBlock::getParent(), getParent(), and MBB.

◆ addOperand() [2/2]

| void MachineInstr::addOperand | ( | MachineFunction & | MF, |

| const MachineOperand & | Op | ||

| ) |

Add the specified operand to the instruction.

addOperand - Add the specified operand to the instruction.

If it is an implicit operand, it is added to the end of the operand list. If it is an explicit operand it is added at the end of the explicit operand list (before the first implicit operand).

MF must be the machine function that was used to allocate this instruction.

MachineInstrBuilder provides a more convenient interface for creating instructions and adding operands.

If it is an implicit operand, it is added to the end of the operand list. If it is an explicit operand it is added at the end of the explicit operand list (before the first implicit operand).

Definition at line 202 of file MachineInstr.cpp.

References addOperand(), llvm::MachineFunction::allocateOperandArray(), assert(), llvm::MachineFunction::deallocateOperandArray(), llvm::MCOI::EARLY_CLOBBER, getNumOperands(), llvm::MCInstrDesc::getOperandConstraint(), isDebugInstr(), isInlineAsm(), llvm::MachineOperand::isReg(), isReg(), llvm::MachineOperand::isUse(), moveOperands(), MRI, llvm::MachineOperand::setIsDebug(), llvm::MachineOperand::setIsEarlyClobber(), llvm::MCOI::TIED_TO, and tieOperands().

Referenced by addImplicitDefUseOperands(), addOperand(), addRegisterDead(), addRegisterDefined(), addRegisterKilled(), llvm::X86InstrInfo::commuteInstructionImpl(), llvm::SIInstrInfo::convertToThreeAddress(), copyImplicitOps(), llvm::XCoreFrameLowering::emitEpilogue(), llvm::HexagonFrameLowering::emitPrologue(), expandSGPRCopy(), insert(), LowerCallResults(), llvm::SIInstrInfo::moveToVALUImpl(), and llvm::X86InstrInfo::replaceBranchWithTailCall().

◆ addRegisterDead()

| bool MachineInstr::addRegisterDead | ( | Register | Reg, |

| const TargetRegisterInfo * | RegInfo, | ||

| bool | AddIfNotFound = false |

||

| ) |

We have determined MI defined a register without a use.

Look for the operand that defines it and mark it as IsDead. If AddIfNotFound is true, add a implicit operand if it's not found. Returns true if the operand exists / is added.

Definition at line 2069 of file MachineInstr.cpp.

References addOperand(), llvm::SmallVectorTemplateCommon< T, typename >::back(), llvm::MachineOperand::CreateReg(), llvm::SmallVectorBase< Size_T >::empty(), findInlineAsmFlagIdx(), getNumOperands(), getOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::isDead(), llvm::MachineOperand::isDef(), isInlineAsm(), llvm::Register::isPhysical(), llvm::MachineOperand::isReg(), llvm::MCRegisterInfo::isSubRegister(), llvm::MCRegisterInfo::isSuperRegister(), llvm::MCRegAliasIterator::isValid(), llvm::SmallVectorTemplateBase< T, bool >::pop_back(), llvm::SmallVectorTemplateBase< T, bool >::push_back(), removeOperand(), and llvm::MachineOperand::setIsDead().

Referenced by llvm::Thumb1InstrInfo::copyPhysReg(), llvm::SIInstrInfo::expandPostRAPseudo(), and llvm::SystemZInstrInfo::foldMemoryOperandImpl().

◆ addRegisterDefined()

| void MachineInstr::addRegisterDefined | ( | Register | Reg, |

| const TargetRegisterInfo * | RegInfo = nullptr |

||

| ) |

We have determined MI defines a register.

Make sure there is an operand defining Reg.

Definition at line 2137 of file MachineInstr.cpp.

References addOperand(), llvm::MachineOperand::CreateReg(), findRegisterDefOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::getSubReg(), llvm::MachineOperand::isDef(), llvm::MachineOperand::isReg(), and operands().

Referenced by llvm::ARMBaseInstrInfo::copyPhysReg(), llvm::SparcInstrInfo::copyPhysReg(), copyPhysSubRegs(), and setPhysRegsDeadExcept().

◆ addRegisterKilled()

| bool MachineInstr::addRegisterKilled | ( | Register | IncomingReg, |

| const TargetRegisterInfo * | RegInfo, | ||

| bool | AddIfNotFound = false |

||

| ) |

We have determined MI kills a register.

Look for the operand that uses it and mark it as IsKill. If AddIfNotFound is true, add a implicit operand if it's not found. Returns true if the operand exists / is added.

Definition at line 1990 of file MachineInstr.cpp.

References addOperand(), llvm::SmallVectorTemplateCommon< T, typename >::back(), llvm::MachineOperand::CreateReg(), llvm::SmallVectorBase< Size_T >::empty(), findInlineAsmFlagIdx(), getNumOperands(), getOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::isDebug(), isInlineAsm(), llvm::MachineOperand::isKill(), llvm::Register::isPhysical(), llvm::MachineOperand::isReg(), isRegTiedToDefOperand(), llvm::MCRegisterInfo::isSubRegister(), llvm::MCRegisterInfo::isSuperRegister(), llvm::MachineOperand::isUndef(), llvm::MachineOperand::isUse(), llvm::MCRegAliasIterator::isValid(), llvm::SmallVectorTemplateBase< T, bool >::pop_back(), llvm::SmallVectorTemplateBase< T, bool >::push_back(), removeOperand(), and llvm::MachineOperand::setIsKill().

Referenced by llvm::ARMBaseInstrInfo::copyPhysReg(), llvm::SparcInstrInfo::copyPhysReg(), llvm::VEInstrInfo::copyPhysReg(), copyPhysSubRegs(), emitAlignedDPRCS2Restores(), emitAlignedDPRCS2Spills(), llvm::XCoreFrameLowering::emitPrologue(), and llvm::VEInstrInfo::expandPostRAPseudo().

◆ all_defs() [1/2]

|

inline |

Returns an iterator range over all operands that are (explicit or implicit) register defs.

Definition at line 745 of file MachineInstr.h.

References llvm::make_filter_range(), and operands().

Referenced by llvm::GCNDownwardRPTracker::advanceToNext(), computeLiveOuts(), and llvm::MachineFunction::salvageCopySSAImpl().

◆ all_defs() [2/2]

|

inline |

Returns an iterator range over all operands that are (explicit or implicit) register defs.

Definition at line 749 of file MachineInstr.h.

References llvm::make_filter_range(), and operands().

◆ all_uses() [1/2]

|

inline |

Returns an iterator range over all operands that are (explicit or implicit) register uses.

Definition at line 755 of file MachineInstr.h.

References llvm::make_filter_range(), and uses().

Referenced by llvm::ScheduleDAGInstrs::addSchedBarrierDeps().

◆ all_uses() [2/2]

|

inline |

Returns an iterator range over all operands that are (explicit or implicit) register uses.

Definition at line 759 of file MachineInstr.h.

References llvm::make_filter_range(), and uses().

◆ allDefsAreDead()

| bool MachineInstr::allDefsAreDead | ( | ) | const |

Return true if all the defs of this instruction are dead.

allDefsAreDead - Return true if all the defs of this instruction are dead.

Definition at line 1545 of file MachineInstr.cpp.

References llvm::MachineOperand::isDead(), llvm::MachineOperand::isReg(), llvm::MachineOperand::isUse(), and operands().

◆ allImplicitDefsAreDead()

| bool MachineInstr::allImplicitDefsAreDead | ( | ) | const |

Return true if all the implicit defs of this instruction are dead.

Definition at line 1555 of file MachineInstr.cpp.

References implicit_operands(), llvm::MachineOperand::isDead(), llvm::MachineOperand::isReg(), and llvm::MachineOperand::isUse().

◆ bundleWithPred()

| void MachineInstr::bundleWithPred | ( | ) |

Bundle this instruction with its predecessor.

This can be an unbundled instruction, or it can be the first instruction in a bundle.

Definition at line 816 of file MachineInstr.cpp.

References assert(), BundledPred, BundledSucc, llvm::ilist_node_impl< ilist_detail::compute_node_options< T, Options... >::type >::getIterator(), isBundledWithPred(), and setFlag().

Referenced by llvm::MachineFunction::cloneMachineInstrBundle().

◆ bundleWithSucc()

| void MachineInstr::bundleWithSucc | ( | ) |

Bundle this instruction with its successor.

This can be an unbundled instruction, or it can be the last instruction in a bundle.

Definition at line 825 of file MachineInstr.cpp.

References assert(), BundledPred, BundledSucc, llvm::ilist_node_impl< ilist_detail::compute_node_options< T, Options... >::type >::getIterator(), isBundledWithSucc(), and setFlag().

◆ canFoldAsLoad()

|

inline |

Return true for instructions that can be folded as memory operands in other instructions.

The most common use for this is instructions that are simple loads from memory that don't modify the loaded value in any way, but it can also be used for instructions that can be expressed as constant-pool loads, such as V_SETALLONES on x86, to allow them to be folded when it is beneficial. This should only be set on instructions that return a value in their only virtual register definition.

Definition at line 1071 of file MachineInstr.h.

References llvm::MCID::FoldableAsLoad, and hasProperty().

Referenced by llvm::TargetInstrInfo::foldMemoryOperand().

◆ changeDebugValuesDefReg()

| void MachineInstr::changeDebugValuesDefReg | ( | Register | Reg | ) |

Find all DBG_VALUEs that point to the register def in this instruction and point them to Reg instead.

Definition at line 2395 of file MachineInstr.cpp.

References getOperand(), llvm::MachineOperand::getParent(), llvm::MachineOperand::getReg(), isReg(), MRI, and llvm::SmallVectorTemplateBase< T, bool >::push_back().

◆ clearAsmPrinterFlag()

|

inline |

Clear specific AsmPrinter flags.

Definition at line 379 of file MachineInstr.h.

References assert().

◆ clearAsmPrinterFlags()

|

inline |

Clear the AsmPrinter bitvector.

Definition at line 362 of file MachineInstr.h.

◆ clearFlag()

|

inline |

clearFlag - Clear a MI flag.

Definition at line 413 of file MachineInstr.h.

References assert().

Referenced by llvm::TargetInstrInfo::reassociateOps(), unbundleFromPred(), and unbundleFromSucc().

◆ clearKillInfo()

| void MachineInstr::clearKillInfo | ( | ) |

Clears kill flags on all operands.

clearKillInfo - Clears kill flags on all operands.

Definition at line 1260 of file MachineInstr.cpp.

References llvm::MachineOperand::isReg(), llvm::MachineOperand::isUse(), operands(), and llvm::MachineOperand::setIsKill().

Referenced by llvm::LanaiInstrInfo::optimizeSelect(), llvm::ARMBaseInstrInfo::optimizeSelect(), and llvm::RISCVInstrInfo::optimizeSelect().

◆ clearRegisterDeads()

| void MachineInstr::clearRegisterDeads | ( | Register | Reg | ) |

Clear all dead flags on operands defining register Reg.

Definition at line 2121 of file MachineInstr.cpp.

References llvm::MachineOperand::getReg(), llvm::MachineOperand::isDef(), llvm::MachineOperand::isReg(), operands(), and llvm::MachineOperand::setIsDead().

Referenced by llvm::PPCInstrInfo::optimizeCmpPostRA().

◆ clearRegisterKills()

| void MachineInstr::clearRegisterKills | ( | Register | Reg, |

| const TargetRegisterInfo * | RegInfo | ||

| ) |

Clear all kill flags affecting Reg.

If RegInfo is provided, this includes all aliasing registers.

Definition at line 2056 of file MachineInstr.cpp.

References llvm::MachineOperand::getReg(), llvm::MachineOperand::isKill(), llvm::MachineOperand::isReg(), llvm::MachineOperand::isUse(), operands(), llvm::TargetRegisterInfo::regsOverlap(), and llvm::MachineOperand::setIsKill().

◆ cloneInstrSymbols()

| void MachineInstr::cloneInstrSymbols | ( | MachineFunction & | MF, |

| const MachineInstr & | MI | ||

| ) |

Clone another MachineInstr's pre- and post- instruction symbols and replace ours with it.

Definition at line 543 of file MachineInstr.cpp.

References assert(), MI, setHeapAllocMarker(), setMMRAMetadata(), setPCSections(), setPostInstrSymbol(), and setPreInstrSymbol().

Referenced by llvm::TargetInstrInfo::foldMemoryOperand().

◆ cloneMemRefs()

| void MachineInstr::cloneMemRefs | ( | MachineFunction & | MF, |

| const MachineInstr & | MI | ||

| ) |

Clone another MachineInstr's memory reference descriptor list and replace ours with it.

Note that *this may be the incoming MI!

Prefer this API whenever possible as it can avoid allocations in common cases.

Definition at line 387 of file MachineInstr.cpp.

References assert(), getHeapAllocMarker(), getMMRAMetadata(), getPCSections(), getPostInstrSymbol(), getPreInstrSymbol(), MI, and setMemRefs().

Referenced by llvm::CombinerHelper::applyCombineIndexedLoadStore(), and cloneMergedMemRefs().

◆ cloneMergedMemRefs()

| void MachineInstr::cloneMergedMemRefs | ( | MachineFunction & | MF, |

| ArrayRef< const MachineInstr * > | MIs | ||

| ) |

Clone the merge of multiple MachineInstrs' memory reference descriptors list and replace ours with it.

Note that *this may be one of the incoming MIs!

Prefer this API whenever possible as it can avoid allocations in common cases.

Definition at line 423 of file MachineInstr.cpp.

References llvm::SmallVectorImpl< T >::append(), assert(), cloneMemRefs(), dropMemRefs(), llvm::ArrayRef< T >::empty(), getMF(), hasIdenticalMMOs(), llvm::make_pointee_range(), memoperands(), memoperands_begin(), memoperands_empty(), memoperands_end(), MI, setMemRefs(), llvm::ArrayRef< T >::size(), and llvm::ArrayRef< T >::slice().

◆ collectDebugValues()

| void MachineInstr::collectDebugValues | ( | SmallVectorImpl< MachineInstr * > & | DbgValues | ) |

Scan instructions immediately following MI and collect any matching DBG_VALUEs.

Definition at line 2379 of file MachineInstr.cpp.

References MI, and llvm::SmallVectorTemplateBase< T, bool >::push_back().

Referenced by emitSelectPseudo().

◆ copyFlagsFromInstruction()

|

static |

Definition at line 565 of file MachineInstr.cpp.

References Disjoint, FmAfn, FmArcp, FmContract, FmNoInfs, FmNoNans, FmNsz, FmReassoc, FP, I, IsExact, NonNeg, NoSWrap, NoUWrap, and Unpredictable.

Referenced by copyIRFlags().

◆ copyImplicitOps()

| void MachineInstr::copyImplicitOps | ( | MachineFunction & | MF, |

| const MachineInstr & | MI | ||

| ) |

Copy implicit register operands from specified instruction to this instruction.

copyImplicitOps - Copy implicit register operands from specified instruction to this instruction.

Definition at line 1567 of file MachineInstr.cpp.

References addOperand(), llvm::drop_begin(), llvm::MachineOperand::isImplicit(), llvm::MachineOperand::isReg(), llvm::MachineOperand::isRegMask(), and MI.

◆ copyIRFlags()

| void MachineInstr::copyIRFlags | ( | const Instruction & | I | ) |

Copy all flags to MachineInst MIFlags.

Definition at line 622 of file MachineInstr.cpp.

References copyFlagsFromInstruction(), and I.

◆ debug_operands() [1/2]

|

inline |

Returns a range over all operands that are used to determine the variable location for this DBG_VALUE instruction.

Definition at line 696 of file MachineInstr.h.

References assert(), isDebugValueLike(), isNonListDebugValue(), llvm::make_range(), operands_begin(), and operands_end().

Referenced by llvm::buildDbgValueForSpill(), getDebugOperand(), getDebugOperandIndex(), getNumDebugOperands(), handleNewDebugValue(), hasDebugOperandForReg(), isDebugOperand(), isUndefDebugValue(), and setDebugValueUndef().

◆ debug_operands() [2/2]

|

inline |

Returns a range over all operands that are used to determine the variable location for this DBG_VALUE instruction.

Definition at line 703 of file MachineInstr.h.

References assert(), isDebugValueLike(), isNonListDebugValue(), llvm::make_range(), operands_begin(), and operands_end().

◆ definesRegister()

|

inline |

Return true if the MachineInstr fully defines the specified register.

If TargetRegisterInfo is non-null, then it also checks if there is a def of a super-register. NOTE: It's ignoring subreg indices on virtual registers.

Definition at line 1497 of file MachineInstr.h.

References findRegisterDefOperandIdx(), Reg, and TRI.

Referenced by checkAndUpdateCCRKill(), checkAndUpdateCPSRKill(), checkCCKill(), llvm::SystemZInstrInfo::foldMemoryOperandImpl(), isCCSelectPair(), llvm::PPCInstrInfo::optimizeCmpPostRA(), and llvm::AArch64InstrInfo::optimizeCompareInstr().

◆ defs() [1/2]

|

inline |

Returns a range over all explicit operands that are register definitions.

Implicit definition are not included!

Definition at line 711 of file MachineInstr.h.

References getNumExplicitDefs(), llvm::make_range(), and operands_begin().

Referenced by findSingleRegDef(), getSalvageOpsForTrunc(), llvm::SPIRVGlobalRegistry::getSPIRVTypeID(), isSafeToMove(), LowerCallResults(), llvm::PeelSingleBlockLoop(), llvm::MipsInstrInfo::SafeInFPUDelaySlot(), and llvm::MipsInstrInfo::SafeInLoadDelaySlot().

◆ defs() [2/2]

|

inline |

Returns a range over all explicit operands that are register definitions.

Implicit definition are not included!

Definition at line 716 of file MachineInstr.h.

References getNumExplicitDefs(), llvm::make_range(), and operands_begin().

◆ dropDebugNumber()

|

inline |

Drop any variable location debugging information associated with this instruction.

Use when an instruction is modified in such a way that it no longer defines the value it used to. Variable locations using that value will be dropped.

Definition at line 544 of file MachineInstr.h.

Referenced by llvm::X86InstrInfo::optimizeCompareInstr().

◆ dropMemRefs()

| void MachineInstr::dropMemRefs | ( | MachineFunction & | MF | ) |

Clear this MachineInstr's memory reference descriptor list.

This resets the memrefs to their most conservative state. This should be used only as a last resort since it greatly pessimizes our knowledge of the memory access performed by the instruction.

Definition at line 358 of file MachineInstr.cpp.

References getCFIType(), getHeapAllocMarker(), getMMRAMetadata(), getPCSections(), getPostInstrSymbol(), getPreInstrSymbol(), and memoperands_empty().

Referenced by cloneMergedMemRefs(), and setMemRefs().

◆ dump()

| LLVM_DUMP_METHOD void MachineInstr::dump | ( | ) | const |

Definition at line 1617 of file MachineInstr.cpp.

References llvm::dbgs(), and print().

Referenced by llvm::PPCInstrInfo::combineRLWINM(), llvm::ScheduleDAGInstrs::dumpNode(), llvm::PPCInstrInfo::foldFrameOffset(), llvm::SMSchedule::insert(), moveAndTeeForMultiUse(), MoveVPNOTBeforeFirstUser(), llvm::PPCInstrInfo::optimizeCmpPostRA(), rematerializeCheapDef(), and updateOperandRegConstraints().

◆ dumpr()

| LLVM_DUMP_METHOD void MachineInstr::dumpr | ( | const MachineRegisterInfo & | MRI, |

| unsigned | MaxDepth = UINT_MAX |

||

| ) | const |

Print on dbgs() the current instruction and the instructions defining its operands and so on until we reach MaxDepth.

Definition at line 1647 of file MachineInstr.cpp.

◆ emitError()

| void MachineInstr::emitError | ( | StringRef | Msg | ) | const |

Emit an error referring to the source location of this instruction.

This should only be used for inline assembly that is somehow impossible to compile. Other errors should have been handled much earlier.

If this method returns, the caller should try to recover from the error.

Definition at line 2195 of file MachineInstr.cpp.

References llvm::LLVMContext::emitError(), llvm::Module::getContext(), llvm::MachineFunction::getMMI(), llvm::MachineModuleInfo::getModule(), getNumOperands(), llvm::MDNode::getNumOperands(), getOperand(), llvm::MDNode::getOperand(), llvm::MachineBasicBlock::getParent(), getParent(), MBB, and llvm::report_fatal_error().

◆ eraseFromBundle()

| void MachineInstr::eraseFromBundle | ( | ) |

Unlink 'this' from its basic block and delete it.

If the instruction is part of a bundle, the other instructions in the bundle remain bundled.

Definition at line 759 of file MachineInstr.cpp.

References assert(), llvm::MachineBasicBlock::erase_instr(), and getParent().

◆ eraseFromParent()

| void MachineInstr::eraseFromParent | ( | ) |

Unlink 'this' from the containing basic block and delete it.

If this instruction is the header of a bundle, the whole bundle is erased. This function can not be used for instructions inside a bundle, use eraseFromBundle() to erase individual bundled instructions.

Definition at line 754 of file MachineInstr.cpp.

References assert(), llvm::MachineBasicBlock::erase(), and getParent().

Referenced by llvm::ARCInstrInfo::analyzeBranch(), llvm::MipsInstrInfo::analyzeBranch(), llvm::AArch64InstrInfo::analyzeBranch(), llvm::ARMBaseInstrInfo::analyzeBranch(), llvm::SparcInstrInfo::analyzeBranch(), llvm::VEInstrInfo::analyzeBranch(), llvm::CombinerHelper::applyBuildFnMO(), llvm::CombinerHelper::applyCombineDivRem(), llvm::CombinerHelper::applyCombineExtendingLoads(), llvm::CombinerHelper::applyCombineIndexedLoadStore(), llvm::CombinerHelper::applyExtendThroughPhis(), llvm::CombinerHelper::applyShiftOfShiftedLogic(), CombineCVTAToLocal(), llvm::createLibcall(), llvm::createMemLibcall(), EmitLoweredCascadedSelect(), emitSelectPseudo(), llvm::M68kInstrInfo::ExpandMOVEM(), llvm::M68kInstrInfo::ExpandMOVSZX_RR(), llvm::M68kInstrInfo::ExpandMOVX_RR(), llvm::M68kInstrInfo::ExpandPUSH_POP(), llvm::PPCInstrInfo::foldFrameOffset(), foldVGPRCopyIntoRegSequence(), llvm::HexagonInstrInfo::genAllInsnTimingClasses(), llvm::MachineSSAUpdater::GetValueInMiddleOfBlock(), llvm::SystemZELFFrameLowering::inlineStackProbe(), llvm::SystemZXPLINKFrameLowering::inlineStackProbe(), LowerCallResults(), llvm::LegalizerHelper::lowerLoad(), llvm::LegalizerHelper::lowerStore(), llvm::CombinerHelper::matchCombineExtractedVectorLoad(), llvm::CombinerHelper::matchCombineLoadWithAndMask(), llvm::SIInstrInfo::moveFlatAddrToVGPR(), llvm::SIInstrInfo::moveToVALUImpl(), llvm::AArch64InstrInfo::optimizeCompareInstr(), llvm::SIInstrInfo::optimizeCompareInstr(), llvm::ARMBaseInstrInfo::optimizeCompareInstr(), llvm::LanaiInstrInfo::optimizeCompareInstr(), llvm::X86InstrInfo::optimizeCompareInstr(), llvm::PPCInstrInfo::optimizeCompareInstr(), llvm::LanaiInstrInfo::optimizeSelect(), llvm::ARMBaseInstrInfo::optimizeSelect(), llvm::RISCVInstrInfo::optimizeSelect(), llvm::LegalizerHelper::reduceLoadStoreWidth(), RemoveDeadAddBetweenLEAAndJT(), llvm::FastISel::selectPatchpoint(), and splitMBB().

◆ explicit_operands() [1/2]

|

inline |

Definition at line 680 of file MachineInstr.h.

References getNumExplicitOperands(), llvm::make_range(), and operands_begin().

Referenced by implicit_operands(), llvm::SIInstrInfo::moveToVALUImpl(), and llvm::TargetInstrInfo::reassociateOps().

◆ explicit_operands() [2/2]

|

inline |

Definition at line 684 of file MachineInstr.h.

References getNumExplicitOperands(), llvm::make_range(), and operands_begin().

◆ explicit_uses() [1/2]

|

inline |

Definition at line 729 of file MachineInstr.h.

References getNumExplicitDefs(), getNumExplicitOperands(), llvm::make_range(), and operands_begin().

◆ explicit_uses() [2/2]

|

inline |

Definition at line 733 of file MachineInstr.h.

References getNumExplicitDefs(), getNumExplicitOperands(), llvm::make_range(), and operands_begin().

◆ findFirstPredOperandIdx()

| int MachineInstr::findFirstPredOperandIdx | ( | ) | const |

Find the index of the first operand in the operand list that is used to represent the predicate.

findFirstPredOperandIdx() - Find the index of the first operand in the operand list that is used to represent the predicate.

It returns -1 if none is found.

Definition at line 1126 of file MachineInstr.cpp.

References getDesc(), getNumOperands(), llvm::MCInstrDesc::isPredicable(), and llvm::MCInstrDesc::operands().

Referenced by llvm::ARMBaseInstrInfo::commuteInstructionImpl().

◆ findInlineAsmFlagIdx()

Find the index of the flag word operand that corresponds to operand OpIdx on an inline asm instruction.

Returns -1 if getOperand(OpIdx) does not belong to an inline asm operand group.

If GroupNo is not NULL, it will receive the number of the operand group containing OpIdx.

Definition at line 867 of file MachineInstr.cpp.

References assert(), F, llvm::MachineOperand::getImm(), getNumOperands(), getOperand(), llvm::MachineOperand::isImm(), isInlineAsm(), and llvm::InlineAsm::MIOp_FirstOperand.

Referenced by addRegisterDead(), addRegisterKilled(), and getRegClassConstraint().

◆ findRegisterDefOperand() [1/2]

|

inline |

Wrapper for findRegisterDefOperandIdx, it returns a pointer to the MachineOperand rather than an index.

Definition at line 1553 of file MachineInstr.h.

References findRegisterDefOperandIdx(), getOperand(), Idx, Reg, and TRI.

Referenced by addRegisterDefined(), findRegisterDefOperand(), llvm::SystemZInstrInfo::foldMemoryOperandImpl(), llvm::X86InstrInfo::hasReassociableOperands(), llvm::X86InstrInfo::optimizeCompareInstr(), llvm::X86InstrInfo::setSpecialOperandAttr(), and transferDeadCC().

◆ findRegisterDefOperand() [2/2]

|

inline |

Definition at line 1561 of file MachineInstr.h.

References findRegisterDefOperand(), Reg, and TRI.

◆ findRegisterDefOperandIdx()

| int MachineInstr::findRegisterDefOperandIdx | ( | Register | Reg, |

| const TargetRegisterInfo * | TRI, | ||

| bool | isDead = false, |

||

| bool | Overlap = false |

||

| ) | const |

Returns the operand index that is a def of the specified register or -1 if it is not found.

findRegisterDefOperandIdx() - Returns the operand index that is a def of the specified register or -1 if it is not found.

If isDead is true, defs that are not dead are skipped. If Overlap is true, then it also looks for defs that merely overlap the specified register. If TargetRegisterInfo is non-null, then it also checks if there is a def of a super-register. This may also return a register mask operand when Overlap is true.

If isDead is true, defs that are not dead are skipped. If TargetRegisterInfo is non-null, then it also checks if there is a def of a super-register.

Definition at line 1097 of file MachineInstr.cpp.

References llvm::MachineOperand::clobbersPhysReg(), getNumOperands(), getOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::isDead(), llvm::MachineOperand::isDef(), llvm::Register::isPhysical(), llvm::MachineOperand::isReg(), llvm::MachineOperand::isRegMask(), and TRI.

Referenced by canFoldIntoCSel(), definesRegister(), findRegisterDefOperand(), getMaddPatterns(), getMiscPatterns(), hasSameValue(), llvm::CombinerHelper::matchEqualDefs(), modifiesRegister(), llvm::SIInstrInfo::moveToVALUImpl(), llvm::AArch64InstrInfo::optimizeCompareInstr(), llvm::AArch64InstrInfo::optimizeCondBranch(), and registerDefIsDead().

◆ findRegisterUseOperand() [1/2]

|

inline |

Wrapper for findRegisterUseOperandIdx, it returns a pointer to the MachineOperand rather than an index.

Definition at line 1527 of file MachineInstr.h.

References findRegisterUseOperandIdx(), getOperand(), Idx, isKill(), Reg, and TRI.

Referenced by findRegisterUseOperand().

◆ findRegisterUseOperand() [2/2]

|

inline |

Definition at line 1534 of file MachineInstr.h.

References findRegisterUseOperand(), isKill(), Reg, and TRI.

◆ findRegisterUseOperandIdx()

| int MachineInstr::findRegisterUseOperandIdx | ( | Register | Reg, |

| const TargetRegisterInfo * | TRI, | ||

| bool | isKill = false |

||

| ) | const |

Returns the operand index that is a use of the specific register or -1 if it is not found.

findRegisterUseOperandIdx() - Returns the MachineOperand that is a use of the specific register or -1 if it is not found.

It further tightens the search criteria to a use that kills the register if isKill is true.

Definition at line 1048 of file MachineInstr.cpp.

References getNumOperands(), getOperand(), llvm::MachineOperand::getReg(), isKill(), llvm::MachineOperand::isKill(), llvm::MachineOperand::isReg(), llvm::MachineOperand::isUse(), and TRI.

Referenced by findRegisterUseOperand(), killsRegister(), readsRegister(), and llvm::salvageDebugInfoForDbgValue().

◆ findTiedOperandIdx()

Given the index of a tied register operand, find the operand it is tied to.

Defs are tied to uses and vice versa. Returns the index of the tied operand which must exist.

Definition at line 1183 of file MachineInstr.cpp.

References assert(), F, llvm::StatepointOpers::getFirstGCPtrIdx(), llvm::MachineOperand::getImm(), llvm::StackMaps::getNextMetaArgIdx(), getNumDefs(), getNumOperands(), getOpcode(), getOperand(), llvm::MachineOperand::isImm(), isInlineAsm(), llvm::MachineOperand::isReg(), isReg(), llvm::MachineOperand::isTied(), llvm::MachineOperand::isUse(), llvm_unreachable, llvm::InlineAsm::MIOp_FirstOperand, llvm::SmallVectorTemplateBase< T, bool >::push_back(), llvm::SmallVectorBase< Size_T >::size(), and TiedMax.

Referenced by hasComplexRegisterTies(), insert(), isRegTiedToDefOperand(), isRegTiedToUseOperand(), print(), and untieRegOperand().

◆ getAsmPrinterFlag()

|

inline |

Return whether an AsmPrinter flag is set.

Definition at line 365 of file MachineInstr.h.

References assert().

◆ getAsmPrinterFlags()

|

inline |

Return the asm printer flags bitvector.

Definition at line 359 of file MachineInstr.h.

◆ getBundleSize()

| unsigned MachineInstr::getBundleSize | ( | ) | const |

Return the number of instructions inside the MI bundle, excluding the bundle header.

Return the number of instructions inside the MI bundle, not counting the header instruction.

This is the number of instructions that MachineBasicBlock::iterator skips, 0 for unbundled instructions.

Definition at line 1024 of file MachineInstr.cpp.

References llvm::ilist_node_impl< ilist_detail::compute_node_options< T, Options... >::type >::getIterator(), I, and Size.

◆ getCFIType()

|

inline |

Helper to extract a CFI type hash if one has been added.

Definition at line 863 of file MachineInstr.h.

References Info.

Referenced by dropMemRefs(), isIdenticalTo(), print(), setCFIType(), setHeapAllocMarker(), setMemRefs(), setMMRAMetadata(), setPCSections(), setPostInstrSymbol(), and setPreInstrSymbol().

◆ getDebugExpression()

| const DIExpression * MachineInstr::getDebugExpression | ( | ) | const |

Return the complex address expression referenced by this DBG_VALUE instruction.

Definition at line 929 of file MachineInstr.cpp.

References getDebugExpressionOp().

Referenced by handleNewDebugValue(), isDebugEntryValue(), isEquivalentDbgInstr(), and llvm::salvageDebugInfoForDbgValue().

◆ getDebugExpressionOp() [1/2]

| MachineOperand & MachineInstr::getDebugExpressionOp | ( | ) |

Definition at line 923 of file MachineInstr.cpp.

References assert(), getOperand(), isDebugValueLike(), and isNonListDebugValue().

◆ getDebugExpressionOp() [2/2]

| const MachineOperand & MachineInstr::getDebugExpressionOp | ( | ) | const |

Return the operand for the complex address expression referenced by this DBG_VALUE instruction.

Definition at line 917 of file MachineInstr.cpp.

References assert(), getOperand(), isDebugValueLike(), and isNonListDebugValue().

Referenced by getDebugExpression(), llvm::salvageDebugInfoForDbgValue(), and llvm::updateDbgValueForSpill().

◆ getDebugInstrNum() [1/2]

| unsigned MachineInstr::getDebugInstrNum | ( | ) |

Fetch the instruction number of this MachineInstr.

If it does not have one already, a new and unique number will be assigned.

Definition at line 2475 of file MachineInstr.cpp.

References llvm::MachineFunction::getNewDebugInstrNum(), llvm::MachineBasicBlock::getParent(), and getParent().

Referenced by llvm::InstrEmitter::EmitDbgInstrRef(), and llvm::MachineFunction::salvageCopySSAImpl().

◆ getDebugInstrNum() [2/2]

| unsigned MachineInstr::getDebugInstrNum | ( | MachineFunction & | MF | ) |

Fetch instruction number of this MachineInstr – but before it's inserted into MF.

Needed for transformations that create an instruction but don't immediately insert them.

Definition at line 2481 of file MachineInstr.cpp.

References llvm::MachineFunction::getNewDebugInstrNum().

◆ getDebugLabel()

Return the debug label referenced by this DBG_LABEL instruction.

Definition at line 896 of file MachineInstr.cpp.

References assert(), getOperand(), and isDebugLabel().

◆ getDebugLoc()

Returns the debug location id of this MachineInstr.

Definition at line 487 of file MachineInstr.h.

Referenced by llvm::buildDbgValueForSpill(), llvm::WebAssemblyDebugValueManager::cloneSink(), CombineCVTAToLocal(), combineFPFusedMultiply(), llvm::constrainOperandRegClass(), llvm::ARCFrameLowering::eliminateCallFramePseudoInstr(), llvm::MSP430FrameLowering::eliminateCallFramePseudoInstr(), llvm::XCoreFrameLowering::eliminateCallFramePseudoInstr(), llvm::Thumb1FrameLowering::eliminateCallFramePseudoInstr(), llvm::AArch64InstrInfo::emitLdStWithAddr(), llvm::RISCVInstrInfo::emitLdStWithAddr(), expandLoadStackGuard(), expandMOV32r1(), llvm::M68kInstrInfo::ExpandMOVEM(), ExpandMOVImmSExti8(), llvm::M68kInstrInfo::ExpandMOVSZX_RM(), llvm::M68kInstrInfo::ExpandMOVSZX_RR(), llvm::M68kInstrInfo::ExpandMOVX_RR(), llvm::X86InstrInfo::expandPostRAPseudo(), llvm::M68kInstrInfo::ExpandPUSH_POP(), INITIALIZE_PASS(), llvm::SystemZELFFrameLowering::inlineStackProbe(), llvm::SystemZXPLINKFrameLowering::inlineStackProbe(), insertPHI(), isEquivalentDbgInstr(), isIdenticalTo(), llvm::SIInstrInfo::legalizeOperands(), llvm::SIInstrInfo::moveToVALUImpl(), print(), llvm::ARMBaseInstrInfo::reMaterialize(), llvm::X86InstrInfo::reMaterialize(), llvm::WebAssemblyDebugValueManager::sink(), splitEdge(), and splitMBB().

◆ getDebugOffset() [1/2]

|

inline |

Definition at line 496 of file MachineInstr.h.

References assert(), getOperand(), and isNonListDebugValue().

◆ getDebugOffset() [2/2]

|

inline |

Return the operand containing the offset to be used if this DBG_VALUE instruction is indirect; will be an invalid register if this value is not indirect, and an immediate with value 0 otherwise.

Definition at line 492 of file MachineInstr.h.

References assert(), getOperand(), and isNonListDebugValue().

Referenced by isDebugOffsetImm(), and llvm::updateDbgValueForSpill().

◆ getDebugOperand() [1/2]

|

inline |

Definition at line 577 of file MachineInstr.h.

References assert(), debug_operands(), and getNumDebugOperands().

Referenced by isEquivalentDbgInstr(), and isIndirectDebugValue().

◆ getDebugOperand() [2/2]

|

inline |

Definition at line 581 of file MachineInstr.h.

References assert(), debug_operands(), and getNumDebugOperands().

◆ getDebugOperandIndex()

|

inline |

Definition at line 621 of file MachineInstr.h.

References llvm::adl_begin(), assert(), debug_operands(), and isDebugOperand().

◆ getDebugOperandsForReg() [1/3]

|

inlinestatic |

Returns a range of all of the operands that correspond to a debug use of Reg.

Definition at line 599 of file MachineInstr.h.

References llvm::make_filter_range(), MI, and Reg.

Referenced by attemptDebugCopyProp(), getDebugOperandsForReg(), and llvm::updateDbgValueForSpill().

◆ getDebugOperandsForReg() [2/3]

|

inline |

Definition at line 612 of file MachineInstr.h.

References Reg.

◆ getDebugOperandsForReg() [3/3]

|

inline |

Definition at line 606 of file MachineInstr.h.

References getDebugOperandsForReg(), and Reg.

◆ getDebugVariable()

| const DILocalVariable * MachineInstr::getDebugVariable | ( | ) | const |

Return the debug variable referenced by this DBG_VALUE instruction.

Definition at line 913 of file MachineInstr.cpp.

References getDebugVariableOp().

Referenced by llvm::buildDbgValueForSpill(), isEquivalentDbgInstr(), and print().

◆ getDebugVariableOp() [1/2]

| MachineOperand & MachineInstr::getDebugVariableOp | ( | ) |

Definition at line 907 of file MachineInstr.cpp.

References assert(), getOperand(), isDebugValueLike(), and isNonListDebugValue().

◆ getDebugVariableOp() [2/2]

| const MachineOperand & MachineInstr::getDebugVariableOp | ( | ) | const |

Return the operand for the debug variable referenced by this DBG_VALUE instruction.

Definition at line 901 of file MachineInstr.cpp.

References assert(), getOperand(), isDebugValueLike(), and isNonListDebugValue().

Referenced by getDebugVariable(), and print().

◆ getDesc()

|

inline |

Returns the target instruction descriptor of this MachineInstr.

Definition at line 555 of file MachineInstr.h.