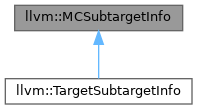

Generic base class for all target subtargets. More...

#include "llvm/MC/MCSubtargetInfo.h"

Public Member Functions | |

| MCSubtargetInfo (const MCSubtargetInfo &)=default | |

| MCSubtargetInfo (const Triple &TT, StringRef CPU, StringRef TuneCPU, StringRef FS, ArrayRef< SubtargetFeatureKV > PF, ArrayRef< SubtargetSubTypeKV > PD, const MCWriteProcResEntry *WPR, const MCWriteLatencyEntry *WL, const MCReadAdvanceEntry *RA, const InstrStage *IS, const unsigned *OC, const unsigned *FP) | |

| MCSubtargetInfo ()=delete | |

| MCSubtargetInfo & | operator= (const MCSubtargetInfo &)=delete |

| MCSubtargetInfo & | operator= (MCSubtargetInfo &&)=delete |

| virtual | ~MCSubtargetInfo ()=default |

| const Triple & | getTargetTriple () const |

| StringRef | getCPU () const |

| StringRef | getTuneCPU () const |

| const FeatureBitset & | getFeatureBits () const |

| void | setFeatureBits (const FeatureBitset &FeatureBits_) |

| StringRef | getFeatureString () const |

| bool | hasFeature (unsigned Feature) const |

| void | setDefaultFeatures (StringRef CPU, StringRef TuneCPU, StringRef FS) |

| Set the features to the default for the given CPU and TuneCPU, with ano appended feature string. | |

| FeatureBitset | ToggleFeature (uint64_t FB) |

| Toggle a feature and return the re-computed feature bits. | |

| FeatureBitset | ToggleFeature (const FeatureBitset &FB) |

| Toggle a feature and return the re-computed feature bits. | |

| FeatureBitset | ToggleFeature (StringRef FS) |

| Toggle a set of features and return the re-computed feature bits. | |

| FeatureBitset | ApplyFeatureFlag (StringRef FS) |

| Apply a feature flag and return the re-computed feature bits, including all feature bits implied by the flag. | |

| FeatureBitset | SetFeatureBitsTransitively (const FeatureBitset &FB) |

| Set/clear additional feature bits, including all other bits they imply. | |

| FeatureBitset | ClearFeatureBitsTransitively (const FeatureBitset &FB) |

| bool | checkFeatures (StringRef FS) const |

| Check whether the subtarget features are enabled/disabled as per the provided string, ignoring all other features. | |

| const MCSchedModel & | getSchedModelForCPU (StringRef CPU) const |

| Get the machine model of a CPU. | |

| const MCSchedModel & | getSchedModel () const |

| Get the machine model for this subtarget's CPU. | |

| const MCWriteProcResEntry * | getWriteProcResBegin (const MCSchedClassDesc *SC) const |

| Return an iterator at the first process resource consumed by the given scheduling class. | |

| const MCWriteProcResEntry * | getWriteProcResEnd (const MCSchedClassDesc *SC) const |

| const MCWriteLatencyEntry * | getWriteLatencyEntry (const MCSchedClassDesc *SC, unsigned DefIdx) const |

| int | getReadAdvanceCycles (const MCSchedClassDesc *SC, unsigned UseIdx, unsigned WriteResID) const |

| ArrayRef< MCReadAdvanceEntry > | getReadAdvanceEntries (const MCSchedClassDesc &SC) const |

| Return the set of ReadAdvance entries declared by the scheduling class descriptor in input. | |

| InstrItineraryData | getInstrItineraryForCPU (StringRef CPU) const |

| Get scheduling itinerary of a CPU. | |

| void | initInstrItins (InstrItineraryData &InstrItins) const |

| Initialize an InstrItineraryData instance. | |

| virtual unsigned | resolveVariantSchedClass (unsigned SchedClass, const MCInst *MI, const MCInstrInfo *MCII, unsigned CPUID) const |

| Resolve a variant scheduling class for the given MCInst and CPU. | |

| bool | isCPUStringValid (StringRef CPU) const |

| Check whether the CPU string is valid. | |

| ArrayRef< SubtargetSubTypeKV > | getAllProcessorDescriptions () const |

| Return processor descriptions. | |

| ArrayRef< SubtargetFeatureKV > | getAllProcessorFeatures () const |

| Return processor features. | |

| virtual unsigned | getHwMode () const |

| virtual std::optional< unsigned > | getCacheSize (unsigned Level) const |

| Return the cache size in bytes for the given level of cache. | |

| virtual std::optional< unsigned > | getCacheAssociativity (unsigned Level) const |

| Return the cache associatvity for the given level of cache. | |

| virtual std::optional< unsigned > | getCacheLineSize (unsigned Level) const |

| Return the target cache line size in bytes at a given level. | |

| virtual unsigned | getCacheLineSize () const |

| Return the target cache line size in bytes. | |

| virtual unsigned | getPrefetchDistance () const |

| Return the preferred prefetch distance in terms of instructions. | |

| virtual unsigned | getMaxPrefetchIterationsAhead () const |

| Return the maximum prefetch distance in terms of loop iterations. | |

| virtual bool | enableWritePrefetching () const |

| virtual unsigned | getMinPrefetchStride (unsigned NumMemAccesses, unsigned NumStridedMemAccesses, unsigned NumPrefetches, bool HasCall) const |

| Return the minimum stride necessary to trigger software prefetching. | |

| virtual bool | shouldPrefetchAddressSpace (unsigned AS) const |

Protected Member Functions | |

| void | InitMCProcessorInfo (StringRef CPU, StringRef TuneCPU, StringRef FS) |

| Initialize the scheduling model and feature bits. | |

Detailed Description

Generic base class for all target subtargets.

Definition at line 76 of file MCSubtargetInfo.h.

Constructor & Destructor Documentation

◆ MCSubtargetInfo() [1/3]

|

default |

◆ MCSubtargetInfo() [2/3]

| MCSubtargetInfo::MCSubtargetInfo | ( | const Triple & | TT, |

| StringRef | CPU, | ||

| StringRef | TuneCPU, | ||

| StringRef | FS, | ||

| ArrayRef< SubtargetFeatureKV > | PF, | ||

| ArrayRef< SubtargetSubTypeKV > | PD, | ||

| const MCWriteProcResEntry * | WPR, | ||

| const MCWriteLatencyEntry * | WL, | ||

| const MCReadAdvanceEntry * | RA, | ||

| const InstrStage * | IS, | ||

| const unsigned * | OC, | ||

| const unsigned * | FP | ||

| ) |

Definition at line 226 of file MCSubtargetInfo.cpp.

References InitMCProcessorInfo(), and string.

◆ MCSubtargetInfo() [3/3]

|

delete |

◆ ~MCSubtargetInfo()

|

virtualdefault |

Member Function Documentation

◆ ApplyFeatureFlag()

| FeatureBitset MCSubtargetInfo::ApplyFeatureFlag | ( | StringRef | FS | ) |

Apply a feature flag and return the re-computed feature bits, including all feature bits implied by the flag.

Definition at line 293 of file MCSubtargetInfo.cpp.

References ApplyFeatureFlag().

Referenced by ApplyFeatureFlag(), and checkFeatures().

◆ checkFeatures()

Check whether the subtarget features are enabled/disabled as per the provided string, ignoring all other features.

Definition at line 298 of file MCSubtargetInfo.cpp.

References llvm::All, ApplyFeatureFlag(), and F.

◆ ClearFeatureBitsTransitively()

| FeatureBitset MCSubtargetInfo::ClearFeatureBitsTransitively | ( | const FeatureBitset & | FB | ) |

Definition at line 257 of file MCSubtargetInfo.cpp.

References ClearImpliedBits(), I, llvm::FeatureBitset::reset(), and llvm::FeatureBitset::size().

◆ enableWritePrefetching()

|

virtual |

- Returns

- True if prefetching should also be done for writes.

Definition at line 361 of file MCSubtargetInfo.cpp.

Referenced by llvm::BasicTTIImplBase< T >::enableWritePrefetching().

◆ getAllProcessorDescriptions()

|

inline |

Return processor descriptions.

Definition at line 234 of file MCSubtargetInfo.h.

◆ getAllProcessorFeatures()

|

inline |

Return processor features.

Definition at line 239 of file MCSubtargetInfo.h.

◆ getCacheAssociativity()

Return the cache associatvity for the given level of cache.

Level is zero-based, so a value of zero means the first level of cache.

Definition at line 344 of file MCSubtargetInfo.cpp.

Referenced by llvm::BasicTTIImplBase< T >::getCacheAssociativity().

◆ getCacheLineSize() [1/2]

|

inlinevirtual |

Return the target cache line size in bytes.

By default, return the line size for the bottom-most level of cache. This provides a more convenient interface for the common case where all cache levels have the same line size. Return zero if there is no cache model.

Definition at line 267 of file MCSubtargetInfo.h.

References getCacheLineSize(), and Size.

Referenced by getCacheLineSize().

◆ getCacheLineSize() [2/2]

Return the target cache line size in bytes at a given level.

Definition at line 349 of file MCSubtargetInfo.cpp.

Referenced by llvm::BasicTTIImplBase< T >::getCacheLineSize().

◆ getCacheSize()

Return the cache size in bytes for the given level of cache.

Level is zero-based, so a value of zero means the first level of cache.

Definition at line 339 of file MCSubtargetInfo.cpp.

◆ getCPU()

|

inline |

Definition at line 109 of file MCSubtargetInfo.h.

Referenced by llvm::Hexagon_MC::addArchSubtarget(), llvm::createHexagonAsmBackend(), llvm::createMipsAsmBackend(), llvm::AMDGPUTargetAsmStreamer::EmitAmdhsaKernelDescriptor(), llvm::ARMTargetStreamer::emitTargetAttributes(), llvm::AMDGPU::IsaInfo::getAddressableNumSGPRs(), getArchForCPU(), llvm::Hexagon_MC::getArchSubtarget(), llvm::AMDGPU::MCKernelDescriptor::getDefaultAmdhsaKernelDescriptor(), llvm::Hexagon_MC::GetELFFlags(), llvm::AMDGPU::IsaInfo::getMaxNumSGPRs(), llvm::AMDGPU::IsaInfo::getMinNumSGPRs(), llvm::AMDGPU::getNSAMaxSize(), llvm::AMDGPU::IsaInfo::getNumExtraSGPRs(), llvm::AMDGPU::IsaInfo::getSGPRAllocGranule(), llvm::AMDGPU::IsaInfo::getTotalNumSGPRs(), llvm::AMDGPU::initDefaultAMDKernelCodeT(), llvm::HexagonMCInstrInfo::isOrderedDuplexPair(), llvm::AMDGPUInstPrinter::printSWaitCnt(), and llvm::AMDGPU::IsaInfo::AMDGPUTargetID::toString().

◆ getFeatureBits()

|

inline |

Definition at line 112 of file MCSubtargetInfo.h.

Referenced by llvm::AMDGPU::IsaInfo::AMDGPUTargetID::AMDGPUTargetID(), llvm::AVRELFStreamer::AVRELFStreamer(), llvm::CSKYTargetELFStreamer::CSKYTargetELFStreamer(), DecodeGPRPairRegisterClass(), DecodeHINTInstruction(), DecodeSETPANInstruction(), DecodeSystemPStateImm0_15Instruction(), DecodeSystemPStateImm0_1Instruction(), llvm::HexagonTargetStreamer::emitTargetAttributes(), llvm::RISCVTargetStreamer::emitTargetAttributes(), llvm::MipsTargetELFStreamer::finish(), llvm::AMDGPU::IsaInfo::getAddressableLocalMemorySize(), llvm::AMDGPU::IsaInfo::getAddressableNumSGPRs(), llvm::AMDGPU::IsaInfo::getAddressableNumVGPRs(), llvm::AMDGPU::MCKernelDescriptor::getDefaultAmdhsaKernelDescriptor(), llvm::MCInstrInfo::getDeprecatedInfo(), llvm::AMDGPU::IsaInfo::getEUsPerCU(), llvm::AMDGPU::IsaInfo::getLocalMemorySize(), llvm::AMDGPU::IsaInfo::getMaxNumSGPRs(), llvm::AMDGPU::IsaInfo::getMaxWorkGroupsPerCU(), llvm::AMDGPU::IsaInfo::getMinNumSGPRs(), llvm::AMDGPU::IsaInfo::getNumExtraSGPRs(), llvm::AMDGPU::IsaInfo::getTotalNumVGPRs(), llvm::AMDGPU::IsaInfo::getVGPRAllocGranule(), llvm::AMDGPU::IsaInfo::getVGPREncodingGranule(), llvm::AMDGPU::IsaInfo::getWavefrontSize(), llvm::AMDGPU::initDefaultAMDKernelCodeT(), llvm::ARM::isCDECoproc(), llvm::AMDGPU::isGFX12(), isValidSysReg(), matchAliasCondition(), llvm::MipsTargetELFStreamer::MipsTargetELFStreamer(), llvm::RISCVInstPrinter::printCSRSystemRegister(), llvm::ARMInstPrinter::printMSRMaskOperand(), llvm::AArch64InstPrinter::printPrefetchOp(), llvm::AArch64InstPrinter::printSysAlias(), llvm::AArch64InstPrinter::printSyspAlias(), llvm::AArch64InstPrinter::printSystemPStateField(), llvm::HexagonMCInstrInfo::requiresSlot(), llvm::RISCVAsmBackend::RISCVAsmBackend(), llvm::RISCVTargetELFStreamer::RISCVTargetELFStreamer(), llvm::CSKYAsmPrinter::runOnMachineFunction(), and XtensaAsmParser::XtensaAsmParser().

◆ getFeatureString()

|

inline |

Definition at line 117 of file MCSubtargetInfo.h.

◆ getHwMode()

|

inlinevirtual |

Definition at line 243 of file MCSubtargetInfo.h.

◆ getInstrItineraryForCPU()

| InstrItineraryData MCSubtargetInfo::getInstrItineraryForCPU | ( | StringRef | CPU | ) | const |

Get scheduling itinerary of a CPU.

Definition at line 329 of file MCSubtargetInfo.cpp.

References getSchedModelForCPU().

Referenced by getItineraryLatency().

◆ getMaxPrefetchIterationsAhead()

|

virtual |

Return the maximum prefetch distance in terms of loop iterations.

Definition at line 357 of file MCSubtargetInfo.cpp.

Referenced by llvm::BasicTTIImplBase< T >::getMaxPrefetchIterationsAhead().

◆ getMinPrefetchStride()

|

virtual |

Return the minimum stride necessary to trigger software prefetching.

Definition at line 365 of file MCSubtargetInfo.cpp.

Referenced by llvm::BasicTTIImplBase< T >::getMinPrefetchStride().

◆ getPrefetchDistance()

|

virtual |

Return the preferred prefetch distance in terms of instructions.

Definition at line 353 of file MCSubtargetInfo.cpp.

Referenced by llvm::BasicTTIImplBase< T >::getPrefetchDistance().

◆ getReadAdvanceCycles()

|

inline |

Definition at line 184 of file MCSubtargetInfo.h.

Referenced by llvm::mca::RegisterFile::addRegisterRead(), llvm::mca::RegisterFile::checkRAWHazards(), llvm::mca::RegisterFile::collectWrites(), and llvm::TargetSchedModel::computeOperandLatency().

◆ getReadAdvanceEntries()

|

inline |

Return the set of ReadAdvance entries declared by the scheduling class descriptor in input.

Definition at line 206 of file MCSubtargetInfo.h.

◆ getSchedModel()

|

inline |

Get the machine model for this subtarget's CPU.

Definition at line 163 of file MCSubtargetInfo.h.

Referenced by llvm::mca::RegisterFile::addRegisterRead(), llvm::mca::RegisterFile::checkRAWHazards(), llvm::mca::RegisterFile::collectWrites(), llvm::mca::Context::createDefaultPipeline(), llvm::mca::Context::createInOrderPipeline(), llvm::mca::InstrBuilder::createInstruction(), llvm::mca::DispatchStage::DispatchStage(), llvm::TargetSubtargetInfo::enablePostRAScheduler(), llvm::HexagonMCInstrInfo::getCVIResources(), llvm::mca::InOrderIssueStage::getIssueWidth(), getLatency(), llvm::HexagonMCInstrInfo::getOtherReservedSlots(), llvm::MCSchedModel::getReciprocalThroughput(), llvm::HexagonMCInstrInfo::getUnits(), llvm::TargetSchedModel::init(), llvm::mca::initializeUsedResources(), initInstrItins(), and llvm::mca::InstrBuilder::InstrBuilder().

◆ getSchedModelForCPU()

| const MCSchedModel & MCSubtargetInfo::getSchedModelForCPU | ( | StringRef | CPU | ) | const |

Get the machine model of a CPU.

Definition at line 310 of file MCSubtargetInfo.cpp.

References assert(), llvm::MCSchedModel::Default, llvm::errs(), Find(), llvm::is_sorted(), and llvm::SubtargetSubTypeKV::SchedModel.

Referenced by getInstrItineraryForCPU(), and InitMCProcessorInfo().

◆ getTargetTriple()

Definition at line 108 of file MCSubtargetInfo.h.

Referenced by llvm::Hexagon_MC::addArchSubtarget(), llvm::ARMAsmBackend::adjustFixupValue(), llvm::createAArch64beAsmBackend(), llvm::createAArch64leAsmBackend(), llvm::createAArch64ObjectTargetStreamer(), llvm::createAMDGPUAsmBackend(), createARMAsmBackend(), llvm::createARMObjectTargetStreamer(), createAsmBackend(), llvm::createAVRAsmBackend(), createCSKYObjectTargetStreamer(), llvm::createHexagonAsmBackend(), llvm::createLanaiAsmBackend(), llvm::createLoongArchAsmBackend(), createLoongArchObjectTargetStreamer(), llvm::createM68kAsmBackend(), llvm::createMipsAsmBackend(), llvm::createMSP430ObjectTargetStreamer(), createObjectTargetStreamer(), llvm::createPPCAsmBackend(), llvm::createRISCVAsmBackend(), createRISCVObjectTargetStreamer(), llvm::createSparcAsmBackend(), llvm::createSystemZMCAsmBackend(), llvm::createVEAsmBackend(), llvm::createX86_32AsmBackend(), llvm::createX86_64AsmBackend(), llvm::createX86ObjectTargetStreamer(), llvm::createXtensaMCAsmBackend(), llvm::AMDGPUAsmPrinter::doFinalization(), llvm::AsmPrinter::emitXRayTable(), llvm::AMDGPUTargetELFStreamer::finish(), llvm::LoongArchAsmBackend::getFixupKind(), llvm::RISCVAsmBackend::getFixupKind(), llvm::AMDGPUMCAsmInfo::getMaxInstLength(), llvm::AMDGPU::IsaInfo::getMaxWorkGroupsPerCU(), llvm::AMDGPU::getMCReg(), llvm::PPCMCCodeEmitter::getTLSRegEncoding(), llvm::AMDGPU::isHsaAbi(), llvm::LoongArchTargetELFStreamer::LoongArchTargetELFStreamer(), lowerMSASplatZExt(), llvm::MipsTargetELFStreamer::MipsTargetELFStreamer(), llvm::RISCVAsmBackend::RISCVAsmBackend(), llvm::RISCVTargetELFStreamer::RISCVTargetELFStreamer(), AMDGPUDAGToDAGISel::SelectBuildVector(), llvm::AMDGPU::IsaInfo::AMDGPUTargetID::toString(), and truncateVecElts().

◆ getTuneCPU()

|

inline |

Definition at line 110 of file MCSubtargetInfo.h.

◆ getWriteLatencyEntry()

|

inline |

Definition at line 176 of file MCSubtargetInfo.h.

References assert().

Referenced by llvm::MCSchedModel::computeInstrLatency(), llvm::TargetSchedModel::computeOperandLatency(), and getLatency().

◆ getWriteProcResBegin()

|

inline |

Return an iterator at the first process resource consumed by the given scheduling class.

Definition at line 167 of file MCSubtargetInfo.h.

Referenced by llvm::ResourceManager::calculateResMII(), llvm::TargetSchedModel::computeOutputLatency(), llvm::MCSchedModel::getReciprocalThroughput(), llvm::TargetSchedModel::getWriteProcResBegin(), getWriteProcResEnd(), and llvm::mca::initializeUsedResources().

◆ getWriteProcResEnd()

|

inline |

Definition at line 171 of file MCSubtargetInfo.h.

References getWriteProcResBegin().

Referenced by llvm::ResourceManager::calculateResMII(), llvm::TargetSchedModel::computeOutputLatency(), llvm::MCSchedModel::getReciprocalThroughput(), and llvm::TargetSchedModel::getWriteProcResEnd().

◆ hasFeature()

Definition at line 119 of file MCSubtargetInfo.h.

Referenced by llvm::ARMAsmBackend::adjustFixupValue(), llvm::AMDGPUDisassembler::AMDGPUDisassembler(), checkFeature(), clearFeature(), llvm::AMDGPUDisassembler::convertEXPInst(), llvm::AMDGPUDisassembler::convertMIMGInst(), llvm::AMDGPUDisassembler::convertSDWAInst(), llvm::LoongArchAsmBackend::createObjectTargetWriter(), llvm::AMDGPUDisassembler::decodeBoolReg(), decodeFPUV3Instruction(), DecodeGPRRegisterClass(), llvm::AMDGPUDisassembler::decodeSDWASrc(), llvm::AMDGPUDisassembler::decodeSDWAVopcDst(), llvm::ARMTargetStreamer::emitTargetAttributes(), llvm::RISCVTargetStreamer::emitTargetAttributes(), llvm::CSKYMCCodeEmitter::expandJBTF(), llvm::RISCVMatInt::generateInstSeq(), generateInstSeqImpl(), generateInstSeqLeadingZeros(), llvm::RISCVMatInt::generateTwoRegInstSeq(), getArchForCPU(), getARMLoadDeprecationInfo(), getARMStoreDeprecationInfo(), llvm::AMDGPUDisassembler::getInstruction(), llvm::RISCVMatInt::getIntMatCost(), getLit16Encoding(), getLit32Encoding(), getLit64Encoding(), llvm::AMDGPUMCAsmInfo::getMaxInstLength(), getMCRDeprecationInfo(), getMRCDeprecationInfo(), llvm::ARMAsmBackend::getRelaxedOpcode(), llvm::RISCVMCObjectFileInfo::getTextSectionAlignment(), llvm::LoongArchAsmBackend::handleAddSubRelocations(), llvm::AMDGPU::hasA16(), llvm::AMDGPUDisassembler::hasArchitectedFlatScratch(), llvm::AMDGPU::hasArchitectedFlatScratch(), llvm::AMDGPU::hasDPPSrc1SGPR(), llvm::AMDGPU::hasG16(), llvm::AMDGPU::hasGDS(), llvm::AMDGPU::hasGFX10_3Insts(), llvm::AMDGPU::hasKernargPreload(), llvm::AMDGPU::hasMAIInsts(), llvm::AMDGPU::hasMIMG_R128(), llvm::ARMAsmBackend::hasNOP(), llvm::AMDGPU::hasPackedD16(), llvm::AMDGPU::hasSRAMECC(), llvm::AMDGPU::hasVOPD(), llvm::AMDGPU::hasXNACK(), llvm::ARMElfTargetObjectFile::Initialize(), llvm::X86_MC::is16BitMemOperand(), llvm::AMDGPU::isCI(), llvm::AMDGPU::isGCN3Encoding(), llvm::AMDGPU::isGFX10(), llvm::AMDGPU::isGFX10_AEncoding(), llvm::AMDGPU::isGFX10_BEncoding(), llvm::AMDGPUDisassembler::isGFX11(), llvm::AMDGPU::isGFX11(), llvm::AMDGPUDisassembler::isGFX12(), llvm::AMDGPU::isGFX9(), llvm::AMDGPUDisassembler::isGFX90A(), llvm::AMDGPU::isGFX90A(), llvm::AMDGPU::isGFX940(), isMicroMips(), isMips32r6(), llvm::AMDGPU::isSI(), isThumb(), isV8M(), llvm::SparcInstPrinter::isV9(), llvm::AMDGPUDisassembler::isVI(), llvm::AMDGPU::isVI(), llvm::LoongArchTargetLowering::LowerFormalArguments(), llvm::CSKYAsmBackend::mayNeedRelaxation(), llvm::MSP430TargetELFStreamer::MSP430TargetELFStreamer(), llvm::X86_MC::needsAddressSizeOverride(), llvm::HexagonMCInstrInfo::packetSizeSlots(), llvm::RISCVInstPrinter::printBranchOperand(), printImmediateBFloat16(), printImmediateFP16(), llvm::AArch64InstPrinter::printInst(), llvm::PPCInstPrinter::printInst(), llvm::X86ATTInstPrinter::printInst(), llvm::X86IntelInstPrinter::printInst(), llvm::X86InstPrinterCommon::printInstFlags(), llvm::ARMInstPrinter::printMemBOption(), llvm::CSKYInstPrinter::printOperand(), llvm::RISCVInstPrinter::printStackAdj(), llvm::AArch64InstPrinter::printSysAlias(), llvm::AArch64InstPrinter::printSyspAlias(), llvm::CSKYAsmBackend::relaxInstruction(), llvm::RISCVTargetELFStreamer::RISCVTargetELFStreamer(), llvm::RISCVTargetStreamer::setFlagsFromFeatures(), llvm::LoongArchAsmBackend::shouldForceRelocation(), llvm::RISCVAsmBackend::shouldForceRelocation(), llvm::LoongArchAsmBackend::shouldInsertExtraNopBytesForCodeAlign(), llvm::RISCVAsmBackend::shouldInsertExtraNopBytesForCodeAlign(), llvm::LoongArchAsmBackend::shouldInsertFixupForCodeAlign(), llvm::RISCVAsmBackend::shouldInsertFixupForCodeAlign(), and llvm::RISCVAsmBackend::writeNopData().

◆ initInstrItins()

| void MCSubtargetInfo::initInstrItins | ( | InstrItineraryData & | InstrItins | ) | const |

Initialize an InstrItineraryData instance.

Definition at line 334 of file MCSubtargetInfo.cpp.

References getSchedModel().

Referenced by llvm::TargetSchedModel::init().

◆ InitMCProcessorInfo()

|

protected |

Initialize the scheduling model and feature bits.

FIXME: Find a way to stick this in the constructor, since it should only be called during initialization.

Definition at line 209 of file MCSubtargetInfo.cpp.

References llvm::MCSchedModel::Default, llvm::StringRef::empty(), getFeatures(), and getSchedModelForCPU().

Referenced by MCSubtargetInfo().

◆ isCPUStringValid()

Check whether the CPU string is valid.

Definition at line 228 of file MCSubtargetInfo.h.

References llvm::ArrayRef< T >::end(), and llvm::lower_bound().

◆ operator=() [1/2]

|

delete |

◆ operator=() [2/2]

|

delete |

◆ resolveVariantSchedClass()

|

inlinevirtual |

Resolve a variant scheduling class for the given MCInst and CPU.

Definition at line 220 of file MCSubtargetInfo.h.

Referenced by llvm::MCSchedModel::computeInstrLatency(), and llvm::MCSchedModel::getReciprocalThroughput().

◆ setDefaultFeatures()

Set the features to the default for the given CPU and TuneCPU, with ano appended feature string.

Definition at line 220 of file MCSubtargetInfo.cpp.

References getFeatures().

◆ setFeatureBits()

|

inline |

Definition at line 113 of file MCSubtargetInfo.h.

Referenced by llvm::CSKYAsmPrinter::runOnMachineFunction().

◆ SetFeatureBitsTransitively()

| FeatureBitset MCSubtargetInfo::SetFeatureBitsTransitively | ( | const FeatureBitset & | FB | ) |

Set/clear additional feature bits, including all other bits they imply.

Definition at line 251 of file MCSubtargetInfo.cpp.

References SetImpliedBits().

◆ shouldPrefetchAddressSpace()

- Returns

- if target want to issue a prefetch in address space

AS.

Definition at line 372 of file MCSubtargetInfo.cpp.

Referenced by llvm::BasicTTIImplBase< T >::shouldPrefetchAddressSpace().

◆ ToggleFeature() [1/3]

| FeatureBitset MCSubtargetInfo::ToggleFeature | ( | const FeatureBitset & | FB | ) |

Toggle a feature and return the re-computed feature bits.

This version does not change the implied bits.

Definition at line 246 of file MCSubtargetInfo.cpp.

◆ ToggleFeature() [2/3]

| FeatureBitset MCSubtargetInfo::ToggleFeature | ( | StringRef | FS | ) |

Toggle a set of features and return the re-computed feature bits.

This version will also change all implied bits.

Definition at line 268 of file MCSubtargetInfo.cpp.

References ClearImpliedBits(), llvm::errs(), Find(), llvm::FeatureBitArray::getAsBitset(), llvm::SubtargetFeatureKV::Implies, llvm::FeatureBitset::reset(), llvm::FeatureBitset::set(), SetImpliedBits(), llvm::SubtargetFeatures::StripFlag(), llvm::FeatureBitset::test(), and llvm::SubtargetFeatureKV::Value.

◆ ToggleFeature() [3/3]

| FeatureBitset MCSubtargetInfo::ToggleFeature | ( | uint64_t | FB | ) |

Toggle a feature and return the re-computed feature bits.

This version does not change the implied bits.

Definition at line 241 of file MCSubtargetInfo.cpp.

References llvm::FeatureBitset::flip().

Referenced by clearFeature().

The documentation for this class was generated from the following files:

- include/llvm/MC/MCSubtargetInfo.h

- lib/MC/MCSubtargetInfo.cpp