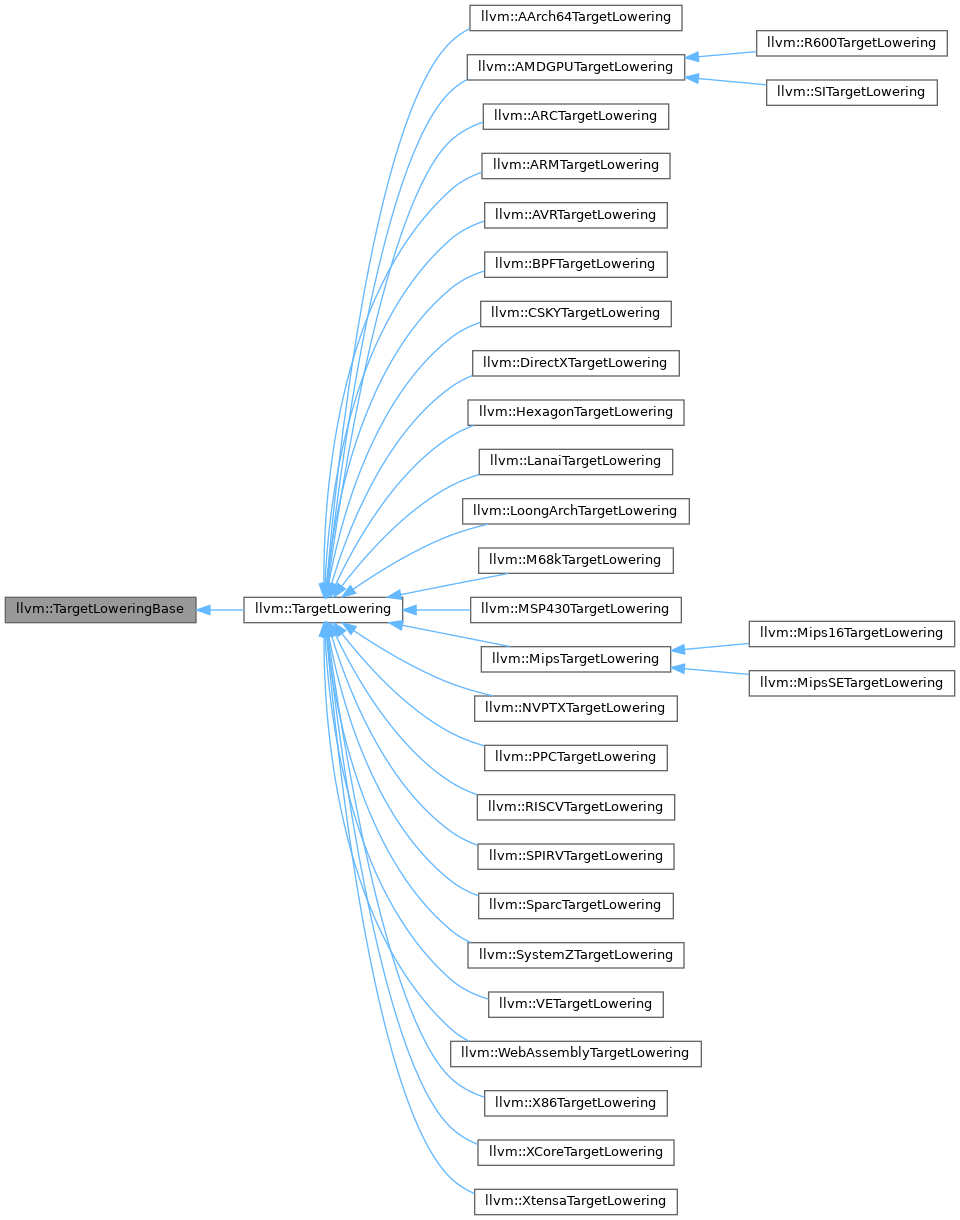

This base class for TargetLowering contains the SelectionDAG-independent parts that can be used from the rest of CodeGen. More...

#include "llvm/CodeGen/TargetLowering.h"

Classes | |

| struct | AddrMode |

| This represents an addressing mode of: BaseGV + BaseOffs + BaseReg + Scale*ScaleReg + ScalableOffset*vscale If BaseGV is null, there is no BaseGV. More... | |

| class | ArgListEntry |

| struct | CondMergingParams |

| struct | IntrinsicInfo |

| class | ValueTypeActionImpl |

Public Types | |

| enum | LegalizeAction : uint8_t { Legal , Promote , Expand , LibCall , Custom } |

| This enum indicates whether operations are valid for a target, and if not, what action should be used to make them valid. More... | |

| enum | LegalizeTypeAction : uint8_t { TypeLegal , TypePromoteInteger , TypeExpandInteger , TypeSoftenFloat , TypeExpandFloat , TypeScalarizeVector , TypeSplitVector , TypeWidenVector , TypePromoteFloat , TypeSoftPromoteHalf , TypeScalarizeScalableVector } |

| This enum indicates whether a types are legal for a target, and if not, what action should be used to make them valid. More... | |

| enum | BooleanContent { UndefinedBooleanContent , ZeroOrOneBooleanContent , ZeroOrNegativeOneBooleanContent } |

| Enum that describes how the target represents true/false values. More... | |

| enum | SelectSupportKind { ScalarValSelect , ScalarCondVectorVal , VectorMaskSelect } |

| Enum that describes what type of support for selects the target has. More... | |

| enum class | AtomicExpansionKind { None , CastToInteger , LLSC , LLOnly , CmpXChg , MaskedIntrinsic , BitTestIntrinsic , CmpArithIntrinsic , Expand , NotAtomic } |

| Enum that specifies what an atomic load/AtomicRMWInst is expanded to, if at all. More... | |

| enum class | MulExpansionKind { Always , OnlyLegalOrCustom } |

| Enum that specifies when a multiplication should be expanded. More... | |

| enum class | NegatibleCost { Cheaper = 0 , Neutral = 1 , Expensive = 2 } |

| Enum that specifies when a float negation is beneficial. More... | |

| enum | AndOrSETCCFoldKind : uint8_t { None = 0 , AddAnd = 1 , NotAnd = 2 , ABS = 4 } |

| Enum of different potentially desirable ways to fold (and/or (setcc ...), (setcc ...)). More... | |

| enum | ReciprocalEstimate : int { Unspecified = -1 , Disabled = 0 , Enabled = 1 } |

| Reciprocal estimate status values used by the functions below. More... | |

| enum class | ShiftLegalizationStrategy { ExpandToParts , ExpandThroughStack , LowerToLibcall } |

Return the preferred strategy to legalize tihs SHIFT instruction, with ExpansionFactor being the recursion depth - how many expansion needed. More... | |

| using | LegalizeKind = std::pair< LegalizeTypeAction, EVT > |

| LegalizeKind holds the legalization kind that needs to happen to EVT in order to type-legalize it. | |

| using | ArgListTy = std::vector< ArgListEntry > |

Public Member Functions | |

| virtual void | markLibCallAttributes (MachineFunction *MF, unsigned CC, ArgListTy &Args) const |

| TargetLoweringBase (const TargetMachine &TM) | |

| NOTE: The TargetMachine owns TLOF. | |

| TargetLoweringBase (const TargetLoweringBase &)=delete | |

| TargetLoweringBase & | operator= (const TargetLoweringBase &)=delete |

| virtual | ~TargetLoweringBase ()=default |

| bool | isStrictFPEnabled () const |

| Return true if the target support strict float operation. | |

| const TargetMachine & | getTargetMachine () const |

| virtual bool | useSoftFloat () const |

| virtual MVT | getPointerTy (const DataLayout &DL, uint32_t AS=0) const |

| Return the pointer type for the given address space, defaults to the pointer type from the data layout. | |

| virtual MVT | getPointerMemTy (const DataLayout &DL, uint32_t AS=0) const |

| Return the in-memory pointer type for the given address space, defaults to the pointer type from the data layout. | |

| MVT | getFrameIndexTy (const DataLayout &DL) const |

| Return the type for frame index, which is determined by the alloca address space specified through the data layout. | |

| MVT | getProgramPointerTy (const DataLayout &DL) const |

| Return the type for code pointers, which is determined by the program address space specified through the data layout. | |

| virtual MVT | getFenceOperandTy (const DataLayout &DL) const |

| Return the type for operands of fence. | |

| virtual MVT | getScalarShiftAmountTy (const DataLayout &, EVT) const |

| Return the type to use for a scalar shift opcode, given the shifted amount type. | |

| EVT | getShiftAmountTy (EVT LHSTy, const DataLayout &DL, bool LegalTypes=true) const |

| Returns the type for the shift amount of a shift opcode. | |

| virtual LLVM_READONLY LLT | getPreferredShiftAmountTy (LLT ShiftValueTy) const |

Return the preferred type to use for a shift opcode, given the shifted amount type is ShiftValueTy. | |

| virtual MVT | getVectorIdxTy (const DataLayout &DL) const |

| Returns the type to be used for the index operand of: ISD::INSERT_VECTOR_ELT, ISD::EXTRACT_VECTOR_ELT, ISD::INSERT_SUBVECTOR, and ISD::EXTRACT_SUBVECTOR. | |

| virtual MVT | getVPExplicitVectorLengthTy () const |

| Returns the type to be used for the EVL/AVL operand of VP nodes: ISD::VP_ADD, ISD::VP_SUB, etc. | |

| virtual MachineMemOperand::Flags | getTargetMMOFlags (const Instruction &I) const |

| This callback is used to inspect load/store instructions and add target-specific MachineMemOperand flags to them. | |

| virtual MachineMemOperand::Flags | getTargetMMOFlags (const MemSDNode &Node) const |

| This callback is used to inspect load/store SDNode. | |

| MachineMemOperand::Flags | getLoadMemOperandFlags (const LoadInst &LI, const DataLayout &DL, AssumptionCache *AC=nullptr, const TargetLibraryInfo *LibInfo=nullptr) const |

| MachineMemOperand::Flags | getStoreMemOperandFlags (const StoreInst &SI, const DataLayout &DL) const |

| MachineMemOperand::Flags | getAtomicMemOperandFlags (const Instruction &AI, const DataLayout &DL) const |

| virtual bool | isSelectSupported (SelectSupportKind) const |

| virtual bool | shouldExpandGetActiveLaneMask (EVT VT, EVT OpVT) const |

| Return true if the @llvm.get.active.lane.mask intrinsic should be expanded using generic code in SelectionDAGBuilder. | |

| virtual bool | shouldExpandGetVectorLength (EVT CountVT, unsigned VF, bool IsScalable) const |

| virtual bool | shouldExpandCttzElements (EVT VT) const |

| Return true if the @llvm.experimental.cttz.elts intrinsic should be expanded using generic code in SelectionDAGBuilder. | |

| virtual bool | shouldReassociateReduction (unsigned RedOpc, EVT VT) const |

| virtual bool | reduceSelectOfFPConstantLoads (EVT CmpOpVT) const |

| Return true if it is profitable to convert a select of FP constants into a constant pool load whose address depends on the select condition. | |

| bool | hasMultipleConditionRegisters () const |

| Return true if multiple condition registers are available. | |

| bool | hasExtractBitsInsn () const |

| Return true if the target has BitExtract instructions. | |

| virtual TargetLoweringBase::LegalizeTypeAction | getPreferredVectorAction (MVT VT) const |

| Return the preferred vector type legalization action. | |

| virtual bool | softPromoteHalfType () const |

| virtual bool | useFPRegsForHalfType () const |

| virtual bool | shouldExpandBuildVectorWithShuffles (EVT, unsigned DefinedValues) const |

| virtual bool | isIntDivCheap (EVT VT, AttributeList Attr) const |

| Return true if integer divide is usually cheaper than a sequence of several shifts, adds, and multiplies for this target. | |

| virtual bool | hasStandaloneRem (EVT VT) const |

| Return true if the target can handle a standalone remainder operation. | |

| virtual bool | isFsqrtCheap (SDValue X, SelectionDAG &DAG) const |

| Return true if SQRT(X) shouldn't be replaced with X*RSQRT(X). | |

| int | getRecipEstimateSqrtEnabled (EVT VT, MachineFunction &MF) const |

| Return a ReciprocalEstimate enum value for a square root of the given type based on the function's attributes. | |

| int | getRecipEstimateDivEnabled (EVT VT, MachineFunction &MF) const |

| Return a ReciprocalEstimate enum value for a division of the given type based on the function's attributes. | |

| int | getSqrtRefinementSteps (EVT VT, MachineFunction &MF) const |

| Return the refinement step count for a square root of the given type based on the function's attributes. | |

| int | getDivRefinementSteps (EVT VT, MachineFunction &MF) const |

| Return the refinement step count for a division of the given type based on the function's attributes. | |

| bool | isSlowDivBypassed () const |

| Returns true if target has indicated at least one type should be bypassed. | |

| const DenseMap< unsigned int, unsigned int > & | getBypassSlowDivWidths () const |

| Returns map of slow types for division or remainder with corresponding fast types. | |

| virtual bool | isVScaleKnownToBeAPowerOfTwo () const |

| Return true only if vscale must be a power of two. | |

| bool | isJumpExpensive () const |

| Return true if Flow Control is an expensive operation that should be avoided. | |

| virtual CondMergingParams | getJumpConditionMergingParams (Instruction::BinaryOps, const Value *, const Value *) const |

| bool | isPredictableSelectExpensive () const |

| Return true if selects are only cheaper than branches if the branch is unlikely to be predicted right. | |

| virtual bool | fallBackToDAGISel (const Instruction &Inst) const |

| virtual bool | isLoadBitCastBeneficial (EVT LoadVT, EVT BitcastVT, const SelectionDAG &DAG, const MachineMemOperand &MMO) const |

| Return true if the following transform is beneficial: fold (conv (load x)) -> (load (conv*)x) On architectures that don't natively support some vector loads efficiently, casting the load to a smaller vector of larger types and loading is more efficient, however, this can be undone by optimizations in dag combiner. | |

| virtual bool | isStoreBitCastBeneficial (EVT StoreVT, EVT BitcastVT, const SelectionDAG &DAG, const MachineMemOperand &MMO) const |

| Return true if the following transform is beneficial: (store (y (conv x)), y*)) -> (store x, (x*)) | |

| virtual bool | storeOfVectorConstantIsCheap (bool IsZero, EVT MemVT, unsigned NumElem, unsigned AddrSpace) const |

| Return true if it is expected to be cheaper to do a store of vector constant with the given size and type for the address space than to store the individual scalar element constants. | |

| virtual bool | mergeStoresAfterLegalization (EVT MemVT) const |

| Allow store merging for the specified type after legalization in addition to before legalization. | |

| virtual bool | canMergeStoresTo (unsigned AS, EVT MemVT, const MachineFunction &MF) const |

| Returns if it's reasonable to merge stores to MemVT size. | |

| virtual bool | isCheapToSpeculateCttz (Type *Ty) const |

| Return true if it is cheap to speculate a call to intrinsic cttz. | |

| virtual bool | isCheapToSpeculateCtlz (Type *Ty) const |

| Return true if it is cheap to speculate a call to intrinsic ctlz. | |

| virtual bool | isCtlzFast () const |

| Return true if ctlz instruction is fast. | |

| virtual bool | isCtpopFast (EVT VT) const |

| Return true if ctpop instruction is fast. | |

| virtual unsigned | getCustomCtpopCost (EVT VT, ISD::CondCode Cond) const |

| Return the maximum number of "x & (x - 1)" operations that can be done instead of deferring to a custom CTPOP. | |

| virtual bool | isEqualityCmpFoldedWithSignedCmp () const |

| Return true if instruction generated for equality comparison is folded with instruction generated for signed comparison. | |

| virtual bool | preferZeroCompareBranch () const |

| Return true if the heuristic to prefer icmp eq zero should be used in code gen prepare. | |

| virtual bool | isMultiStoresCheaperThanBitsMerge (EVT LTy, EVT HTy) const |

| Return true if it is cheaper to split the store of a merged int val from a pair of smaller values into multiple stores. | |

| virtual bool | isMaskAndCmp0FoldingBeneficial (const Instruction &AndI) const |

| Return if the target supports combining a chain like: | |

| virtual bool | areTwoSDNodeTargetMMOFlagsMergeable (const MemSDNode &NodeX, const MemSDNode &NodeY) const |

| Return true if it is valid to merge the TargetMMOFlags in two SDNodes. | |

| virtual bool | convertSetCCLogicToBitwiseLogic (EVT VT) const |

| Use bitwise logic to make pairs of compares more efficient. | |

| virtual MVT | hasFastEqualityCompare (unsigned NumBits) const |

| Return the preferred operand type if the target has a quick way to compare integer values of the given size. | |

| virtual bool | hasAndNotCompare (SDValue Y) const |

| Return true if the target should transform: (X & Y) == Y —> (~X & Y) == 0 (X & Y) != Y —> (~X & Y) != 0. | |

| virtual bool | hasAndNot (SDValue X) const |

| Return true if the target has a bitwise and-not operation: X = ~A & B This can be used to simplify select or other instructions. | |

| virtual bool | hasBitTest (SDValue X, SDValue Y) const |

| Return true if the target has a bit-test instruction: (X & (1 << Y)) ==/!= 0 This knowledge can be used to prevent breaking the pattern, or creating it if it could be recognized. | |

| virtual bool | shouldFoldMaskToVariableShiftPair (SDValue X) const |

| There are two ways to clear extreme bits (either low or high): Mask: x & (-1 << y) (the instcombine canonical form) Shifts: x >> y << y Return true if the variant with 2 variable shifts is preferred. | |

| virtual bool | shouldFoldConstantShiftPairToMask (const SDNode *N, CombineLevel Level) const |

| Return true if it is profitable to fold a pair of shifts into a mask. | |

| virtual bool | shouldTransformSignedTruncationCheck (EVT XVT, unsigned KeptBits) const |

| Should we tranform the IR-optimal check for whether given truncation down into KeptBits would be truncating or not: (add x, (1 << (KeptBits-1))) srccond (1 << KeptBits) Into it's more traditional form: ((x << C) a>> C) dstcond x Return true if we should transform. | |

| virtual bool | shouldProduceAndByConstByHoistingConstFromShiftsLHSOfAnd (SDValue X, ConstantSDNode *XC, ConstantSDNode *CC, SDValue Y, unsigned OldShiftOpcode, unsigned NewShiftOpcode, SelectionDAG &DAG) const |

| Given the pattern (X & (C l>>/<< Y)) ==/!= 0 return true if it should be transformed into: ((X <</l>> Y) & C) ==/!= 0 WARNING: if 'X' is a constant, the fold may deadlock! FIXME: we could avoid passing XC, but we can't use isConstOrConstSplat() here because it can end up being not linked in. | |

| virtual bool | optimizeFMulOrFDivAsShiftAddBitcast (SDNode *N, SDValue FPConst, SDValue IntPow2) const |

| virtual unsigned | preferedOpcodeForCmpEqPiecesOfOperand (EVT VT, unsigned ShiftOpc, bool MayTransformRotate, const APInt &ShiftOrRotateAmt, const std::optional< APInt > &AndMask) const |

| virtual bool | preferIncOfAddToSubOfNot (EVT VT) const |

| These two forms are equivalent: sub y, (xor x, -1) add (add x, 1), y The variant with two add's is IR-canonical. | |

| virtual bool | preferABDSToABSWithNSW (EVT VT) const |

| virtual bool | preferScalarizeSplat (SDNode *N) const |

| virtual bool | preferSextInRegOfTruncate (EVT TruncVT, EVT VT, EVT ExtVT) const |

| bool | enableExtLdPromotion () const |

| Return true if the target wants to use the optimization that turns ext(promotableInst1(...(promotableInstN(load)))) into promotedInst1(...(promotedInstN(ext(load)))). | |

| virtual bool | canCombineStoreAndExtract (Type *VectorTy, Value *Idx, unsigned &Cost) const |

| Return true if the target can combine store(extractelement VectorTy,

Idx). | |

| virtual bool | shallExtractConstSplatVectorElementToStore (Type *VectorTy, unsigned ElemSizeInBits, unsigned &Index) const |

| Return true if the target shall perform extract vector element and store given that the vector is known to be splat of constant. | |

| virtual bool | shouldSplatInsEltVarIndex (EVT) const |

| Return true if inserting a scalar into a variable element of an undef vector is more efficiently handled by splatting the scalar instead. | |

| virtual bool | enableAggressiveFMAFusion (EVT VT) const |

| Return true if target always benefits from combining into FMA for a given value type. | |

| virtual bool | enableAggressiveFMAFusion (LLT Ty) const |

| Return true if target always benefits from combining into FMA for a given value type. | |

| virtual EVT | getSetCCResultType (const DataLayout &DL, LLVMContext &Context, EVT VT) const |

| Return the ValueType of the result of SETCC operations. | |

| virtual MVT::SimpleValueType | getCmpLibcallReturnType () const |

| Return the ValueType for comparison libcalls. | |

| BooleanContent | getBooleanContents (bool isVec, bool isFloat) const |

| For targets without i1 registers, this gives the nature of the high-bits of boolean values held in types wider than i1. | |

| BooleanContent | getBooleanContents (EVT Type) const |

| SDValue | promoteTargetBoolean (SelectionDAG &DAG, SDValue Bool, EVT ValVT) const |

| Promote the given target boolean to a target boolean of the given type. | |

| Sched::Preference | getSchedulingPreference () const |

| Return target scheduling preference. | |

| virtual Sched::Preference | getSchedulingPreference (SDNode *) const |

| Some scheduler, e.g. | |

| virtual const TargetRegisterClass * | getRegClassFor (MVT VT, bool isDivergent=false) const |

| Return the register class that should be used for the specified value type. | |

| virtual bool | requiresUniformRegister (MachineFunction &MF, const Value *) const |

| Allows target to decide about the register class of the specific value that is live outside the defining block. | |

| virtual const TargetRegisterClass * | getRepRegClassFor (MVT VT) const |

| Return the 'representative' register class for the specified value type. | |

| virtual uint8_t | getRepRegClassCostFor (MVT VT) const |

| Return the cost of the 'representative' register class for the specified value type. | |

| virtual ShiftLegalizationStrategy | preferredShiftLegalizationStrategy (SelectionDAG &DAG, SDNode *N, unsigned ExpansionFactor) const |

| bool | isTypeLegal (EVT VT) const |

| Return true if the target has native support for the specified value type. | |

| const ValueTypeActionImpl & | getValueTypeActions () const |

| LegalizeKind | getTypeConversion (LLVMContext &Context, EVT VT) const |

| Return pair that represents the legalization kind (first) that needs to happen to EVT (second) in order to type-legalize it. | |

| LegalizeTypeAction | getTypeAction (LLVMContext &Context, EVT VT) const |

| Return how we should legalize values of this type, either it is already legal (return 'Legal') or we need to promote it to a larger type (return 'Promote'), or we need to expand it into multiple registers of smaller integer type (return 'Expand'). | |

| LegalizeTypeAction | getTypeAction (MVT VT) const |

| virtual EVT | getTypeToTransformTo (LLVMContext &Context, EVT VT) const |

| For types supported by the target, this is an identity function. | |

| EVT | getTypeToExpandTo (LLVMContext &Context, EVT VT) const |

| For types supported by the target, this is an identity function. | |

| unsigned | getVectorTypeBreakdown (LLVMContext &Context, EVT VT, EVT &IntermediateVT, unsigned &NumIntermediates, MVT &RegisterVT) const |

| Vector types are broken down into some number of legal first class types. | |

| virtual unsigned | getVectorTypeBreakdownForCallingConv (LLVMContext &Context, CallingConv::ID CC, EVT VT, EVT &IntermediateVT, unsigned &NumIntermediates, MVT &RegisterVT) const |

| Certain targets such as MIPS require that some types such as vectors are always broken down into scalars in some contexts. | |

| virtual bool | getTgtMemIntrinsic (IntrinsicInfo &, const CallInst &, MachineFunction &, unsigned) const |

| Given an intrinsic, checks if on the target the intrinsic will need to map to a MemIntrinsicNode (touches memory). | |

| virtual bool | isFPImmLegal (const APFloat &, EVT, bool ForCodeSize=false) const |

| Returns true if the target can instruction select the specified FP immediate natively. | |

| virtual bool | isShuffleMaskLegal (ArrayRef< int >, EVT) const |

| Targets can use this to indicate that they only support some VECTOR_SHUFFLE operations, those with specific masks. | |

| virtual bool | canOpTrap (unsigned Op, EVT VT) const |

| Returns true if the operation can trap for the value type. | |

| virtual bool | isVectorClearMaskLegal (ArrayRef< int >, EVT) const |

| Similar to isShuffleMaskLegal. | |

| virtual LegalizeAction | getCustomOperationAction (SDNode &Op) const |

| How to legalize this custom operation? | |

| LegalizeAction | getOperationAction (unsigned Op, EVT VT) const |

| Return how this operation should be treated: either it is legal, needs to be promoted to a larger size, needs to be expanded to some other code sequence, or the target has a custom expander for it. | |

| virtual bool | isSupportedFixedPointOperation (unsigned Op, EVT VT, unsigned Scale) const |

| Custom method defined by each target to indicate if an operation which may require a scale is supported natively by the target. | |

| LegalizeAction | getFixedPointOperationAction (unsigned Op, EVT VT, unsigned Scale) const |

| Some fixed point operations may be natively supported by the target but only for specific scales. | |

| LegalizeAction | getStrictFPOperationAction (unsigned Op, EVT VT) const |

| bool | isOperationLegalOrCustom (unsigned Op, EVT VT, bool LegalOnly=false) const |

| Return true if the specified operation is legal on this target or can be made legal with custom lowering. | |

| bool | isOperationLegalOrPromote (unsigned Op, EVT VT, bool LegalOnly=false) const |

| Return true if the specified operation is legal on this target or can be made legal using promotion. | |

| bool | isOperationLegalOrCustomOrPromote (unsigned Op, EVT VT, bool LegalOnly=false) const |

| Return true if the specified operation is legal on this target or can be made legal with custom lowering or using promotion. | |

| bool | isOperationCustom (unsigned Op, EVT VT) const |

| Return true if the operation uses custom lowering, regardless of whether the type is legal or not. | |

| virtual bool | areJTsAllowed (const Function *Fn) const |

| Return true if lowering to a jump table is allowed. | |

| bool | rangeFitsInWord (const APInt &Low, const APInt &High, const DataLayout &DL) const |

| Check whether the range [Low,High] fits in a machine word. | |

| virtual bool | isSuitableForJumpTable (const SwitchInst *SI, uint64_t NumCases, uint64_t Range, ProfileSummaryInfo *PSI, BlockFrequencyInfo *BFI) const |

Return true if lowering to a jump table is suitable for a set of case clusters which may contain NumCases cases, Range range of values. | |

| virtual MVT | getPreferredSwitchConditionType (LLVMContext &Context, EVT ConditionVT) const |

| Returns preferred type for switch condition. | |

| bool | isSuitableForBitTests (unsigned NumDests, unsigned NumCmps, const APInt &Low, const APInt &High, const DataLayout &DL) const |

Return true if lowering to a bit test is suitable for a set of case clusters which contains NumDests unique destinations, Low and High as its lowest and highest case values, and expects NumCmps case value comparisons. | |

| bool | isOperationExpand (unsigned Op, EVT VT) const |

| Return true if the specified operation is illegal on this target or unlikely to be made legal with custom lowering. | |

| bool | isOperationLegal (unsigned Op, EVT VT) const |

| Return true if the specified operation is legal on this target. | |

| LegalizeAction | getLoadExtAction (unsigned ExtType, EVT ValVT, EVT MemVT) const |

| Return how this load with extension should be treated: either it is legal, needs to be promoted to a larger size, needs to be expanded to some other code sequence, or the target has a custom expander for it. | |

| bool | isLoadExtLegal (unsigned ExtType, EVT ValVT, EVT MemVT) const |

| Return true if the specified load with extension is legal on this target. | |

| bool | isLoadExtLegalOrCustom (unsigned ExtType, EVT ValVT, EVT MemVT) const |

| Return true if the specified load with extension is legal or custom on this target. | |

| LegalizeAction | getAtomicLoadExtAction (unsigned ExtType, EVT ValVT, EVT MemVT) const |

| Same as getLoadExtAction, but for atomic loads. | |

| bool | isAtomicLoadExtLegal (unsigned ExtType, EVT ValVT, EVT MemVT) const |

| Return true if the specified atomic load with extension is legal on this target. | |

| LegalizeAction | getTruncStoreAction (EVT ValVT, EVT MemVT) const |

| Return how this store with truncation should be treated: either it is legal, needs to be promoted to a larger size, needs to be expanded to some other code sequence, or the target has a custom expander for it. | |

| bool | isTruncStoreLegal (EVT ValVT, EVT MemVT) const |

| Return true if the specified store with truncation is legal on this target. | |

| bool | isTruncStoreLegalOrCustom (EVT ValVT, EVT MemVT) const |

| Return true if the specified store with truncation has solution on this target. | |

| virtual bool | canCombineTruncStore (EVT ValVT, EVT MemVT, bool LegalOnly) const |

| LegalizeAction | getIndexedLoadAction (unsigned IdxMode, MVT VT) const |

| Return how the indexed load should be treated: either it is legal, needs to be promoted to a larger size, needs to be expanded to some other code sequence, or the target has a custom expander for it. | |

| bool | isIndexedLoadLegal (unsigned IdxMode, EVT VT) const |

| Return true if the specified indexed load is legal on this target. | |

| LegalizeAction | getIndexedStoreAction (unsigned IdxMode, MVT VT) const |

| Return how the indexed store should be treated: either it is legal, needs to be promoted to a larger size, needs to be expanded to some other code sequence, or the target has a custom expander for it. | |

| bool | isIndexedStoreLegal (unsigned IdxMode, EVT VT) const |

| Return true if the specified indexed load is legal on this target. | |

| LegalizeAction | getIndexedMaskedLoadAction (unsigned IdxMode, MVT VT) const |

| Return how the indexed load should be treated: either it is legal, needs to be promoted to a larger size, needs to be expanded to some other code sequence, or the target has a custom expander for it. | |

| bool | isIndexedMaskedLoadLegal (unsigned IdxMode, EVT VT) const |

| Return true if the specified indexed load is legal on this target. | |

| LegalizeAction | getIndexedMaskedStoreAction (unsigned IdxMode, MVT VT) const |

| Return how the indexed store should be treated: either it is legal, needs to be promoted to a larger size, needs to be expanded to some other code sequence, or the target has a custom expander for it. | |

| bool | isIndexedMaskedStoreLegal (unsigned IdxMode, EVT VT) const |

| Return true if the specified indexed load is legal on this target. | |

| virtual bool | shouldExtendGSIndex (EVT VT, EVT &EltTy) const |

| Returns true if the index type for a masked gather/scatter requires extending. | |

| virtual bool | shouldRemoveExtendFromGSIndex (SDValue Extend, EVT DataVT) const |

| virtual bool | isLegalScaleForGatherScatter (uint64_t Scale, uint64_t ElemSize) const |

| LegalizeAction | getCondCodeAction (ISD::CondCode CC, MVT VT) const |

| Return how the condition code should be treated: either it is legal, needs to be expanded to some other code sequence, or the target has a custom expander for it. | |

| bool | isCondCodeLegal (ISD::CondCode CC, MVT VT) const |

| Return true if the specified condition code is legal on this target. | |

| bool | isCondCodeLegalOrCustom (ISD::CondCode CC, MVT VT) const |

| Return true if the specified condition code is legal or custom on this target. | |

| MVT | getTypeToPromoteTo (unsigned Op, MVT VT) const |

| If the action for this operation is to promote, this method returns the ValueType to promote to. | |

| virtual EVT | getAsmOperandValueType (const DataLayout &DL, Type *Ty, bool AllowUnknown=false) const |

| EVT | getValueType (const DataLayout &DL, Type *Ty, bool AllowUnknown=false) const |

| Return the EVT corresponding to this LLVM type. | |

| EVT | getMemValueType (const DataLayout &DL, Type *Ty, bool AllowUnknown=false) const |

| MVT | getSimpleValueType (const DataLayout &DL, Type *Ty, bool AllowUnknown=false) const |

| Return the MVT corresponding to this LLVM type. See getValueType. | |

| virtual uint64_t | getByValTypeAlignment (Type *Ty, const DataLayout &DL) const |

| Return the desired alignment for ByVal or InAlloca aggregate function arguments in the caller parameter area. | |

| MVT | getRegisterType (MVT VT) const |

| Return the type of registers that this ValueType will eventually require. | |

| MVT | getRegisterType (LLVMContext &Context, EVT VT) const |

| Return the type of registers that this ValueType will eventually require. | |

| virtual unsigned | getNumRegisters (LLVMContext &Context, EVT VT, std::optional< MVT > RegisterVT=std::nullopt) const |

| Return the number of registers that this ValueType will eventually require. | |

| virtual MVT | getRegisterTypeForCallingConv (LLVMContext &Context, CallingConv::ID CC, EVT VT) const |

| Certain combinations of ABIs, Targets and features require that types are legal for some operations and not for other operations. | |

| virtual unsigned | getNumRegistersForCallingConv (LLVMContext &Context, CallingConv::ID CC, EVT VT) const |

| Certain targets require unusual breakdowns of certain types. | |

| virtual Align | getABIAlignmentForCallingConv (Type *ArgTy, const DataLayout &DL) const |

| Certain targets have context sensitive alignment requirements, where one type has the alignment requirement of another type. | |

| virtual bool | ShouldShrinkFPConstant (EVT) const |

| If true, then instruction selection should seek to shrink the FP constant of the specified type to a smaller type in order to save space and / or reduce runtime. | |

| virtual bool | shouldReduceLoadWidth (SDNode *Load, ISD::LoadExtType ExtTy, EVT NewVT) const |

| Return true if it is profitable to reduce a load to a smaller type. | |

| virtual bool | shouldRemoveRedundantExtend (SDValue Op) const |

| Return true (the default) if it is profitable to remove a sext_inreg(x) where the sext is redundant, and use x directly. | |

| bool | isPaddedAtMostSignificantBitsWhenStored (EVT VT) const |

| Indicates if any padding is guaranteed to go at the most significant bits when storing the type to memory and the type size isn't equal to the store size. | |

| bool | hasBigEndianPartOrdering (EVT VT, const DataLayout &DL) const |

| When splitting a value of the specified type into parts, does the Lo or Hi part come first? This usually follows the endianness, except for ppcf128, where the Hi part always comes first. | |

| bool | hasTargetDAGCombine (ISD::NodeType NT) const |

| If true, the target has custom DAG combine transformations that it can perform for the specified node. | |

| unsigned | getGatherAllAliasesMaxDepth () const |

| virtual unsigned | getVaListSizeInBits (const DataLayout &DL) const |

| Returns the size of the platform's va_list object. | |

| unsigned | getMaxStoresPerMemset (bool OptSize) const |

| Get maximum # of store operations permitted for llvm.memset. | |

| unsigned | getMaxStoresPerMemcpy (bool OptSize) const |

| Get maximum # of store operations permitted for llvm.memcpy. | |

| virtual unsigned | getMaxGluedStoresPerMemcpy () const |

| Get maximum # of store operations to be glued together. | |

| unsigned | getMaxExpandSizeMemcmp (bool OptSize) const |

| Get maximum # of load operations permitted for memcmp. | |

| unsigned | getMaxStoresPerMemmove (bool OptSize) const |

| Get maximum # of store operations permitted for llvm.memmove. | |

| virtual bool | allowsMisalignedMemoryAccesses (EVT, unsigned AddrSpace=0, Align Alignment=Align(1), MachineMemOperand::Flags Flags=MachineMemOperand::MONone, unsigned *=nullptr) const |

| Determine if the target supports unaligned memory accesses. | |

| virtual bool | allowsMisalignedMemoryAccesses (LLT, unsigned AddrSpace=0, Align Alignment=Align(1), MachineMemOperand::Flags Flags=MachineMemOperand::MONone, unsigned *=nullptr) const |

| LLT handling variant. | |

| bool | allowsMemoryAccessForAlignment (LLVMContext &Context, const DataLayout &DL, EVT VT, unsigned AddrSpace=0, Align Alignment=Align(1), MachineMemOperand::Flags Flags=MachineMemOperand::MONone, unsigned *Fast=nullptr) const |

| This function returns true if the memory access is aligned or if the target allows this specific unaligned memory access. | |

| bool | allowsMemoryAccessForAlignment (LLVMContext &Context, const DataLayout &DL, EVT VT, const MachineMemOperand &MMO, unsigned *Fast=nullptr) const |

| Return true if the memory access of this type is aligned or if the target allows this specific unaligned access for the given MachineMemOperand. | |

| virtual bool | allowsMemoryAccess (LLVMContext &Context, const DataLayout &DL, EVT VT, unsigned AddrSpace=0, Align Alignment=Align(1), MachineMemOperand::Flags Flags=MachineMemOperand::MONone, unsigned *Fast=nullptr) const |

| Return true if the target supports a memory access of this type for the given address space and alignment. | |

| bool | allowsMemoryAccess (LLVMContext &Context, const DataLayout &DL, EVT VT, const MachineMemOperand &MMO, unsigned *Fast=nullptr) const |

| Return true if the target supports a memory access of this type for the given MachineMemOperand. | |

| bool | allowsMemoryAccess (LLVMContext &Context, const DataLayout &DL, LLT Ty, const MachineMemOperand &MMO, unsigned *Fast=nullptr) const |

| LLT handling variant. | |

| virtual EVT | getOptimalMemOpType (const MemOp &Op, const AttributeList &) const |

| Returns the target specific optimal type for load and store operations as a result of memset, memcpy, and memmove lowering. | |

| virtual LLT | getOptimalMemOpLLT (const MemOp &Op, const AttributeList &) const |

| LLT returning variant. | |

| virtual bool | isSafeMemOpType (MVT) const |

| Returns true if it's safe to use load / store of the specified type to expand memcpy / memset inline. | |

| virtual unsigned | getMinimumJumpTableEntries () const |

| Return lower limit for number of blocks in a jump table. | |

| unsigned | getMinimumJumpTableDensity (bool OptForSize) const |

| Return lower limit of the density in a jump table. | |

| unsigned | getMaximumJumpTableSize () const |

| Return upper limit for number of entries in a jump table. | |

| virtual bool | isJumpTableRelative () const |

| Register | getStackPointerRegisterToSaveRestore () const |

| If a physical register, this specifies the register that llvm.savestack/llvm.restorestack should save and restore. | |

| virtual Register | getExceptionPointerRegister (const Constant *PersonalityFn) const |

| If a physical register, this returns the register that receives the exception address on entry to an EH pad. | |

| virtual Register | getExceptionSelectorRegister (const Constant *PersonalityFn) const |

| If a physical register, this returns the register that receives the exception typeid on entry to a landing pad. | |

| virtual bool | needsFixedCatchObjects () const |

| Align | getMinStackArgumentAlignment () const |

| Return the minimum stack alignment of an argument. | |

| Align | getMinFunctionAlignment () const |

| Return the minimum function alignment. | |

| Align | getPrefFunctionAlignment () const |

| Return the preferred function alignment. | |

| virtual Align | getPrefLoopAlignment (MachineLoop *ML=nullptr) const |

| Return the preferred loop alignment. | |

| virtual unsigned | getMaxPermittedBytesForAlignment (MachineBasicBlock *MBB) const |

| Return the maximum amount of bytes allowed to be emitted when padding for alignment. | |

| virtual bool | alignLoopsWithOptSize () const |

| Should loops be aligned even when the function is marked OptSize (but not MinSize). | |

| virtual Value * | getIRStackGuard (IRBuilderBase &IRB) const |

| If the target has a standard location for the stack protector guard, returns the address of that location. | |

| virtual void | insertSSPDeclarations (Module &M) const |

| Inserts necessary declarations for SSP (stack protection) purpose. | |

| virtual Value * | getSDagStackGuard (const Module &M) const |

| Return the variable that's previously inserted by insertSSPDeclarations, if any, otherwise return nullptr. | |

| virtual bool | useStackGuardXorFP () const |

| If this function returns true, stack protection checks should XOR the frame pointer (or whichever pointer is used to address locals) into the stack guard value before checking it. | |

| virtual Function * | getSSPStackGuardCheck (const Module &M) const |

| If the target has a standard stack protection check function that performs validation and error handling, returns the function. | |

| virtual Value * | getSafeStackPointerLocation (IRBuilderBase &IRB) const |

| Returns the target-specific address of the unsafe stack pointer. | |

| virtual bool | hasStackProbeSymbol (const MachineFunction &MF) const |

| Returns the name of the symbol used to emit stack probes or the empty string if not applicable. | |

| virtual bool | hasInlineStackProbe (const MachineFunction &MF) const |

| virtual StringRef | getStackProbeSymbolName (const MachineFunction &MF) const |

| virtual bool | isFreeAddrSpaceCast (unsigned SrcAS, unsigned DestAS) const |

| Returns true if a cast from SrcAS to DestAS is "cheap", such that e.g. | |

| virtual bool | shouldAlignPointerArgs (CallInst *, unsigned &, Align &) const |

| Return true if the pointer arguments to CI should be aligned by aligning the object whose address is being passed. | |

| virtual void | emitAtomicCmpXchgNoStoreLLBalance (IRBuilderBase &Builder) const |

| virtual bool | shouldSignExtendTypeInLibCall (EVT Type, bool IsSigned) const |

| Returns true if arguments should be sign-extended in lib calls. | |

| virtual bool | shouldExtendTypeInLibCall (EVT Type) const |

| Returns true if arguments should be extended in lib calls. | |

| virtual AtomicExpansionKind | shouldExpandAtomicLoadInIR (LoadInst *LI) const |

| Returns how the given (atomic) load should be expanded by the IR-level AtomicExpand pass. | |

| virtual AtomicExpansionKind | shouldCastAtomicLoadInIR (LoadInst *LI) const |

| Returns how the given (atomic) load should be cast by the IR-level AtomicExpand pass. | |

| virtual AtomicExpansionKind | shouldExpandAtomicStoreInIR (StoreInst *SI) const |

| Returns how the given (atomic) store should be expanded by the IR-level AtomicExpand pass into. | |

| virtual AtomicExpansionKind | shouldCastAtomicStoreInIR (StoreInst *SI) const |

| Returns how the given (atomic) store should be cast by the IR-level AtomicExpand pass into. | |

| virtual AtomicExpansionKind | shouldExpandAtomicCmpXchgInIR (AtomicCmpXchgInst *AI) const |

| Returns how the given atomic cmpxchg should be expanded by the IR-level AtomicExpand pass. | |

| virtual AtomicExpansionKind | shouldExpandAtomicRMWInIR (AtomicRMWInst *RMW) const |

| Returns how the IR-level AtomicExpand pass should expand the given AtomicRMW, if at all. | |

| virtual AtomicExpansionKind | shouldCastAtomicRMWIInIR (AtomicRMWInst *RMWI) const |

| Returns how the given atomic atomicrmw should be cast by the IR-level AtomicExpand pass. | |

| virtual LoadInst * | lowerIdempotentRMWIntoFencedLoad (AtomicRMWInst *RMWI) const |

| On some platforms, an AtomicRMW that never actually modifies the value (such as fetch_add of 0) can be turned into a fence followed by an atomic load. | |

| virtual ISD::NodeType | getExtendForAtomicOps () const |

| Returns how the platform's atomic operations are extended (ZERO_EXTEND, SIGN_EXTEND, or ANY_EXTEND). | |

| virtual ISD::NodeType | getExtendForAtomicCmpSwapArg () const |

| Returns how the platform's atomic compare and swap expects its comparison value to be extended (ZERO_EXTEND, SIGN_EXTEND, or ANY_EXTEND). | |

| virtual bool | shouldNormalizeToSelectSequence (LLVMContext &Context, EVT VT) const |

| Returns true if we should normalize select(N0&N1, X, Y) => select(N0, select(N1, X, Y), Y) and select(N0|N1, X, Y) => select(N0, select(N1, X, Y, Y)) if it is likely that it saves us from materializing N0 and N1 in an integer register. | |

| virtual bool | isProfitableToCombineMinNumMaxNum (EVT VT) const |

| virtual bool | convertSelectOfConstantsToMath (EVT VT) const |

| Return true if a select of constants (select Cond, C1, C2) should be transformed into simple math ops with the condition value. | |

| virtual bool | decomposeMulByConstant (LLVMContext &Context, EVT VT, SDValue C) const |

| Return true if it is profitable to transform an integer multiplication-by-constant into simpler operations like shifts and adds. | |

| virtual bool | isMulAddWithConstProfitable (SDValue AddNode, SDValue ConstNode) const |

| Return true if it may be profitable to transform (mul (add x, c1), c2) -> (add (mul x, c2), c1*c2). | |

| virtual bool | shouldUseStrictFP_TO_INT (EVT FpVT, EVT IntVT, bool IsSigned) const |

| Return true if it is more correct/profitable to use strict FP_TO_INT conversion operations - canonicalizing the FP source value instead of converting all cases and then selecting based on value. | |

| bool | isBeneficialToExpandPowI (int64_t Exponent, bool OptForSize) const |

| Return true if it is beneficial to expand an @llvm.powi. | |

| virtual bool | getAddrModeArguments (IntrinsicInst *, SmallVectorImpl< Value * > &, Type *&) const |

| CodeGenPrepare sinks address calculations into the same BB as Load/Store instructions reading the address. | |

| virtual bool | isLegalAddressingMode (const DataLayout &DL, const AddrMode &AM, Type *Ty, unsigned AddrSpace, Instruction *I=nullptr) const |

| Return true if the addressing mode represented by AM is legal for this target, for a load/store of the specified type. | |

| virtual bool | addressingModeSupportsTLS (const GlobalValue &) const |

| Returns true if the targets addressing mode can target thread local storage (TLS). | |

| virtual int64_t | getPreferredLargeGEPBaseOffset (int64_t MinOffset, int64_t MaxOffset) const |

| Return the prefered common base offset. | |

| virtual bool | isLegalICmpImmediate (int64_t) const |

| Return true if the specified immediate is legal icmp immediate, that is the target has icmp instructions which can compare a register against the immediate without having to materialize the immediate into a register. | |

| virtual bool | isLegalAddImmediate (int64_t) const |

| Return true if the specified immediate is legal add immediate, that is the target has add instructions which can add a register with the immediate without having to materialize the immediate into a register. | |

| virtual bool | isLegalAddScalableImmediate (int64_t) const |

| Return true if adding the specified scalable immediate is legal, that is the target has add instructions which can add a register with the immediate (multiplied by vscale) without having to materialize the immediate into a register. | |

| virtual bool | isLegalStoreImmediate (int64_t Value) const |

| Return true if the specified immediate is legal for the value input of a store instruction. | |

| virtual bool | isVectorShiftByScalarCheap (Type *Ty) const |

| Return true if it's significantly cheaper to shift a vector by a uniform scalar than by an amount which will vary across each lane. | |

| virtual Type * | shouldConvertSplatType (ShuffleVectorInst *SVI) const |

| Given a shuffle vector SVI representing a vector splat, return a new scalar type of size equal to SVI's scalar type if the new type is more profitable. | |

| virtual bool | shouldConvertPhiType (Type *From, Type *To) const |

| Given a set in interconnected phis of type 'From' that are loaded/stored or bitcast to type 'To', return true if the set should be converted to 'To'. | |

| virtual bool | isCommutativeBinOp (unsigned Opcode) const |

| Returns true if the opcode is a commutative binary operation. | |

| virtual bool | isBinOp (unsigned Opcode) const |

| Return true if the node is a math/logic binary operator. | |

| virtual bool | isTruncateFree (Type *FromTy, Type *ToTy) const |

| Return true if it's free to truncate a value of type FromTy to type ToTy. | |

| virtual bool | allowTruncateForTailCall (Type *FromTy, Type *ToTy) const |

| Return true if a truncation from FromTy to ToTy is permitted when deciding whether a call is in tail position. | |

| virtual bool | isTruncateFree (EVT FromVT, EVT ToVT) const |

| virtual bool | isTruncateFree (LLT FromTy, LLT ToTy, const DataLayout &DL, LLVMContext &Ctx) const |

| virtual bool | isTruncateFree (SDValue Val, EVT VT2) const |

| Return true if truncating the specific node Val to type VT2 is free. | |

| virtual bool | isProfitableToHoist (Instruction *I) const |

| bool | isExtFree (const Instruction *I) const |

Return true if the extension represented by I is free. | |

| bool | isExtLoad (const LoadInst *Load, const Instruction *Ext, const DataLayout &DL) const |

Return true if Load and Ext can form an ExtLoad. | |

| virtual bool | isZExtFree (Type *FromTy, Type *ToTy) const |

| Return true if any actual instruction that defines a value of type FromTy implicitly zero-extends the value to ToTy in the result register. | |

| virtual bool | isZExtFree (EVT FromTy, EVT ToTy) const |

| virtual bool | isZExtFree (LLT FromTy, LLT ToTy, const DataLayout &DL, LLVMContext &Ctx) const |

| virtual bool | isZExtFree (SDValue Val, EVT VT2) const |

| Return true if zero-extending the specific node Val to type VT2 is free (either because it's implicitly zero-extended such as ARM ldrb / ldrh or because it's folded such as X86 zero-extending loads). | |

| virtual bool | isSExtCheaperThanZExt (EVT FromTy, EVT ToTy) const |

| Return true if sign-extension from FromTy to ToTy is cheaper than zero-extension. | |

| virtual bool | signExtendConstant (const ConstantInt *C) const |

| Return true if this constant should be sign extended when promoting to a larger type. | |

| virtual bool | shouldSinkOperands (Instruction *I, SmallVectorImpl< Use * > &Ops) const |

| Return true if sinking I's operands to the same basic block as I is profitable, e.g. | |

| virtual bool | optimizeExtendOrTruncateConversion (Instruction *I, Loop *L, const TargetTransformInfo &TTI) const |

| Try to optimize extending or truncating conversion instructions (like zext, trunc, fptoui, uitofp) for the target. | |

| virtual bool | hasPairedLoad (EVT, Align &) const |

| Return true if the target supplies and combines to a paired load two loaded values of type LoadedType next to each other in memory. | |

| virtual bool | hasVectorBlend () const |

| Return true if the target has a vector blend instruction. | |

| virtual unsigned | getMaxSupportedInterleaveFactor () const |

| Get the maximum supported factor for interleaved memory accesses. | |

| virtual bool | lowerInterleavedLoad (LoadInst *LI, ArrayRef< ShuffleVectorInst * > Shuffles, ArrayRef< unsigned > Indices, unsigned Factor) const |

| Lower an interleaved load to target specific intrinsics. | |

| virtual bool | lowerInterleavedStore (StoreInst *SI, ShuffleVectorInst *SVI, unsigned Factor) const |

| Lower an interleaved store to target specific intrinsics. | |

| virtual bool | lowerDeinterleaveIntrinsicToLoad (IntrinsicInst *DI, LoadInst *LI) const |

| Lower a deinterleave intrinsic to a target specific load intrinsic. | |

| virtual bool | lowerInterleaveIntrinsicToStore (IntrinsicInst *II, StoreInst *SI) const |

| Lower an interleave intrinsic to a target specific store intrinsic. | |

| virtual bool | isFPExtFree (EVT DestVT, EVT SrcVT) const |

| Return true if an fpext operation is free (for instance, because single-precision floating-point numbers are implicitly extended to double-precision). | |

| virtual bool | isFPExtFoldable (const MachineInstr &MI, unsigned Opcode, LLT DestTy, LLT SrcTy) const |

Return true if an fpext operation input to an Opcode operation is free (for instance, because half-precision floating-point numbers are implicitly extended to float-precision) for an FMA instruction. | |

| virtual bool | isFPExtFoldable (const SelectionDAG &DAG, unsigned Opcode, EVT DestVT, EVT SrcVT) const |

Return true if an fpext operation input to an Opcode operation is free (for instance, because half-precision floating-point numbers are implicitly extended to float-precision) for an FMA instruction. | |

| virtual bool | isVectorLoadExtDesirable (SDValue ExtVal) const |

| Return true if folding a vector load into ExtVal (a sign, zero, or any extend node) is profitable. | |

| virtual bool | isFNegFree (EVT VT) const |

| Return true if an fneg operation is free to the point where it is never worthwhile to replace it with a bitwise operation. | |

| virtual bool | isFAbsFree (EVT VT) const |

| Return true if an fabs operation is free to the point where it is never worthwhile to replace it with a bitwise operation. | |

| virtual bool | isFMAFasterThanFMulAndFAdd (const MachineFunction &MF, EVT) const |

| Return true if an FMA operation is faster than a pair of fmul and fadd instructions. | |

| virtual bool | isFMAFasterThanFMulAndFAdd (const MachineFunction &MF, LLT) const |

| Return true if an FMA operation is faster than a pair of fmul and fadd instructions. | |

| virtual bool | isFMAFasterThanFMulAndFAdd (const Function &F, Type *) const |

| IR version. | |

| virtual bool | isFMADLegal (const MachineInstr &MI, LLT Ty) const |

Returns true if MI can be combined with another instruction to form TargetOpcode::G_FMAD. | |

| virtual bool | isFMADLegal (const SelectionDAG &DAG, const SDNode *N) const |

| Returns true if be combined with to form an ISD::FMAD. | |

| virtual bool | generateFMAsInMachineCombiner (EVT VT, CodeGenOptLevel OptLevel) const |

| virtual bool | isNarrowingProfitable (EVT SrcVT, EVT DestVT) const |

| Return true if it's profitable to narrow operations of type SrcVT to DestVT. | |

| virtual bool | shouldFoldSelectWithIdentityConstant (unsigned BinOpcode, EVT VT) const |

| Return true if pulling a binary operation into a select with an identity constant is profitable. | |

| virtual bool | shouldConvertConstantLoadToIntImm (const APInt &Imm, Type *Ty) const |

| Return true if it is beneficial to convert a load of a constant to just the constant itself. | |

| virtual bool | isExtractSubvectorCheap (EVT ResVT, EVT SrcVT, unsigned Index) const |

| Return true if EXTRACT_SUBVECTOR is cheap for extracting this result type from this source type with this index. | |

| virtual bool | shouldScalarizeBinop (SDValue VecOp) const |

| Try to convert an extract element of a vector binary operation into an extract element followed by a scalar operation. | |

| virtual bool | isExtractVecEltCheap (EVT VT, unsigned Index) const |

| Return true if extraction of a scalar element from the given vector type at the given index is cheap. | |

| virtual bool | shouldFormOverflowOp (unsigned Opcode, EVT VT, bool MathUsed) const |

| Try to convert math with an overflow comparison into the corresponding DAG node operation. | |

| virtual bool | aggressivelyPreferBuildVectorSources (EVT VecVT) const |

| virtual bool | shouldConsiderGEPOffsetSplit () const |

| virtual bool | shouldAvoidTransformToShift (EVT VT, unsigned Amount) const |

| Return true if creating a shift of the type by the given amount is not profitable. | |

| virtual bool | shouldFoldSelectWithSingleBitTest (EVT VT, const APInt &AndMask) const |

| virtual bool | shouldKeepZExtForFP16Conv () const |

| Does this target require the clearing of high-order bits in a register passed to the fp16 to fp conversion library function. | |

| virtual bool | shouldConvertFpToSat (unsigned Op, EVT FPVT, EVT VT) const |

| Should we generate fp_to_si_sat and fp_to_ui_sat from type FPVT to type VT from min(max(fptoi)) saturation patterns. | |

| virtual bool | isComplexDeinterleavingSupported () const |

| Does this target support complex deinterleaving. | |

| virtual bool | isComplexDeinterleavingOperationSupported (ComplexDeinterleavingOperation Operation, Type *Ty) const |

| Does this target support complex deinterleaving with the given operation and type. | |

| virtual Value * | createComplexDeinterleavingIR (IRBuilderBase &B, ComplexDeinterleavingOperation OperationType, ComplexDeinterleavingRotation Rotation, Value *InputA, Value *InputB, Value *Accumulator=nullptr) const |

| Create the IR node for the given complex deinterleaving operation. | |

| void | setLibcallName (RTLIB::Libcall Call, const char *Name) |

| Rename the default libcall routine name for the specified libcall. | |

| void | setLibcallName (ArrayRef< RTLIB::Libcall > Calls, const char *Name) |

| const char * | getLibcallName (RTLIB::Libcall Call) const |

| Get the libcall routine name for the specified libcall. | |

| void | setCmpLibcallCC (RTLIB::Libcall Call, ISD::CondCode CC) |

| Override the default CondCode to be used to test the result of the comparison libcall against zero. | |

| ISD::CondCode | getCmpLibcallCC (RTLIB::Libcall Call) const |

| Get the CondCode that's to be used to test the result of the comparison libcall against zero. | |

| void | setLibcallCallingConv (RTLIB::Libcall Call, CallingConv::ID CC) |

| Set the CallingConv that should be used for the specified libcall. | |

| CallingConv::ID | getLibcallCallingConv (RTLIB::Libcall Call) const |

| Get the CallingConv that should be used for the specified libcall. | |

| virtual void | finalizeLowering (MachineFunction &MF) const |

| Execute target specific actions to finalize target lowering. | |

| virtual bool | shouldLocalize (const MachineInstr &MI, const TargetTransformInfo *TTI) const |

Check whether or not MI needs to be moved close to its uses. | |

Helpers for TargetTransformInfo implementations | |

| int | InstructionOpcodeToISD (unsigned Opcode) const |

| Get the ISD node that corresponds to the Instruction class opcode. | |

Helpers for atomic expansion. | |

| unsigned | getMaxAtomicSizeInBitsSupported () const |

| Returns the maximum atomic operation size (in bits) supported by the backend. | |

| unsigned | getMaxDivRemBitWidthSupported () const |

| Returns the size in bits of the maximum div/rem the backend supports. | |

| unsigned | getMaxLargeFPConvertBitWidthSupported () const |

| Returns the size in bits of the maximum larget fp convert the backend supports. | |

| unsigned | getMinCmpXchgSizeInBits () const |

| Returns the size of the smallest cmpxchg or ll/sc instruction the backend supports. | |

| bool | supportsUnalignedAtomics () const |

| Whether the target supports unaligned atomic operations. | |

| virtual bool | shouldInsertFencesForAtomic (const Instruction *I) const |

| Whether AtomicExpandPass should automatically insert fences and reduce ordering for this atomic. | |

| virtual bool | shouldInsertTrailingFenceForAtomicStore (const Instruction *I) const |

| Whether AtomicExpandPass should automatically insert a trailing fence without reducing the ordering for this atomic. | |

| virtual Value * | emitLoadLinked (IRBuilderBase &Builder, Type *ValueTy, Value *Addr, AtomicOrdering Ord) const |

| Perform a load-linked operation on Addr, returning a "Value *" with the corresponding pointee type. | |

| virtual Value * | emitStoreConditional (IRBuilderBase &Builder, Value *Val, Value *Addr, AtomicOrdering Ord) const |

| Perform a store-conditional operation to Addr. | |

| virtual Value * | emitMaskedAtomicRMWIntrinsic (IRBuilderBase &Builder, AtomicRMWInst *AI, Value *AlignedAddr, Value *Incr, Value *Mask, Value *ShiftAmt, AtomicOrdering Ord) const |

| Perform a masked atomicrmw using a target-specific intrinsic. | |

| virtual void | emitExpandAtomicRMW (AtomicRMWInst *AI) const |

| Perform a atomicrmw expansion using a target-specific way. | |

| virtual void | emitBitTestAtomicRMWIntrinsic (AtomicRMWInst *AI) const |

| Perform a bit test atomicrmw using a target-specific intrinsic. | |

| virtual void | emitCmpArithAtomicRMWIntrinsic (AtomicRMWInst *AI) const |

| Perform a atomicrmw which the result is only used by comparison, using a target-specific intrinsic. | |

| virtual Value * | emitMaskedAtomicCmpXchgIntrinsic (IRBuilderBase &Builder, AtomicCmpXchgInst *CI, Value *AlignedAddr, Value *CmpVal, Value *NewVal, Value *Mask, AtomicOrdering Ord) const |

| Perform a masked cmpxchg using a target-specific intrinsic. | |

KCFI check lowering. | |

| virtual MachineInstr * | EmitKCFICheck (MachineBasicBlock &MBB, MachineBasicBlock::instr_iterator &MBBI, const TargetInstrInfo *TII) const |

| virtual Instruction * | emitLeadingFence (IRBuilderBase &Builder, Instruction *Inst, AtomicOrdering Ord) const |

| Inserts in the IR a target-specific intrinsic specifying a fence. | |

| virtual Instruction * | emitTrailingFence (IRBuilderBase &Builder, Instruction *Inst, AtomicOrdering Ord) const |

Static Public Member Functions | |

| static ISD::NodeType | getExtendForContent (BooleanContent Content) |

Protected Member Functions | |

| void | initActions () |

| Initialize all of the actions to default values. | |

| Value * | getDefaultSafeStackPointerLocation (IRBuilderBase &IRB, bool UseTLS) const |

| void | setBooleanContents (BooleanContent Ty) |

| Specify how the target extends the result of integer and floating point boolean values from i1 to a wider type. | |

| void | setBooleanContents (BooleanContent IntTy, BooleanContent FloatTy) |

| Specify how the target extends the result of integer and floating point boolean values from i1 to a wider type. | |

| void | setBooleanVectorContents (BooleanContent Ty) |

| Specify how the target extends the result of a vector boolean value from a vector of i1 to a wider type. | |

| void | setSchedulingPreference (Sched::Preference Pref) |

| Specify the target scheduling preference. | |

| void | setMinimumJumpTableEntries (unsigned Val) |

| Indicate the minimum number of blocks to generate jump tables. | |

| void | setMaximumJumpTableSize (unsigned) |

| Indicate the maximum number of entries in jump tables. | |

| void | setStackPointerRegisterToSaveRestore (Register R) |

| If set to a physical register, this specifies the register that llvm.savestack/llvm.restorestack should save and restore. | |

| void | setHasMultipleConditionRegisters (bool hasManyRegs=true) |

| Tells the code generator that the target has multiple (allocatable) condition registers that can be used to store the results of comparisons for use by selects and conditional branches. | |

| void | setHasExtractBitsInsn (bool hasExtractInsn=true) |

| Tells the code generator that the target has BitExtract instructions. | |

| void | setJumpIsExpensive (bool isExpensive=true) |

| Tells the code generator not to expand logic operations on comparison predicates into separate sequences that increase the amount of flow control. | |

| void | addBypassSlowDiv (unsigned int SlowBitWidth, unsigned int FastBitWidth) |

| Tells the code generator which bitwidths to bypass. | |

| void | addRegisterClass (MVT VT, const TargetRegisterClass *RC) |

| Add the specified register class as an available regclass for the specified value type. | |

| virtual std::pair< const TargetRegisterClass *, uint8_t > | findRepresentativeClass (const TargetRegisterInfo *TRI, MVT VT) const |

| Return the largest legal super-reg register class of the register class for the specified type and its associated "cost". | |

| void | computeRegisterProperties (const TargetRegisterInfo *TRI) |

| Once all of the register classes are added, this allows us to compute derived properties we expose. | |

| void | setOperationAction (unsigned Op, MVT VT, LegalizeAction Action) |

| Indicate that the specified operation does not work with the specified type and indicate what to do about it. | |

| void | setOperationAction (ArrayRef< unsigned > Ops, MVT VT, LegalizeAction Action) |

| void | setOperationAction (ArrayRef< unsigned > Ops, ArrayRef< MVT > VTs, LegalizeAction Action) |

| void | setLoadExtAction (unsigned ExtType, MVT ValVT, MVT MemVT, LegalizeAction Action) |

| Indicate that the specified load with extension does not work with the specified type and indicate what to do about it. | |

| void | setLoadExtAction (ArrayRef< unsigned > ExtTypes, MVT ValVT, MVT MemVT, LegalizeAction Action) |

| void | setLoadExtAction (ArrayRef< unsigned > ExtTypes, MVT ValVT, ArrayRef< MVT > MemVTs, LegalizeAction Action) |

| void | setAtomicLoadExtAction (unsigned ExtType, MVT ValVT, MVT MemVT, LegalizeAction Action) |

| Let target indicate that an extending atomic load of the specified type is legal. | |

| void | setAtomicLoadExtAction (ArrayRef< unsigned > ExtTypes, MVT ValVT, MVT MemVT, LegalizeAction Action) |

| void | setAtomicLoadExtAction (ArrayRef< unsigned > ExtTypes, MVT ValVT, ArrayRef< MVT > MemVTs, LegalizeAction Action) |

| void | setTruncStoreAction (MVT ValVT, MVT MemVT, LegalizeAction Action) |

| Indicate that the specified truncating store does not work with the specified type and indicate what to do about it. | |

| void | setIndexedLoadAction (ArrayRef< unsigned > IdxModes, MVT VT, LegalizeAction Action) |

| Indicate that the specified indexed load does or does not work with the specified type and indicate what to do abort it. | |

| void | setIndexedLoadAction (ArrayRef< unsigned > IdxModes, ArrayRef< MVT > VTs, LegalizeAction Action) |

| void | setIndexedStoreAction (ArrayRef< unsigned > IdxModes, MVT VT, LegalizeAction Action) |

| Indicate that the specified indexed store does or does not work with the specified type and indicate what to do about it. | |

| void | setIndexedStoreAction (ArrayRef< unsigned > IdxModes, ArrayRef< MVT > VTs, LegalizeAction Action) |

| void | setIndexedMaskedLoadAction (unsigned IdxMode, MVT VT, LegalizeAction Action) |

| Indicate that the specified indexed masked load does or does not work with the specified type and indicate what to do about it. | |

| void | setIndexedMaskedStoreAction (unsigned IdxMode, MVT VT, LegalizeAction Action) |

| Indicate that the specified indexed masked store does or does not work with the specified type and indicate what to do about it. | |

| void | setCondCodeAction (ArrayRef< ISD::CondCode > CCs, MVT VT, LegalizeAction Action) |

| Indicate that the specified condition code is or isn't supported on the target and indicate what to do about it. | |

| void | setCondCodeAction (ArrayRef< ISD::CondCode > CCs, ArrayRef< MVT > VTs, LegalizeAction Action) |

| void | AddPromotedToType (unsigned Opc, MVT OrigVT, MVT DestVT) |

| If Opc/OrigVT is specified as being promoted, the promotion code defaults to trying a larger integer/fp until it can find one that works. | |

| void | setOperationPromotedToType (unsigned Opc, MVT OrigVT, MVT DestVT) |

| Convenience method to set an operation to Promote and specify the type in a single call. | |

| void | setOperationPromotedToType (ArrayRef< unsigned > Ops, MVT OrigVT, MVT DestVT) |

| void | setTargetDAGCombine (ArrayRef< ISD::NodeType > NTs) |

| Targets should invoke this method for each target independent node that they want to provide a custom DAG combiner for by implementing the PerformDAGCombine virtual method. | |

| void | setMinFunctionAlignment (Align Alignment) |

| Set the target's minimum function alignment. | |

| void | setPrefFunctionAlignment (Align Alignment) |

| Set the target's preferred function alignment. | |

| void | setPrefLoopAlignment (Align Alignment) |

| Set the target's preferred loop alignment. | |

| void | setMaxBytesForAlignment (unsigned MaxBytes) |

| void | setMinStackArgumentAlignment (Align Alignment) |

| Set the minimum stack alignment of an argument. | |

| void | setMaxAtomicSizeInBitsSupported (unsigned SizeInBits) |

| Set the maximum atomic operation size supported by the backend. | |

| void | setMaxDivRemBitWidthSupported (unsigned SizeInBits) |

| Set the size in bits of the maximum div/rem the backend supports. | |

| void | setMaxLargeFPConvertBitWidthSupported (unsigned SizeInBits) |

| Set the size in bits of the maximum fp convert the backend supports. | |

| void | setMinCmpXchgSizeInBits (unsigned SizeInBits) |

| Sets the minimum cmpxchg or ll/sc size supported by the backend. | |

| void | setSupportsUnalignedAtomics (bool UnalignedSupported) |

| Sets whether unaligned atomic operations are supported. | |

| virtual bool | isExtFreeImpl (const Instruction *I) const |

Return true if the extension represented by I is free. | |

| bool | isLegalRC (const TargetRegisterInfo &TRI, const TargetRegisterClass &RC) const |

| Return true if the value types that can be represented by the specified register class are all legal. | |

| MachineBasicBlock * | emitPatchPoint (MachineInstr &MI, MachineBasicBlock *MBB) const |

| Replace/modify any TargetFrameIndex operands with a targte-dependent sequence of memory operands that is recognized by PrologEpilogInserter. | |

Protected Attributes | |

| unsigned | GatherAllAliasesMaxDepth |

| Depth that GatherAllAliases should continue looking for chain dependencies when trying to find a more preferable chain. | |

| unsigned | MaxStoresPerMemset |

| Specify maximum number of store instructions per memset call. | |

| unsigned | MaxStoresPerMemsetOptSize |

| Likewise for functions with the OptSize attribute. | |

| unsigned | MaxStoresPerMemcpy |

| Specify maximum number of store instructions per memcpy call. | |

| unsigned | MaxStoresPerMemcpyOptSize |

| Likewise for functions with the OptSize attribute. | |

| unsigned | MaxGluedStoresPerMemcpy = 0 |

| Specify max number of store instructions to glue in inlined memcpy. | |

| unsigned | MaxLoadsPerMemcmp |

| Specify maximum number of load instructions per memcmp call. | |

| unsigned | MaxLoadsPerMemcmpOptSize |

| Likewise for functions with the OptSize attribute. | |

| unsigned | MaxStoresPerMemmove |

| Specify maximum number of store instructions per memmove call. | |

| unsigned | MaxStoresPerMemmoveOptSize |

| Likewise for functions with the OptSize attribute. | |

| bool | PredictableSelectIsExpensive |

| Tells the code generator that select is more expensive than a branch if the branch is usually predicted right. | |

| bool | EnableExtLdPromotion |

| bool | IsStrictFPEnabled |

Detailed Description

This base class for TargetLowering contains the SelectionDAG-independent parts that can be used from the rest of CodeGen.

Definition at line 193 of file TargetLowering.h.

Member Typedef Documentation

◆ ArgListTy

| using llvm::TargetLoweringBase::ArgListTy = std::vector<ArgListEntry> |

Definition at line 325 of file TargetLowering.h.

◆ LegalizeKind

| using llvm::TargetLoweringBase::LegalizeKind = std::pair<LegalizeTypeAction, EVT> |

LegalizeKind holds the legalization kind that needs to happen to EVT in order to type-legalize it.

Definition at line 229 of file TargetLowering.h.

Member Enumeration Documentation

◆ AndOrSETCCFoldKind

| enum llvm::TargetLoweringBase::AndOrSETCCFoldKind : uint8_t |

Enum of different potentially desirable ways to fold (and/or (setcc ...), (setcc ...)).

| Enumerator | |

|---|---|

| None | |

| AddAnd | |

| NotAnd | |

| ABS | |

Definition at line 288 of file TargetLowering.h.

◆ AtomicExpansionKind

|

strong |

Enum that specifies what an atomic load/AtomicRMWInst is expanded to, if at all.

Exists because different targets have different levels of support for these atomic instructions, and also have different options w.r.t. what they should expand to.

| Enumerator | |

|---|---|

| None | |

| CastToInteger | |

| LLSC | |

| LLOnly | |

| CmpXChg | |

| MaskedIntrinsic | |

| BitTestIntrinsic | |

| CmpArithIntrinsic | |

| Expand | |

| NotAtomic | |

Definition at line 251 of file TargetLowering.h.

◆ BooleanContent

Enum that describes how the target represents true/false values.

| Enumerator | |

|---|---|

| UndefinedBooleanContent | |

| ZeroOrOneBooleanContent | |

| ZeroOrNegativeOneBooleanContent | |

Definition at line 232 of file TargetLowering.h.

◆ LegalizeAction

| enum llvm::TargetLoweringBase::LegalizeAction : uint8_t |

This enum indicates whether operations are valid for a target, and if not, what action should be used to make them valid.

| Enumerator | |

|---|---|

| Legal | |

| Promote | |

| Expand | |

| LibCall | |

| Custom | |

Definition at line 197 of file TargetLowering.h.

◆ LegalizeTypeAction

| enum llvm::TargetLoweringBase::LegalizeTypeAction : uint8_t |

This enum indicates whether a types are legal for a target, and if not, what action should be used to make them valid.

Definition at line 207 of file TargetLowering.h.

◆ MulExpansionKind

|

strong |

Enum that specifies when a multiplication should be expanded.

| Enumerator | |

|---|---|

| Always | |

| OnlyLegalOrCustom | |

Definition at line 273 of file TargetLowering.h.

◆ NegatibleCost

|

strong |

Enum that specifies when a float negation is beneficial.

| Enumerator | |

|---|---|

| Cheaper | |

| Neutral | |

| Expensive | |

Definition at line 280 of file TargetLowering.h.

◆ ReciprocalEstimate

| enum llvm::TargetLoweringBase::ReciprocalEstimate : int |

Reciprocal estimate status values used by the functions below.

| Enumerator | |

|---|---|

| Unspecified | |

| Disabled | |

| Enabled | |

Definition at line 553 of file TargetLowering.h.

◆ SelectSupportKind

Enum that describes what type of support for selects the target has.

| Enumerator | |

|---|---|

| ScalarValSelect | |

| ScalarCondVectorVal | |

| VectorMaskSelect | |

Definition at line 239 of file TargetLowering.h.

◆ ShiftLegalizationStrategy

|

strong |

Return the preferred strategy to legalize tihs SHIFT instruction, with ExpansionFactor being the recursion depth - how many expansion needed.

| Enumerator | |

|---|---|

| ExpandToParts | |

| ExpandThroughStack | |

| LowerToLibcall | |

Definition at line 1057 of file TargetLowering.h.

Constructor & Destructor Documentation

◆ TargetLoweringBase() [1/2]

|

explicit |

NOTE: The TargetMachine owns TLOF.

Definition at line 776 of file TargetLoweringBase.cpp.

References DisableStrictNodeMutation, EnableExtLdPromotion, GatherAllAliasesMaxDepth, llvm::TargetMachine::getTargetTriple(), llvm::Sched::ILP, initActions(), InitCmpLibcallCCs(), IsStrictFPEnabled, JumpIsExpensiveOverride, llvm::IntegerType::MAX_INT_BITS, MaxGluedStoresPerMemcpy, MaxLoadsPerMemcmp, MaxLoadsPerMemcmpOptSize, MaxStoresPerMemcpy, MaxStoresPerMemcpyOptSize, MaxStoresPerMemmove, MaxStoresPerMemmoveOptSize, MaxStoresPerMemset, MaxStoresPerMemsetOptSize, PredictableSelectIsExpensive, and UndefinedBooleanContent.

◆ TargetLoweringBase() [2/2]

|

delete |

◆ ~TargetLoweringBase()

|

virtualdefault |

Member Function Documentation

◆ addBypassSlowDiv()

|

inlineprotected |

Tells the code generator which bitwidths to bypass.

Definition at line 2507 of file TargetLowering.h.

Referenced by llvm::AMDGPUTargetLowering::AMDGPUTargetLowering(), llvm::NVPTXTargetLowering::NVPTXTargetLowering(), and llvm::X86TargetLowering::X86TargetLowering().

◆ AddPromotedToType()

|

inlineprotected |

If Opc/OrigVT is specified as being promoted, the promotion code defaults to trying a larger integer/fp until it can find one that works.

If that default is insufficient, this method can be used by the target to override the default.

Definition at line 2679 of file TargetLowering.h.

References llvm::MVT::SimpleTy.

Referenced by llvm::AMDGPUTargetLowering::AMDGPUTargetLowering(), llvm::HexagonTargetLowering::HexagonTargetLowering(), initActions(), llvm::MipsTargetLowering::MipsTargetLowering(), llvm::NVPTXTargetLowering::NVPTXTargetLowering(), llvm::PPCTargetLowering::PPCTargetLowering(), setOperationPromotedToType(), and llvm::SITargetLowering::SITargetLowering().

◆ addRegisterClass()

|

inlineprotected |

Add the specified register class as an available regclass for the specified value type.

This indicates the selector can handle values of that class natively.

Definition at line 2514 of file TargetLowering.h.

References assert(), and llvm::MVT::SimpleTy.

Referenced by llvm::AArch64TargetLowering::AArch64TargetLowering(), llvm::MipsSETargetLowering::addMSAFloatType(), llvm::MipsSETargetLowering::addMSAIntType(), llvm::ARCTargetLowering::ARCTargetLowering(), llvm::ARMTargetLowering::ARMTargetLowering(), llvm::AVRTargetLowering::AVRTargetLowering(), llvm::BPFTargetLowering::BPFTargetLowering(), llvm::CSKYTargetLowering::CSKYTargetLowering(), llvm::HexagonTargetLowering::HexagonTargetLowering(), llvm::LanaiTargetLowering::LanaiTargetLowering(), llvm::LoongArchTargetLowering::LoongArchTargetLowering(), llvm::M68kTargetLowering::M68kTargetLowering(), llvm::Mips16TargetLowering::Mips16TargetLowering(), llvm::MipsSETargetLowering::MipsSETargetLowering(), llvm::MSP430TargetLowering::MSP430TargetLowering(), llvm::NVPTXTargetLowering::NVPTXTargetLowering(), llvm::PPCTargetLowering::PPCTargetLowering(), llvm::R600TargetLowering::R600TargetLowering(), llvm::RISCVTargetLowering::RISCVTargetLowering(), llvm::SITargetLowering::SITargetLowering(), llvm::SparcTargetLowering::SparcTargetLowering(), llvm::SystemZTargetLowering::SystemZTargetLowering(), llvm::WebAssemblyTargetLowering::WebAssemblyTargetLowering(), llvm::X86TargetLowering::X86TargetLowering(), llvm::XCoreTargetLowering::XCoreTargetLowering(), and llvm::XtensaTargetLowering::XtensaTargetLowering().

◆ addressingModeSupportsTLS()

|

inlinevirtual |

Returns true if the targets addressing mode can target thread local storage (TLS).

Reimplemented in llvm::X86TargetLowering.

Definition at line 2810 of file TargetLowering.h.

◆ aggressivelyPreferBuildVectorSources()

|

inlinevirtual |

Reimplemented in llvm::AMDGPUTargetLowering, and llvm::NVPTXTargetLowering.

Definition at line 3356 of file TargetLowering.h.

◆ alignLoopsWithOptSize()

|

inlinevirtual |

Should loops be aligned even when the function is marked OptSize (but not MinSize).

Reimplemented in llvm::ARMTargetLowering.

Definition at line 2036 of file TargetLowering.h.

◆ allowsMemoryAccess() [1/3]

| bool TargetLoweringBase::allowsMemoryAccess | ( | LLVMContext & | Context, |

| const DataLayout & | DL, | ||

| EVT | VT, | ||

| const MachineMemOperand & | MMO, | ||

| unsigned * | Fast = nullptr |

||

| ) | const |

Return true if the target supports a memory access of this type for the given MachineMemOperand.

If the access is allowed, the optional final parameter returns the relative access speed (as defined by the target).

Definition at line 1869 of file TargetLoweringBase.cpp.

References allowsMemoryAccess(), Context, DL, llvm::CallingConv::Fast, llvm::MachineMemOperand::getAddrSpace(), llvm::MachineMemOperand::getAlign(), and llvm::MachineMemOperand::getFlags().

◆ allowsMemoryAccess() [2/3]

|

virtual |

Return true if the target supports a memory access of this type for the given address space and alignment.